Memory cell suitable for dram memory

A memory cell and memory technology, applied in the direction of capacitors, electrical components, electric solid devices, etc., can solve the problems of increased danger of junction leakage, problematic process temperature, negative memory effect, etc., to reduce the danger of junction leakage, manufacturing Low cost and reduced temperature problems

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

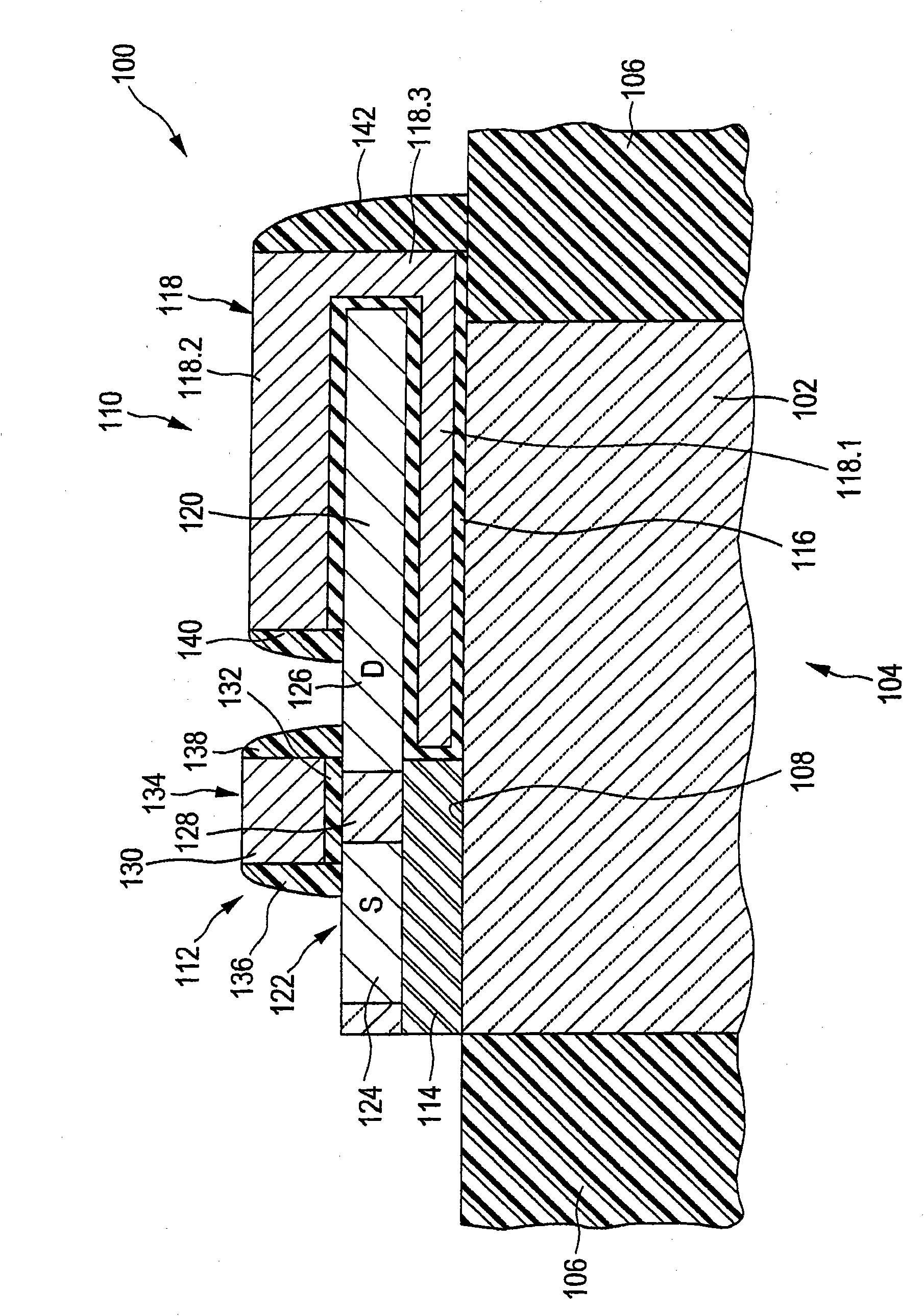

[0061] figure 1 A schematic cross-sectional view of a memory cell 100 according to a first embodiment of the invention is shown. The memory cell 100 is disposed on a silicon substrate 102 . On a silicon substrate, an active semiconductor region 104 is laterally bounded by shallow trench isolation (STI) regions 106, as is well known in CMOS technology. figure 1 Only a portion of substrate 102 is shown. The portion includes an active semiconductor region having a substantially planar surface 108 . The substrate 102 is only shown to a depth that does not exceed the depth of the shallow trench isolation regions. Notice, figure 1 The illustration of the memory cells in is purely schematic and is not intended to fully reflect geometrical proportions.

[0062] On the active semiconductor region 104, active elements of the memory cell 100 are arranged. That is, the memory capacitor 110 and the control MOSFET 112 are provided on the active semiconductor region. Note that the sur...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More