Method for forming shallow trench isolation structure

A technology of isolation structures and shallow trenches, which is applied in the fields of electrical components, semiconductor/solid-state device manufacturing, circuits, etc., can solve the problems of low performance of semiconductor devices and affecting the electrical characteristics of semiconductor devices, etc. Good corrosion performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

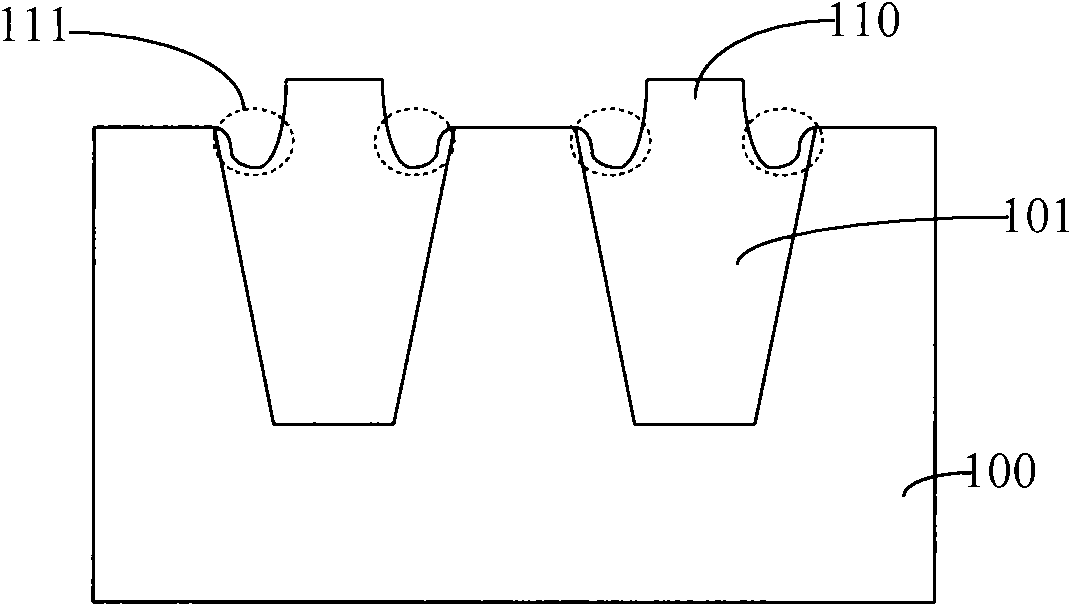

[0014] It can be seen from the background technology that in the existing shallow trench isolation structure, the isolation dielectric layer is located in a relatively loose area adjacent to the active region, which is corroded by the chemical reagents in the semiconductor device formation process, resulting in a gap between the shallow trench and the active region. The adjacent area will form a downward concave shape, called the side ditch (Divot), please refer to figure 1 , figure 1 The isolation shallow trench formed for the prior art includes a substrate 100; forming a shallow trench 101 in the substrate 100; a dielectric layer 110 filling the shallow trench; forming a side trench 111 in the dielectric layer, The semiconductor device formed by using the above-mentioned isolated shallow trenches is prone to generate parasitic current, thereby affecting the electrical characteristics of the semiconductor device, and the existence of side trenches will lead to the formation o...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More