Preparation method of Through-Silicon-Via back coupling end

A technology for through-silicon vias and connection ends, which is applied in the field of preparation of back connection ends of through-silicon vias. Implementation and Yield Effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

preparation example Construction

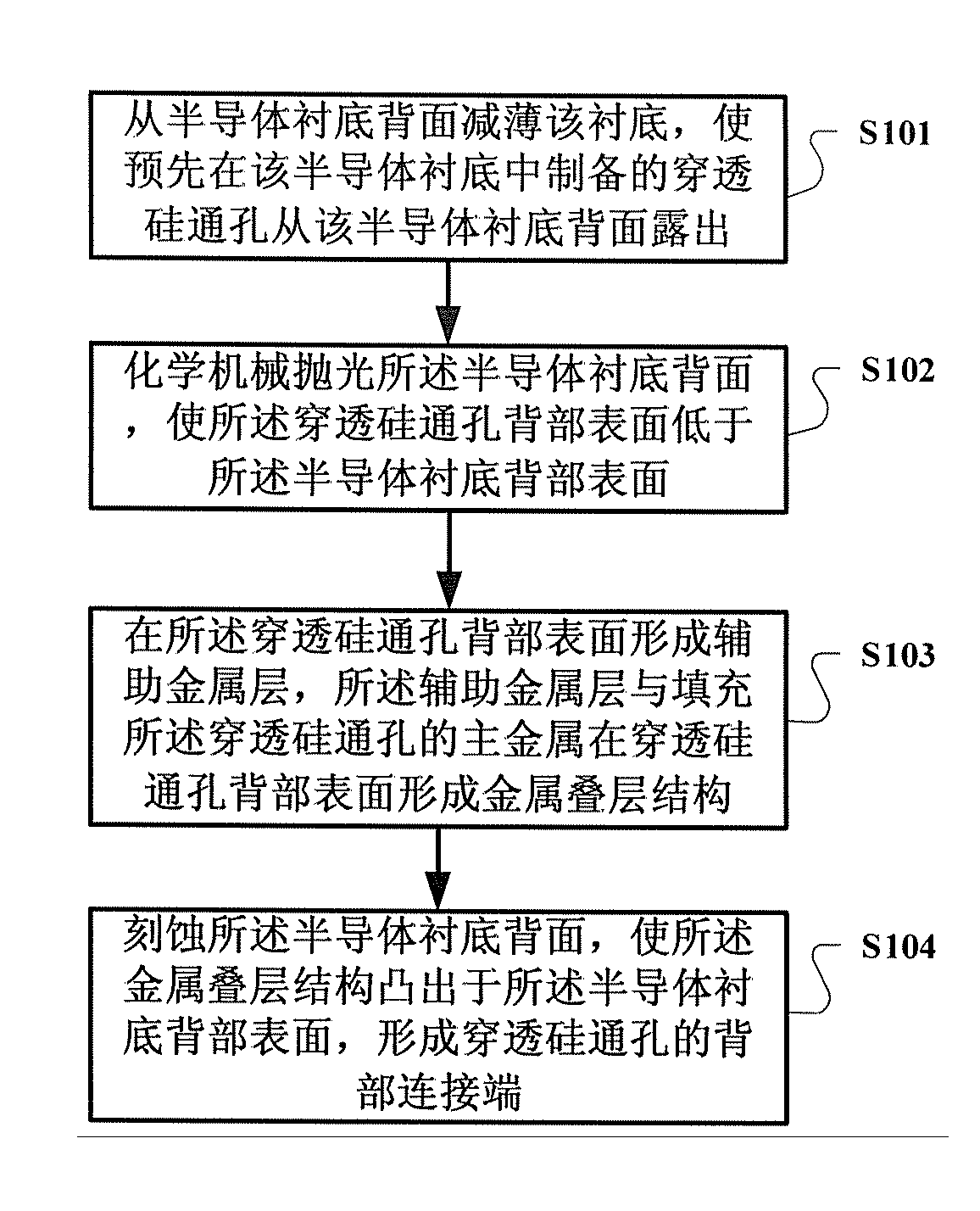

[0035] Such as figure 1 as shown, figure 1 It is a flowchart of a method for preparing the back connection end of a TSV provided by the present invention, and the method includes:

[0036] Step S101, thinning the semiconductor substrate from the back of the semiconductor substrate, so that the TSVs prepared in the semiconductor substrate in advance are exposed from the back of the semiconductor substrate;

[0037] Step S102, chemical mechanical polishing the back surface of the semiconductor substrate, so that the back surface of the TSV is lower than the back surface of the semiconductor substrate;

[0038] Step S103, forming an auxiliary metal layer on the back surface of the TSV, the auxiliary metal layer and the main metal filling the TSV form a metal stack structure on the back surface of the TSV;

[0039] Step S104, etching the back surface of the semiconductor substrate to make the metal stacked structure protrude from the back surface of the semiconductor substrate t...

Embodiment

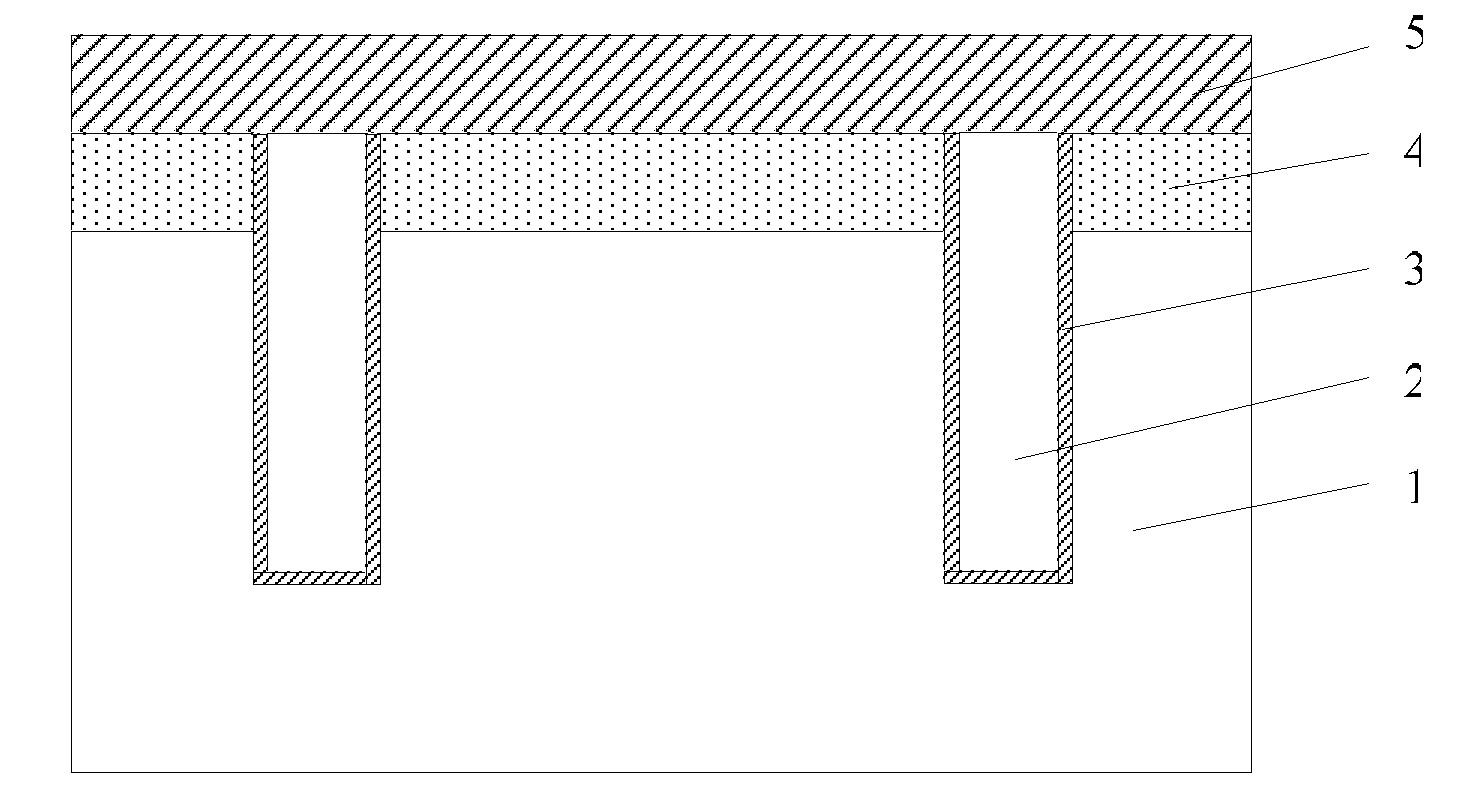

[0042] This embodiment will take the complete preparation process of the back connection end of the TSV as an example for illustration. The semiconductor substrate used in this embodiment is as figure 2 shown. The through-silicon via has been prepared on the semiconductor substrate 1, and the material for filling the through-silicon via includes the main metal 2 and the sidewall isolation layer material 3, and the semiconductor substrate 1 is also completed The processing of the semiconductor device layer 4 and the interconnection layer 5 is completed. The main metal is copper or tungsten, and the isolation layer material is one or more combinations of the following materials: silicon oxide, silicon nitride, titanium, tantalum, titanium nitride, tantalum nitride, ruthenium. The subsequent preparation of the back connection end of the TSV includes the following steps:

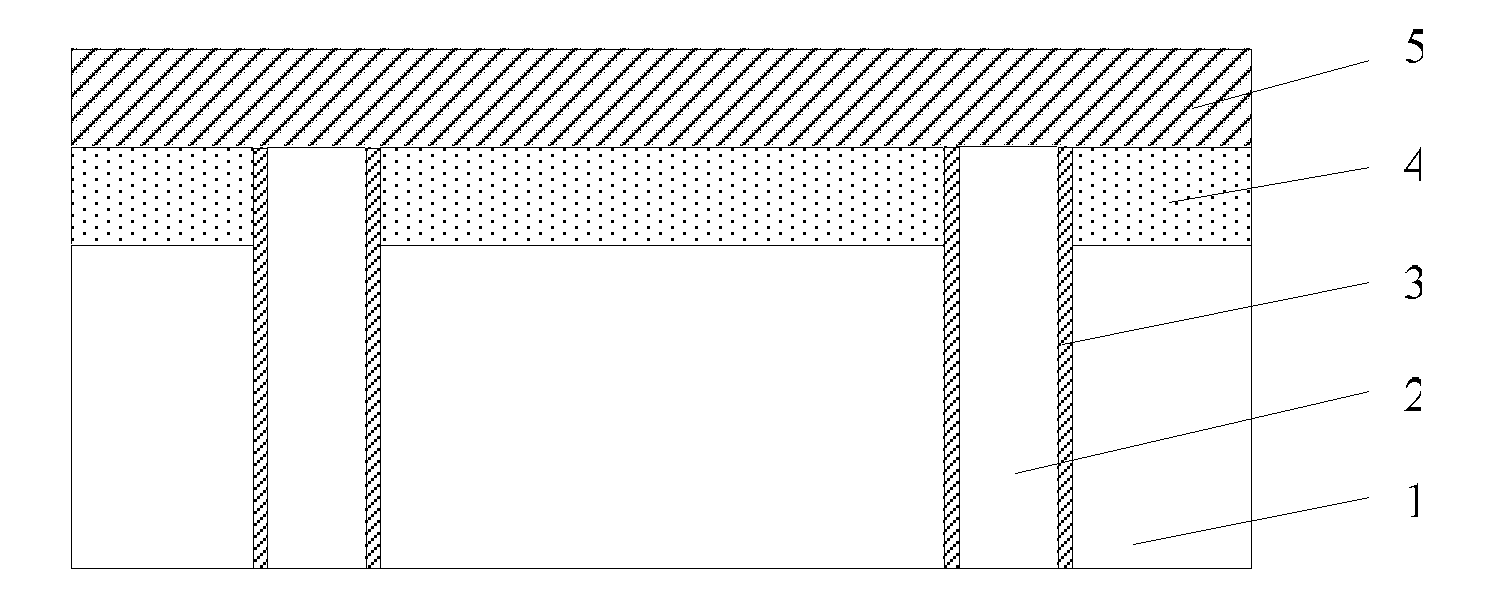

[0043] Step 1: Thinning the semiconductor substrate 1 on the back side, so that the TSV (combination of 2...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More