Field programmable gate array (FPGA) logic module debugging and data acquisition method based on PicoBlaze embedded soft core processor

A soft-core processor and data acquisition technology, applied in the fields of debugging, FPGA teaching, and logic circuit verification, to achieve the effect of simple and easy method, flexible use, good scalability and real-time performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0025] The present invention will be described in further detail below in conjunction with the accompanying drawings and specific examples.

[0026] In FPGA-based SoC design, it is often necessary to reuse the designed logic circuit (such as IP core). The traditional design method is to add the source code of the existing logic module to the project. After the synthesis is passed, use the software simulation Verify that the system can work normally, and then burn it into the FPGA for verification. The disadvantage of using this method is that if the software simulation fails to run normally on the FPGA, it will be difficult to determine the cause of the error. In addition, because the internal signals of the device cannot be collected from the hardware in real time, it is difficult to observe on the hardware. and debug.

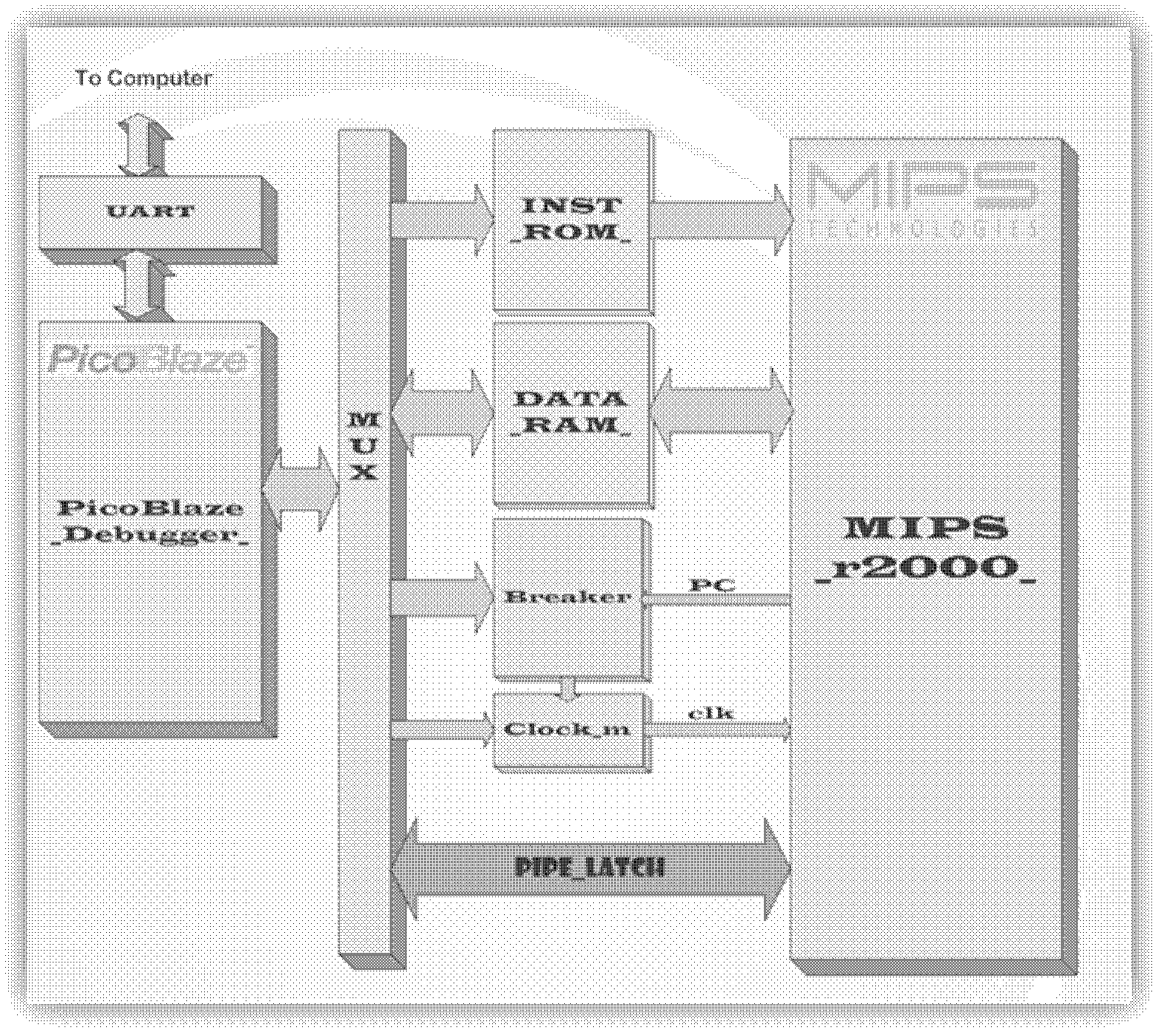

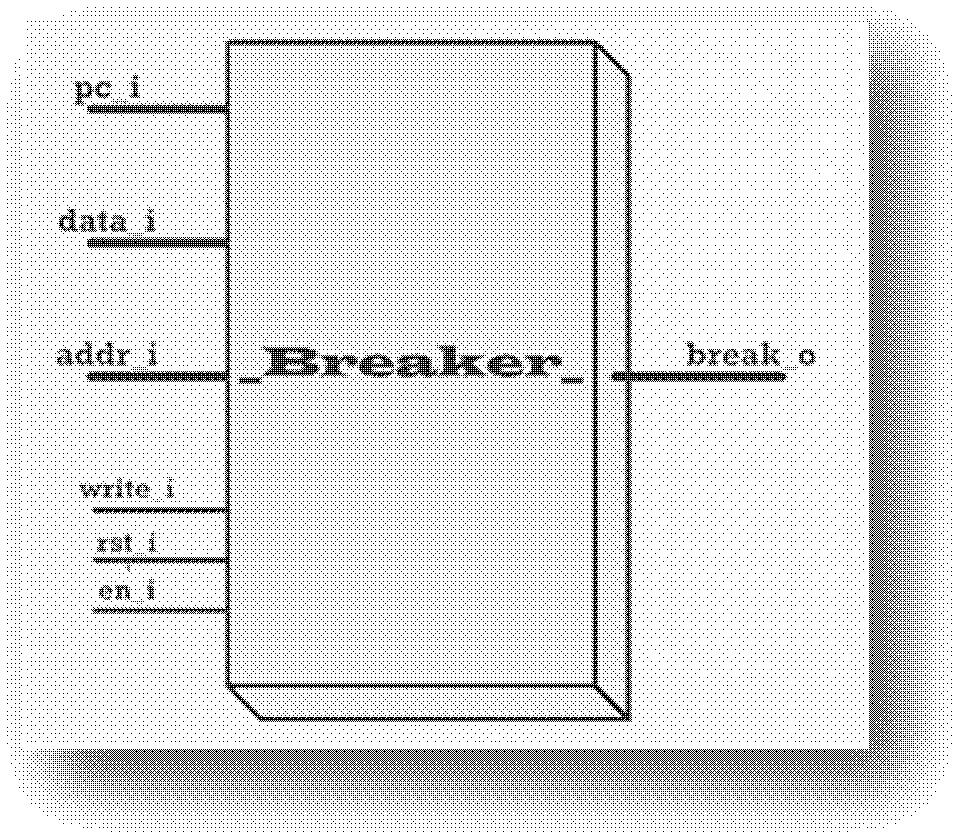

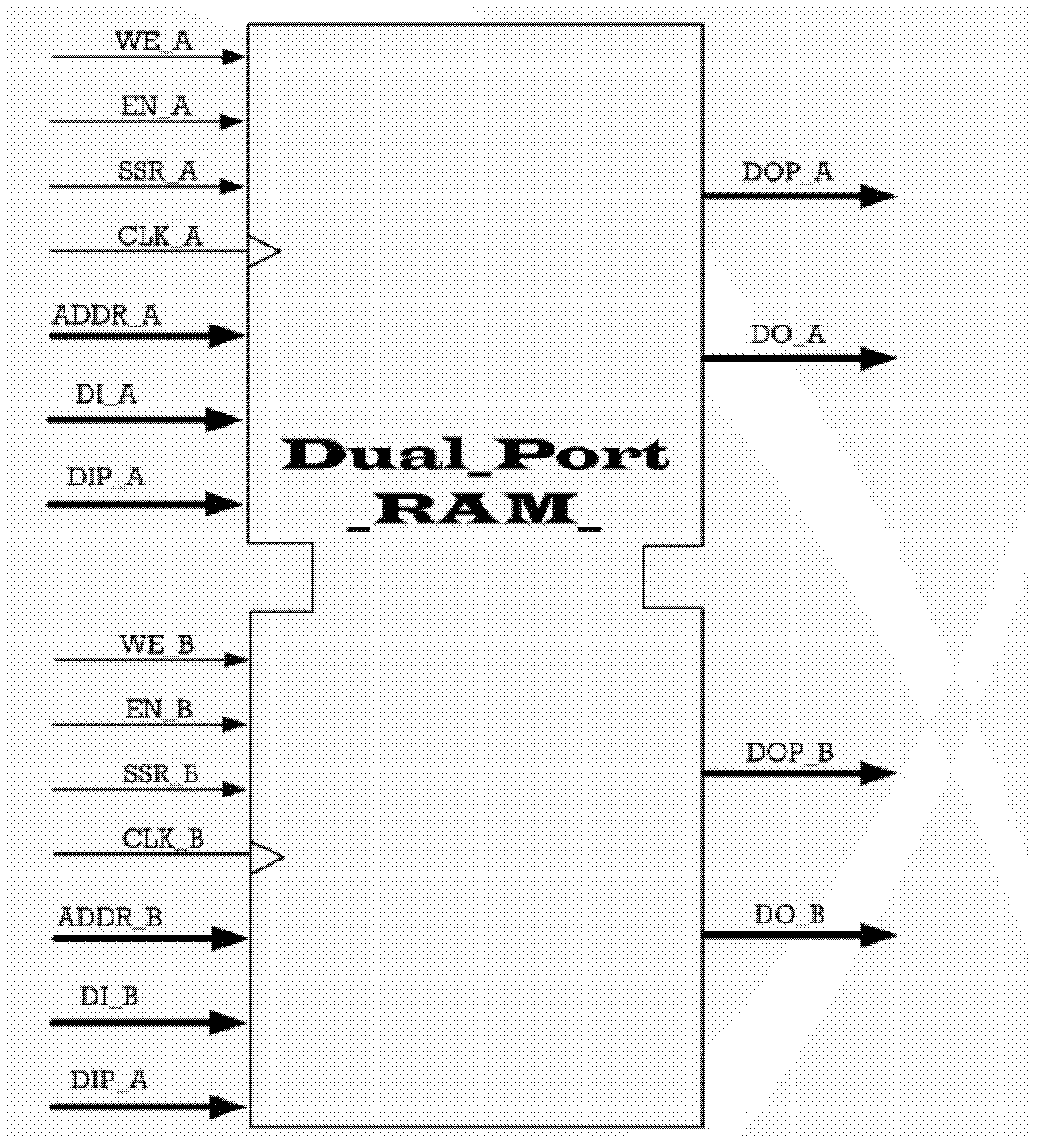

[0027] The present invention is aimed at above-mentioned problem, has added PicoBlaze microprocessor and corresponding control module in the basis of origin...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More