ESD (Electro Spark Detector) power clamping circuit

A technology of clamping circuit and power supply, which is applied in the direction of circuit devices, emergency protection circuit devices, emergency protection circuit devices for limiting overcurrent/overvoltage, etc., to avoid false triggering and reduce the layout area.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

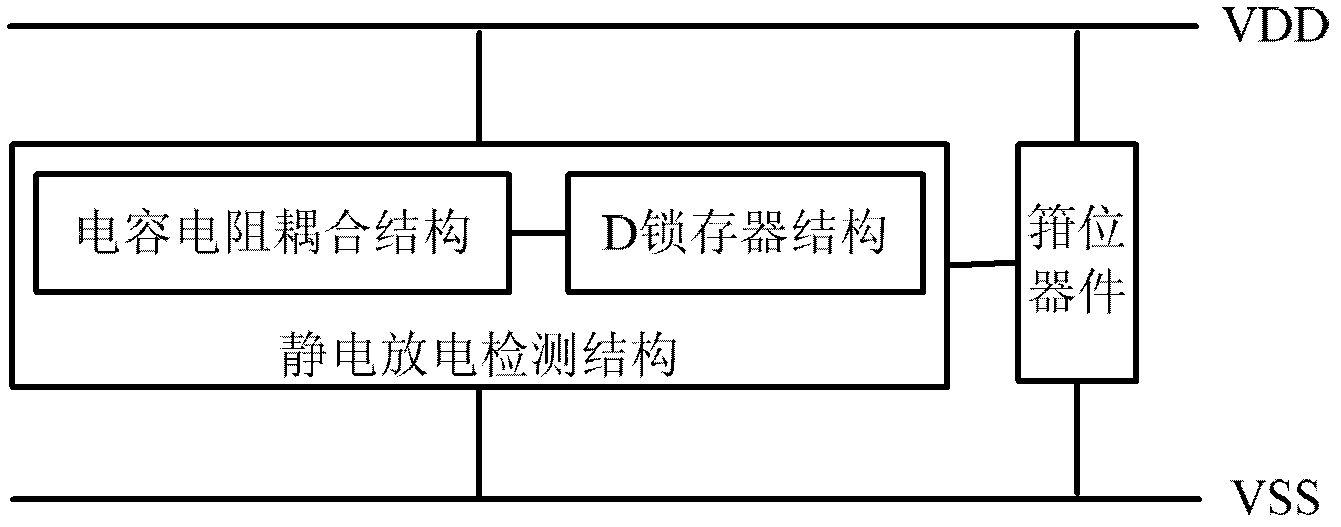

[0040] Such as Figure 4 As shown, the clamping device in this embodiment is an NMOS transistor 60 .

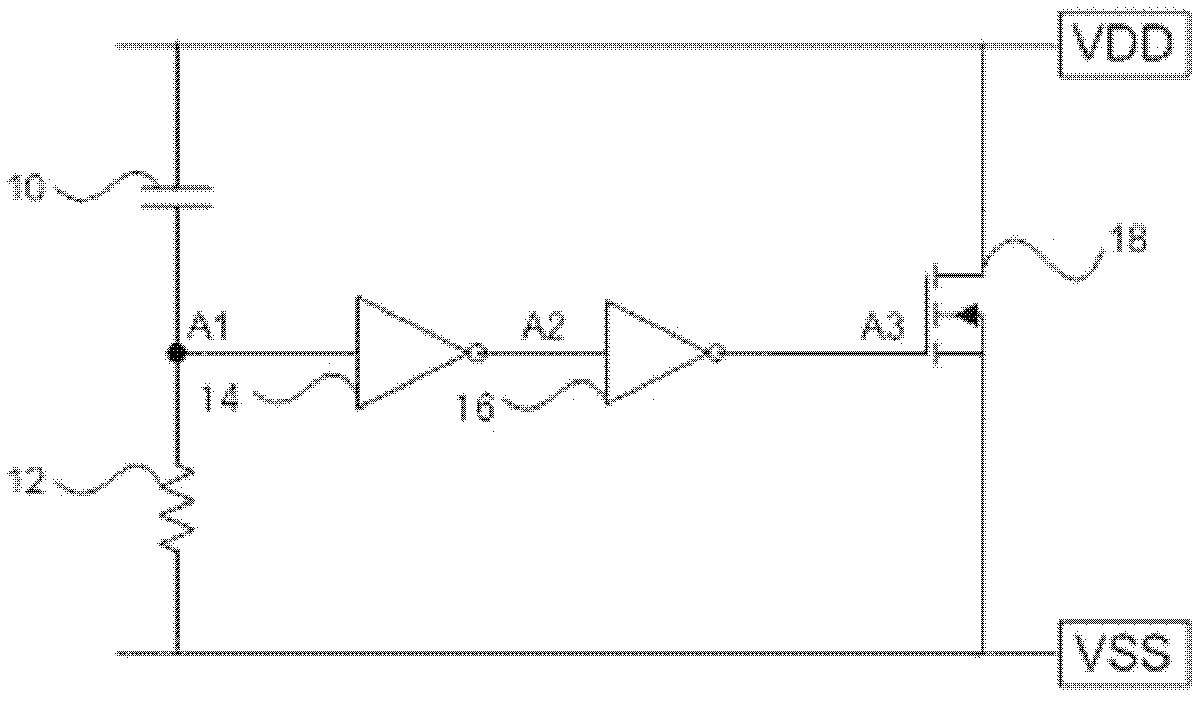

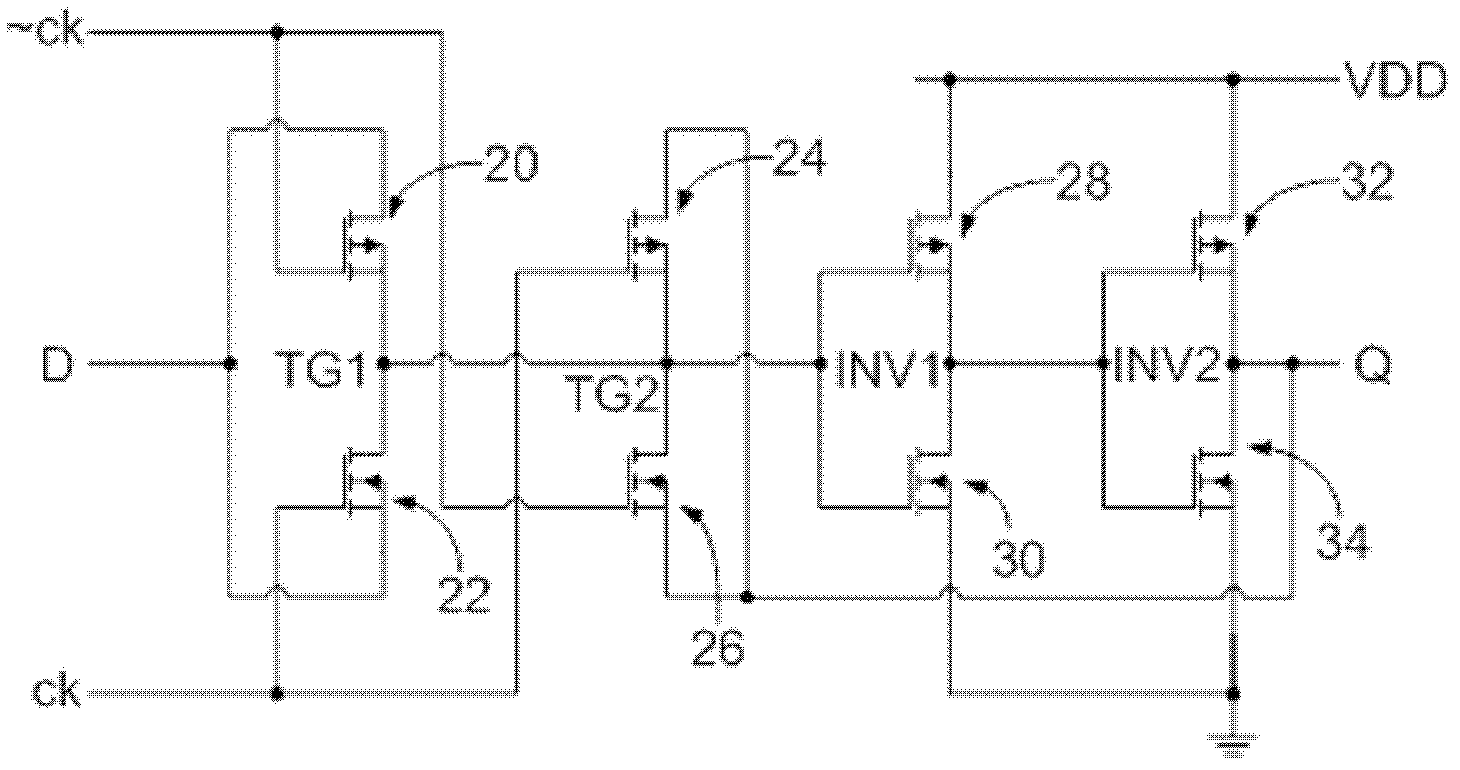

[0041] The D latch structure includes: a first inverter 44, a first CMOS transmission gate TG3, a second CMOS transmission gate TG4, a second inverter 54, a third inverter 56, and a third NMOS transistor 58; The input terminal of an inverter 44 is connected to the connection point C1 of the capacitor 40 and the resistor 42 (the connection point C1 outputs a detection voltage, which is used as the clock signal of the D latch structure, that is figure 2 ck signal in); the two gates of the first CMOS transmission gate TG3 are respectively connected to the input terminal and the output terminal of the first inverter 44 (the complementary signal of the output node C2 output clock signal, namely figure 2 ~ck signal in ), the input control signals are the voltages of nodes C1 and C2 respectively, the input of the first CMOS transmission gate TG3 is connected to the power supply p...

Embodiment 2

[0052]The ESD power supply clamping circuit of this embodiment is a simplification of the circuit of Embodiment 1. Since the input of the D latch structure is connected to a constant high level, the first CMOS transmission gate TG3 can be simplified into an NMOS transmission gate; at the same time, the NMOS transistors in the first inverter 44 and the second CMOS transmission gate TG4 are removed, Only the PMOS transistors in the second CMOS transmission gate TG4 remain. This simplification process does not affect the realization of circuit functions. The HSPICE simulation proves that the function of the circuit after simplification is basically the same as that before simplification.

[0053] Such as Figure 5 As shown, the clamping device of this embodiment is an NMOS transistor 84, and the D latch structure includes: a first NMOS transistor 74, a first PMOS transistor 76, a second NMOS transistor 82, a first inverter 78, and a second inverter Phase device 80; the gate of...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More