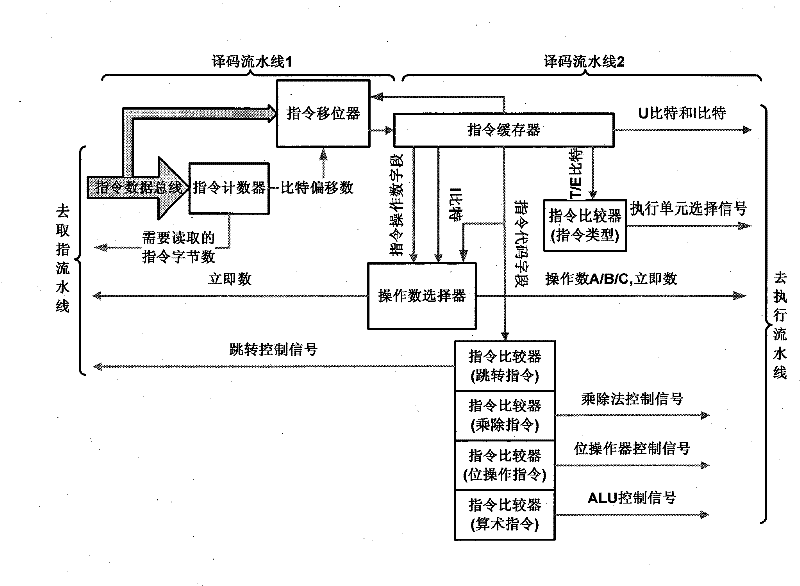

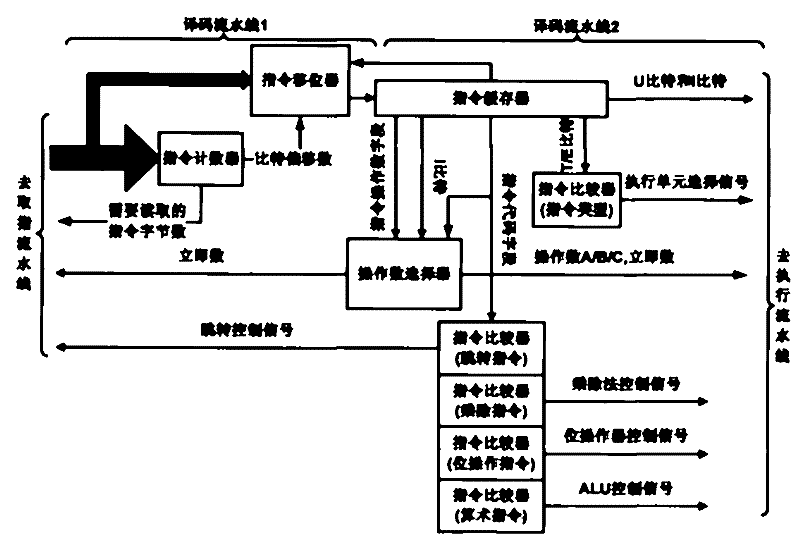

risc microprocessor instruction decoding circuit

A technology of instruction decoding and microprocessor, applied in concurrent instruction execution, machine execution devices, etc., can solve the problems of large decoding circuit, RISC microprocessor main frequency cannot be quickly increased, and complex decoding structure, etc. Achieve the effects of less circuit stages, small circuit scale, and simple decoding circuit structure

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0025] The present invention has carried out systematic design to RISC microprocessor instruction structure, has adopted variable-length code instruction set, and instruction has 8, 16, 24, 32 four kinds of codes, and the higher instruction length of use frequency is shorter, like this The code density can be improved; redundant coding is adopted, although the lengths of the four instruction codes are different, the instruction format and the meaning of the instruction field are completely consistent. Therefore, the structure of the instruction decoding circuit is very simple, the circuit scale is small, and the number of circuit stages is small; in addition, part of the instruction space is reserved for future expansion of instructions.

[0026] (1) Instruction encoding and instruction format

[0027] The various instruction codes are explained one by one below. Each instruction encoding consists of several instruction fields. Instructions are described in assembly language...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More