Method for realizing conflict-free real-time data access in FPGA (field programmable gate array)

A data and real-time technology, applied in electrical digital data processing, instruments, etc., can solve problems such as data errors and dislocations, achieve accurate access, low cost, and meet application requirements.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0016] The present invention will be further described below in conjunction with the accompanying drawings. The following examples are only used to illustrate the technical solution of the present invention more clearly, but not to limit the protection scope of the present invention.

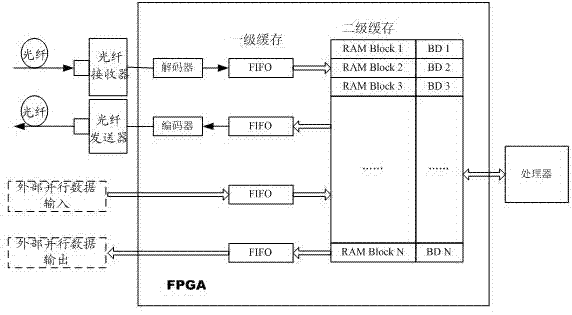

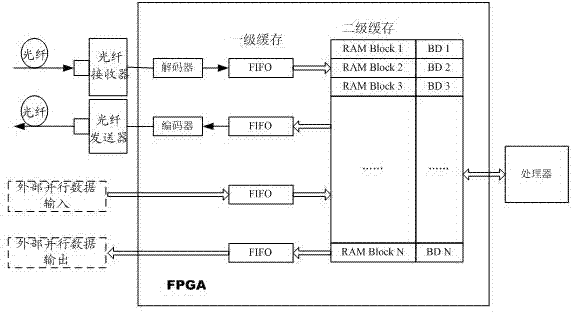

[0017] figure 1 It is a functional block diagram of the data conflict-free real-time access method implemented in FPGA. FPGA includes a primary buffer and a secondary buffer. The secondary buffer is divided into multiple data areas, and the size and number of blocks can be configured according to actual use. .

[0018] Taking reception as an example, the decoder in synchronous serial communication recovers the original data and clock from the received code stream according to the actual line code pattern, and converts the serial input data into parallel data under the control of the clock. Or combine the parallel input data into parallel data with a larger width and save it in the FIFO of the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More