Inverse ratio or small ratio NMOS (N-channel Metal Oxide Semiconductor) tube layout structure resistant to total dose irradiation effect

A radiation effect and anti-total dose technology, applied in the direction of electrical components, circuits, semiconductor devices, etc., can solve problems such as impracticality, application limitations, layout and wiring design limitations, etc., to achieve commercial process compatibility, small footprint, layout and wiring Convenience and flexible effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0026] The present invention will be further described below in conjunction with specific drawings and embodiments.

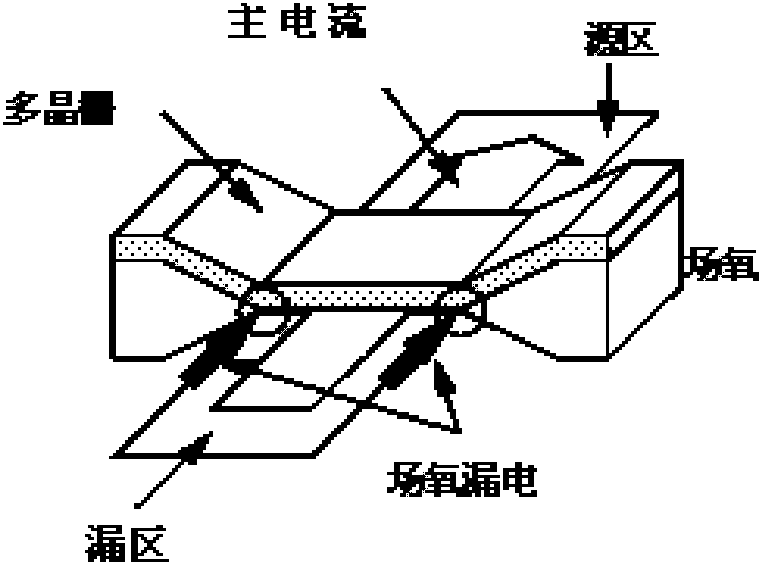

[0027] Such as figure 1 Shown: It is a conventional NMOS transistor manufactured by a self-aligned process. The polysilicon gate is deposited on a thin oxide layer, and the source / drain is formed by implanting the active area not covered by polysilicon. The circuit density produced by this process is High, but the polysilicon gate creates a parasitic transistor in the gate oxide and field-oxygen transition regions, which is very sensitive to total dose effects. Because the field oxygen and the gate oxide layer will be ionized under radiation conditions to generate electron-hole pairs; due to the trapping effect, positive charges will accumulate on the silicon dioxide side of the silicon / silicon dioxide system to form an interface state, which seriously affects to the current and voltage characteristics of transistors. As the radiation dose increases, the leak...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More