High-reliability chip scale packaging method

A chip-level packaging and reliable technology, applied in the formation of wafer-level chip-scale packaging and the metal layer under solder bumps, can solve the problems of short-circuiting of solder bumps, easy dripping between solders, affecting soldering quality, etc. Adhesion, good wetting effect, effect of improving forming quality

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

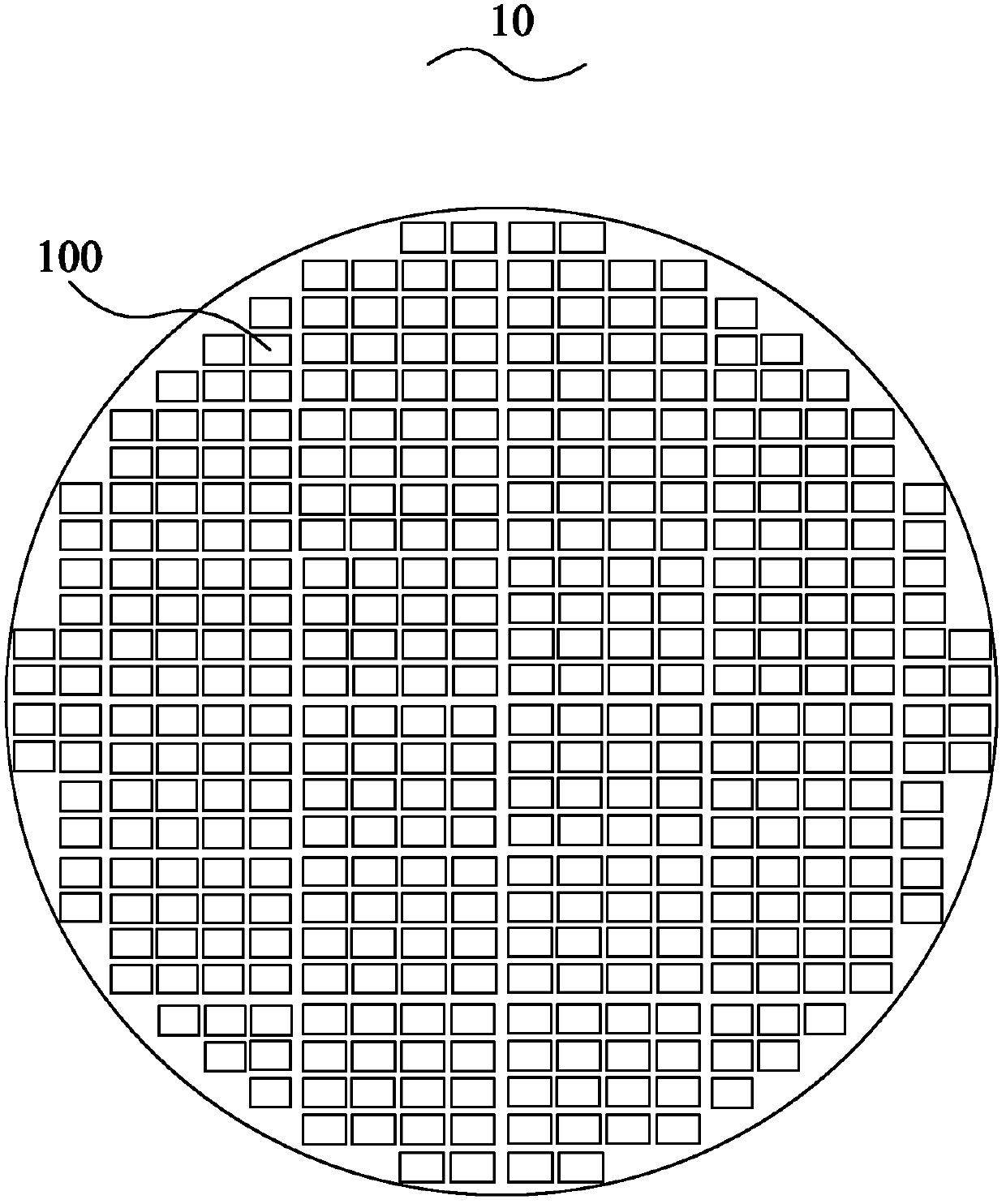

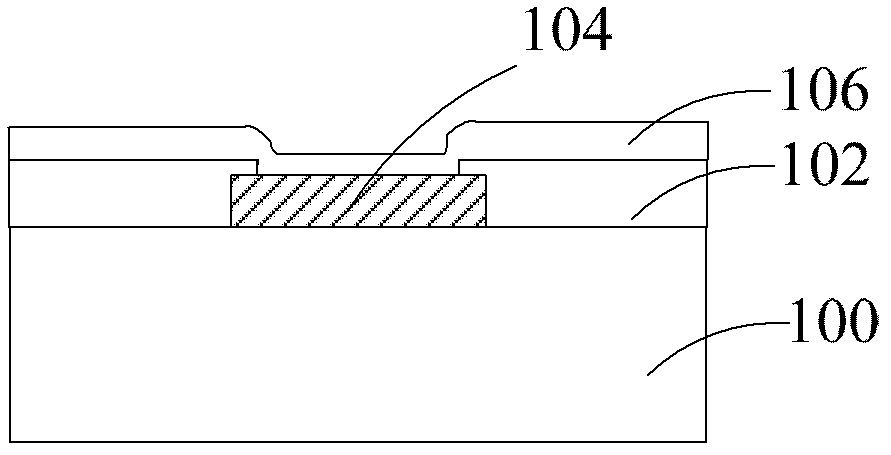

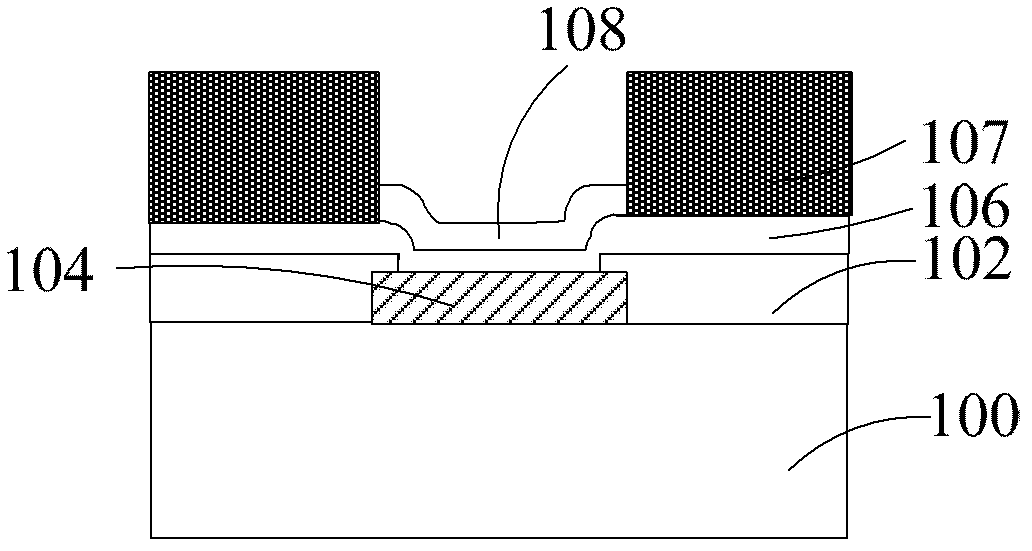

[0029] The specific embodiments of the present invention will be described in detail below in conjunction with the accompanying drawings.

[0030] figure 2 It is a flow chart of a specific embodiment of the present invention to form solder bumps, including steps:

[0031] S101, sequentially forming a heat-resistant metal layer and a metal wetting layer on the chip pad and the passivation layer;

[0032] S102, forming a photoresist on the metal wetting layer, the photoresist is provided with an opening to expose the metal wetting layer above the chip pad;

[0033] S103, sequentially forming a barrier layer and a solder protection layer on the metal wetting layer in the opening;

[0034] S104, removing the photoresist;

[0035] S105, etching the heat-resistant metal layer and the metal wetting layer on the passivation layer until the passivation layer is exposed;

[0036] S106, forming a protective glue layer on the chip, the protective glue covering the solder protective l...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More