Method for forming solder bump

A solder bump and solder technology, which is applied in the field of semiconductor device packaging, can solve the problems affecting soldering quality, solder bump performance and reliability, and achieve the effects of improving forming quality, improving adhesion and good humidification.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

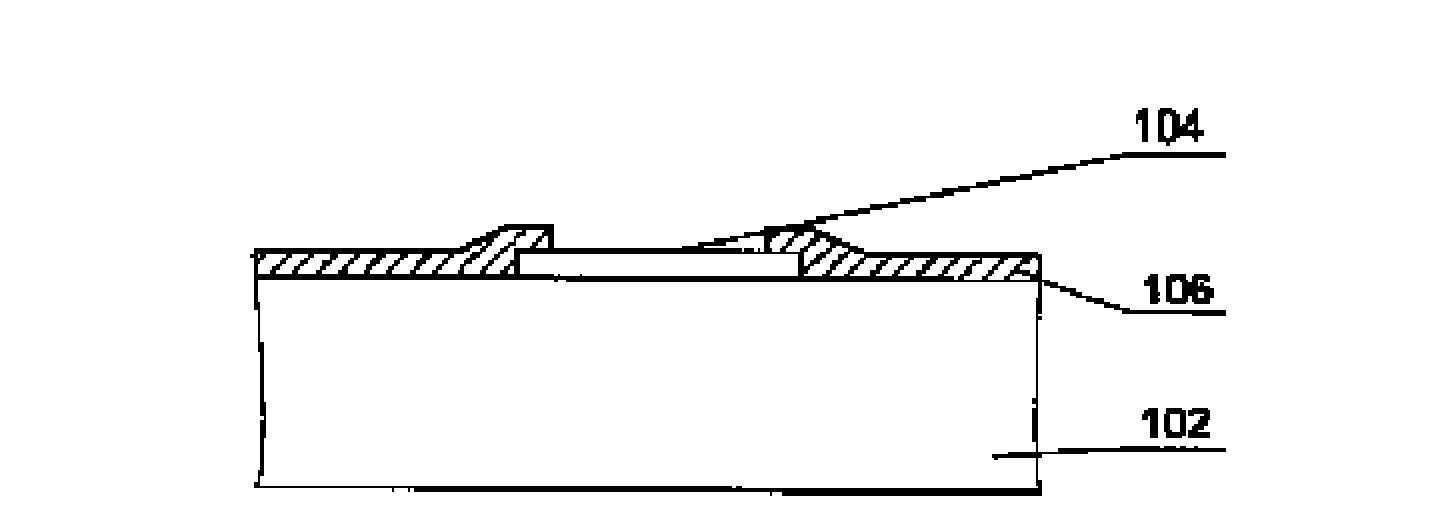

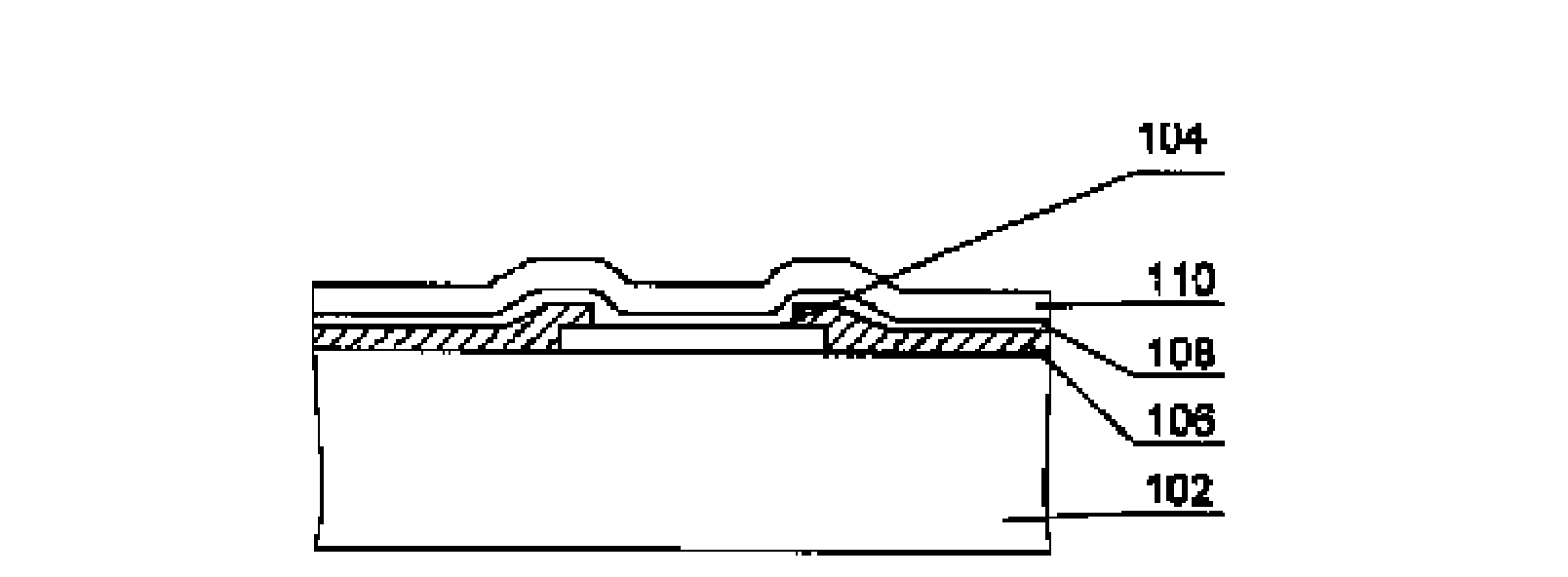

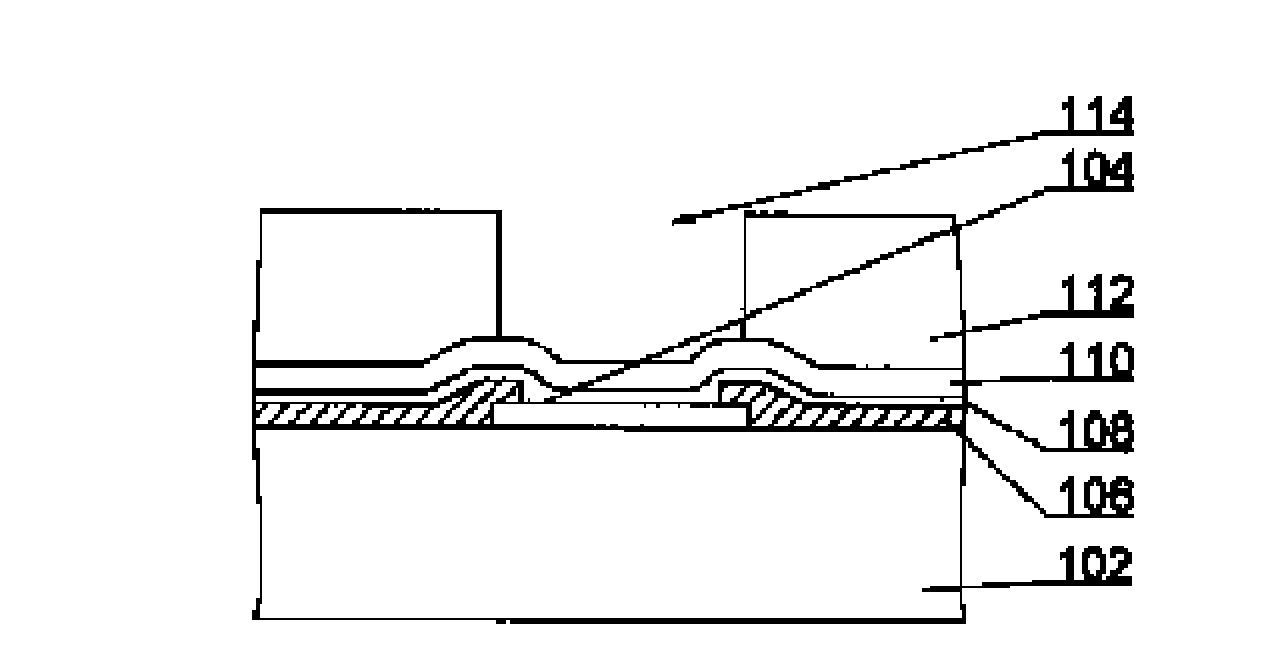

[0023] The specific embodiments of the present invention will be described in detail below in conjunction with the accompanying drawings.

[0024] figure 2 It is a flow chart of a specific embodiment of the present invention to form solder bumps, including steps:

[0025] S101, sequentially forming a heat-resistant metal layer and a metal wetting layer on the chip pad and the passivation layer;

[0026] S102, forming a photoresist on the metal wetting layer, the photoresist is provided with an opening to expose the metal wetting layer above the chip pad;

[0027] S103, sequentially forming a barrier layer and a solder protection layer on the metal wetting layer in the opening;

[0028] S104, forming a solder paste on the solder protection layer;

[0029] S105, removing the photoresist;

[0030] S106, etching the heat-resistant metal layer and the metal wetting layer on the passivation layer until the passivation layer is exposed;

[0031] S107 , reflowing the solder past...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More