Patents

Literature

204 results about "Wetting layer" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

In experimental physics, a wetting layer is an initial layer of atoms that is epitaxially grown on a surface upon which self-assembled quantum dots or thin films are created. The atoms composing a wetting layer can be semimetallic elements/compounds (usually InAs in the case of self-assembled quantum dots) or metallic alloys (for thin films). This article refers to the wetting layer used for quantum dot applications. By spraying a surface with layers of these atoms under high temperature, this wetting layer residue is produced on the surface. Wetting layers control the artificial atomic states of the quantum dot for uses in quantum information processing and quantum computation.

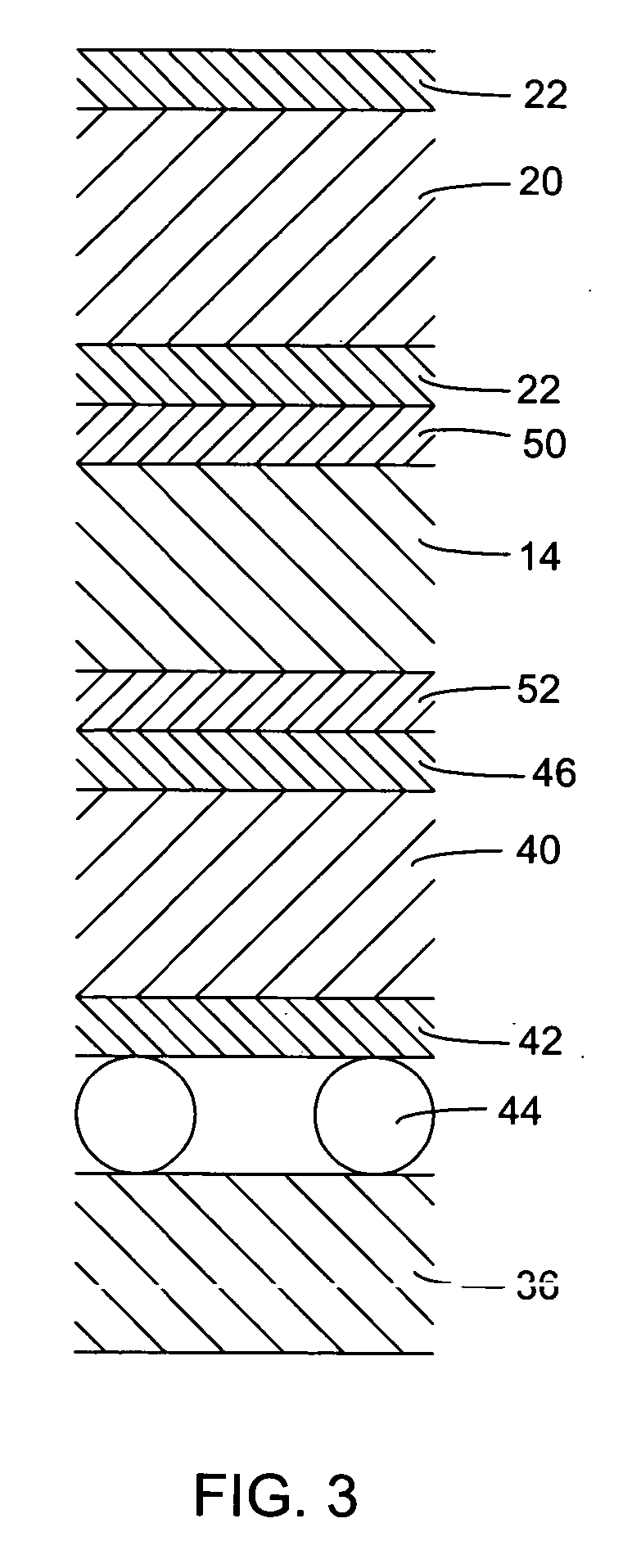

Electronic assembly having a wetting layer on a thermally conductive heat spreader

InactiveUS6504242B1Maintain temperatureSemiconductor/solid-state device detailsSolid-state devicesIndiumHeat cycling

An electronic assembly including a die, having an integrated circuit formed therein, a thermally conductive heat spreader, and indium located between the die and the heat spreader, is described. The heat spreader has a layer of nickel. A gold layer is formed on the nickel layer, and provides better wetting of indium than nickel. A better structural connection between the indium and the heat spreader is provided, especially during thermal cycling.

Owner:INTEL CORP

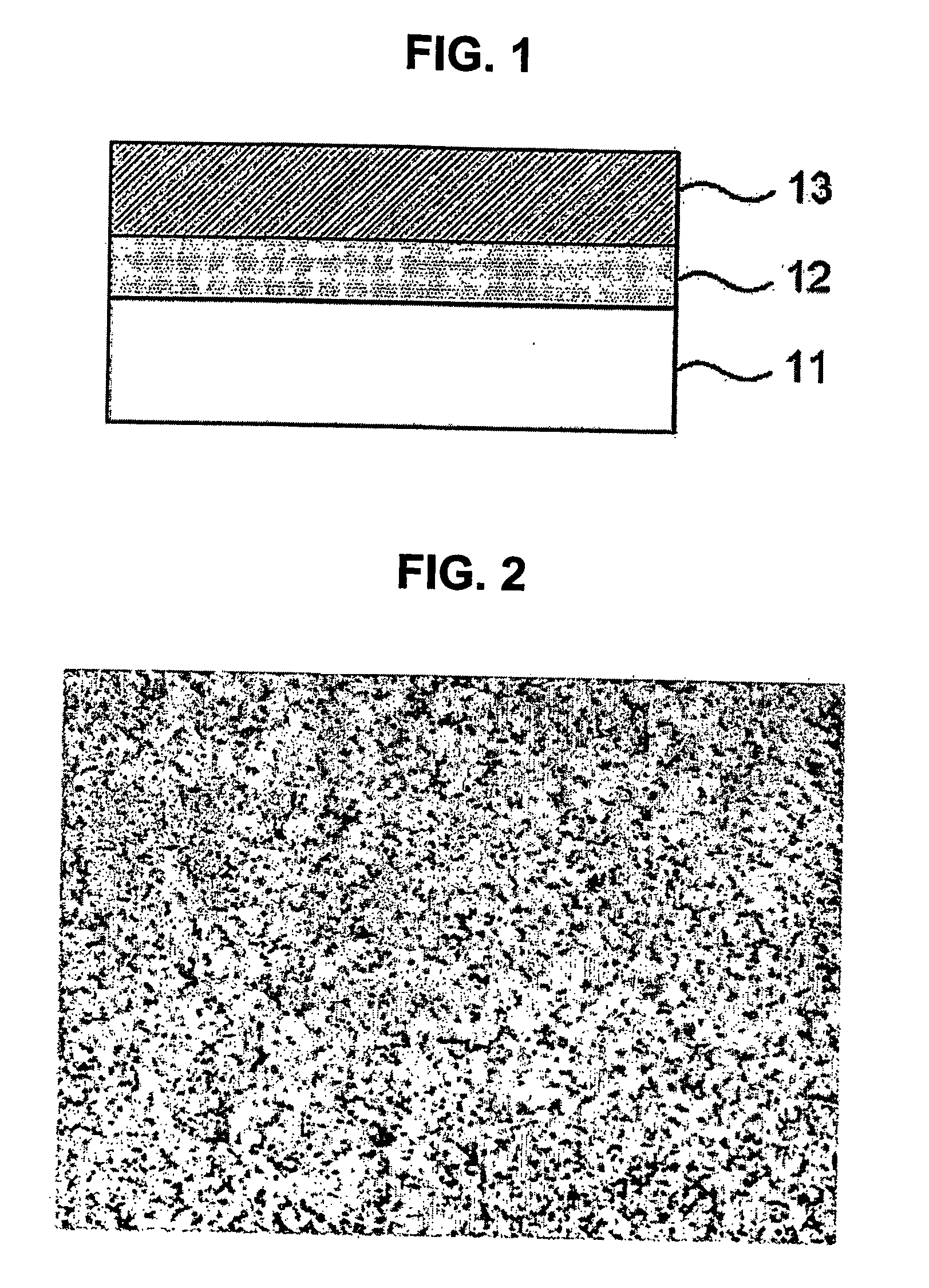

Thin Films and Methods of Making Them

InactiveUS20020197831A1Increase productionImprove device yieldTransistorMaterial nanotechnologyAnti-reflective coatingSilicon membrane

<heading lvl="0">Abstract of Disclosure< / heading> Thin, smooth silicon-containing films are prepared by deposition methods that utilize a silicon-containing precursor. In preferred embodiments, the methods result in Si-containing films that are continuous and have a thickness of about 150 Åor less, a surface roughness of about 5 Å rms or less, and a thickness non-uniformity of about 20% or less. Preferred silicon-containing films display a high degree of compositional uniformity when doped or alloyed with other elements. Preferred deposition methods provide improved manufacturing efficiency and can be used to make various useful structures such as wetting layers, HSG silicon, quantum dots, dielectric layers, anti-reflective coatings (ARC s), gate electrodes and diffusion sources.

Owner:ASM IP HLDG BV

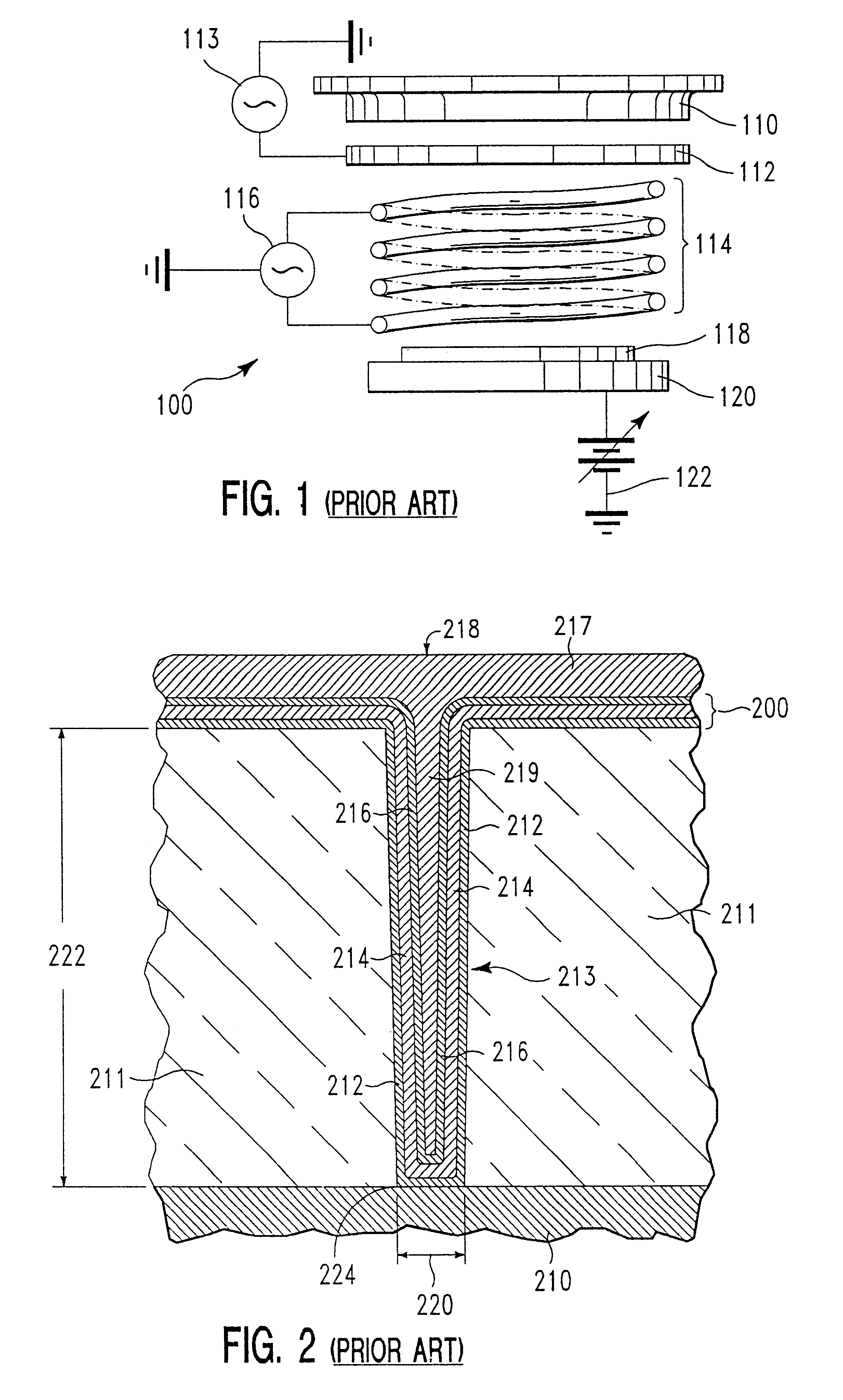

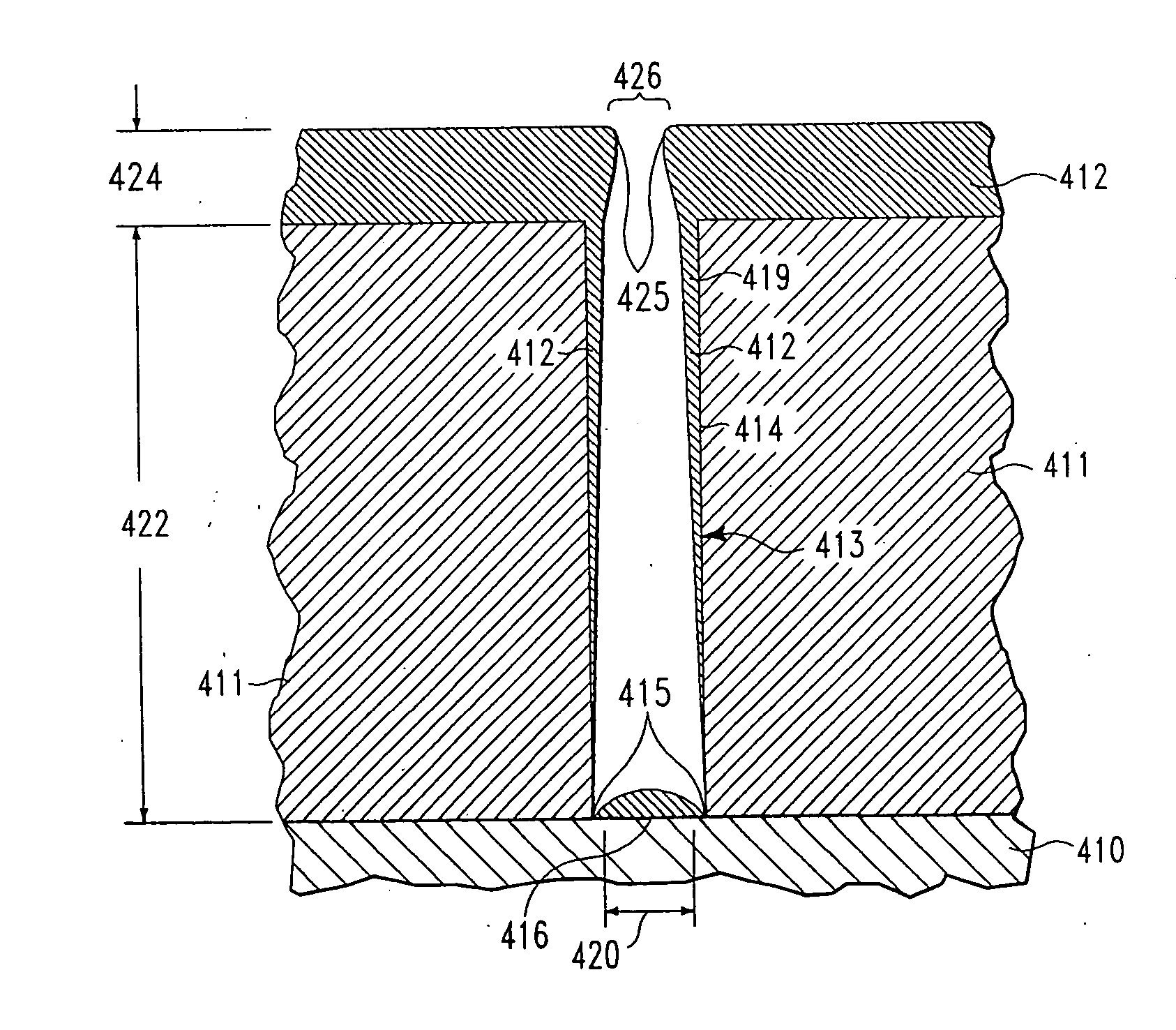

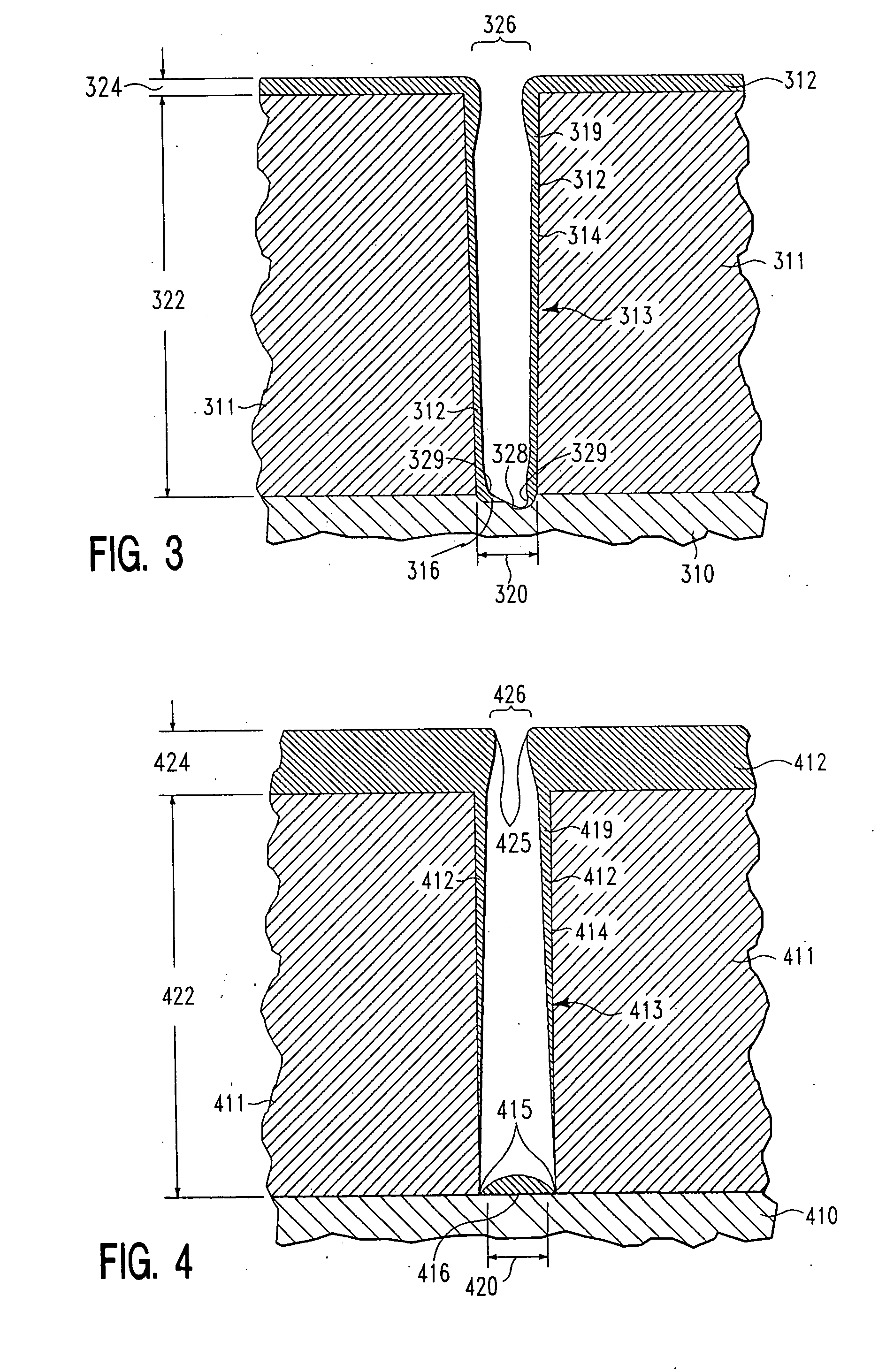

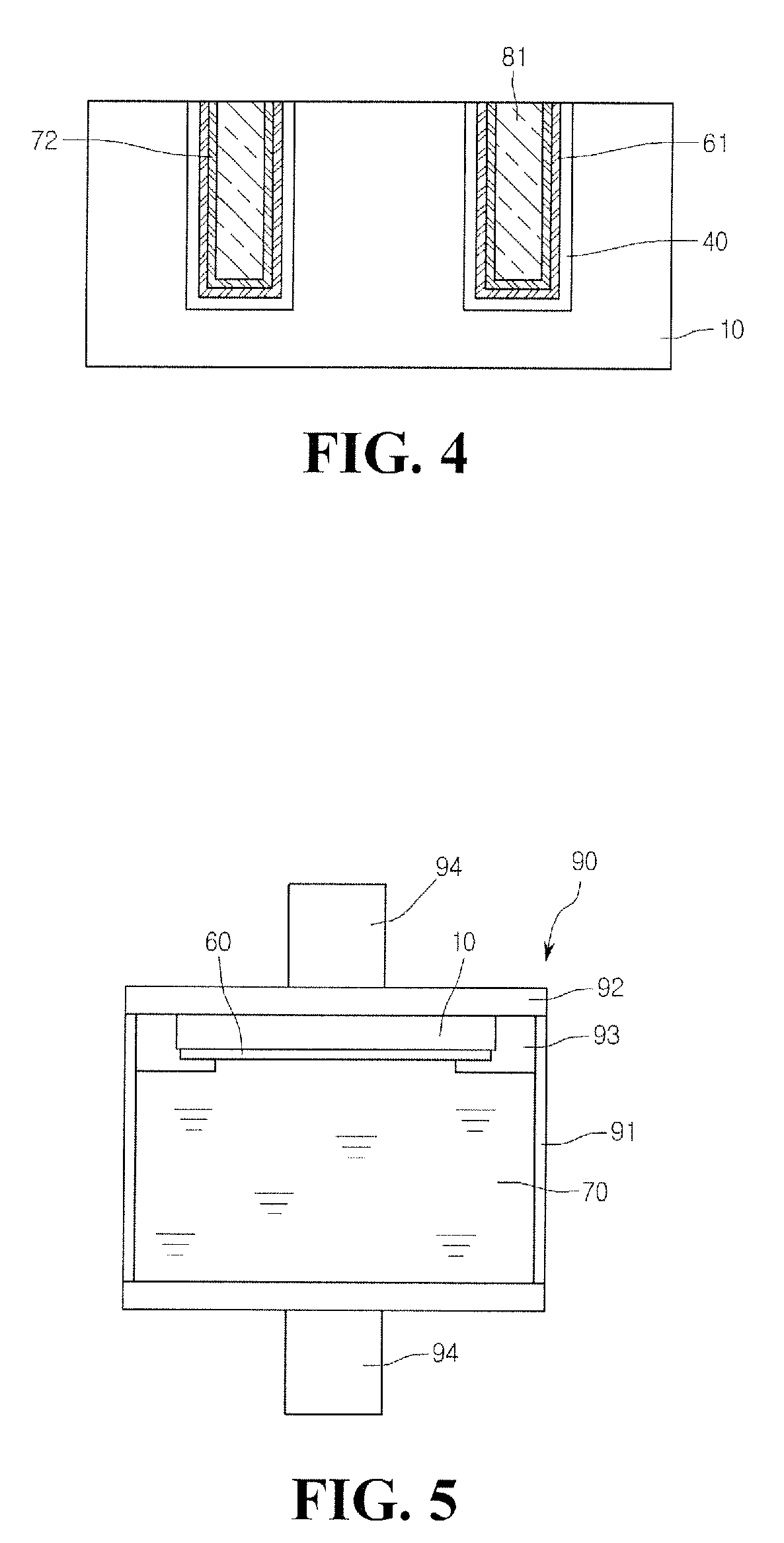

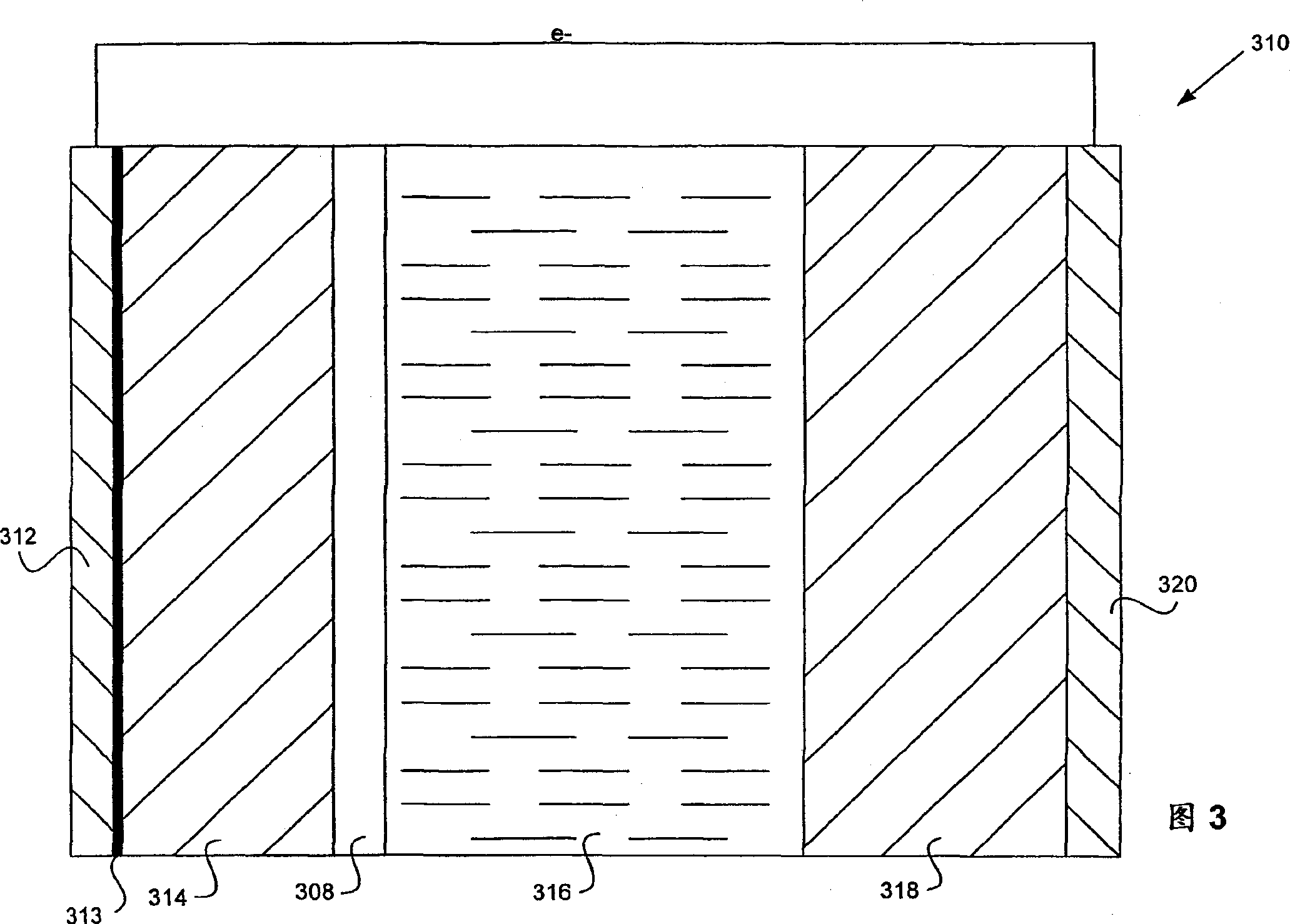

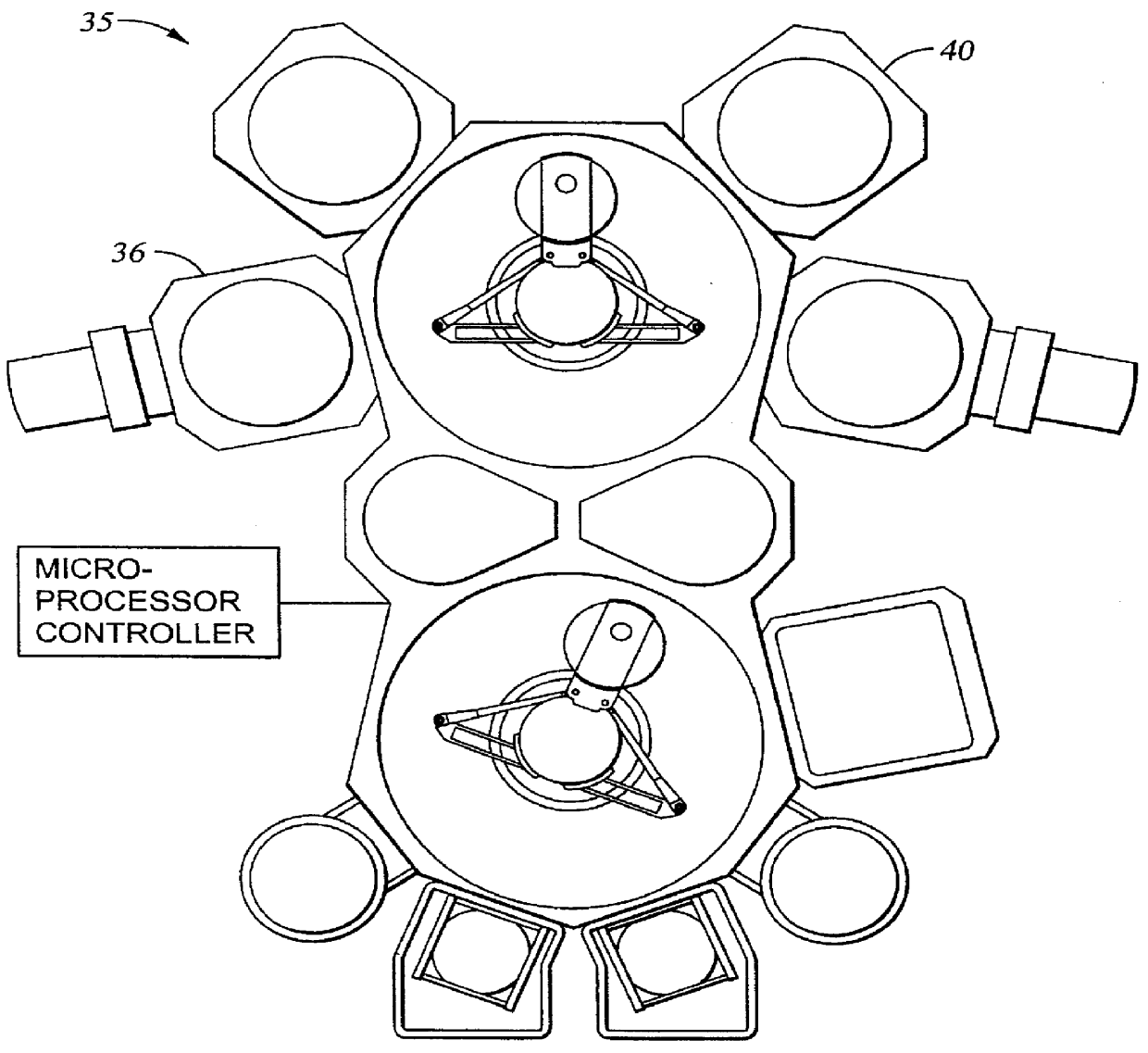

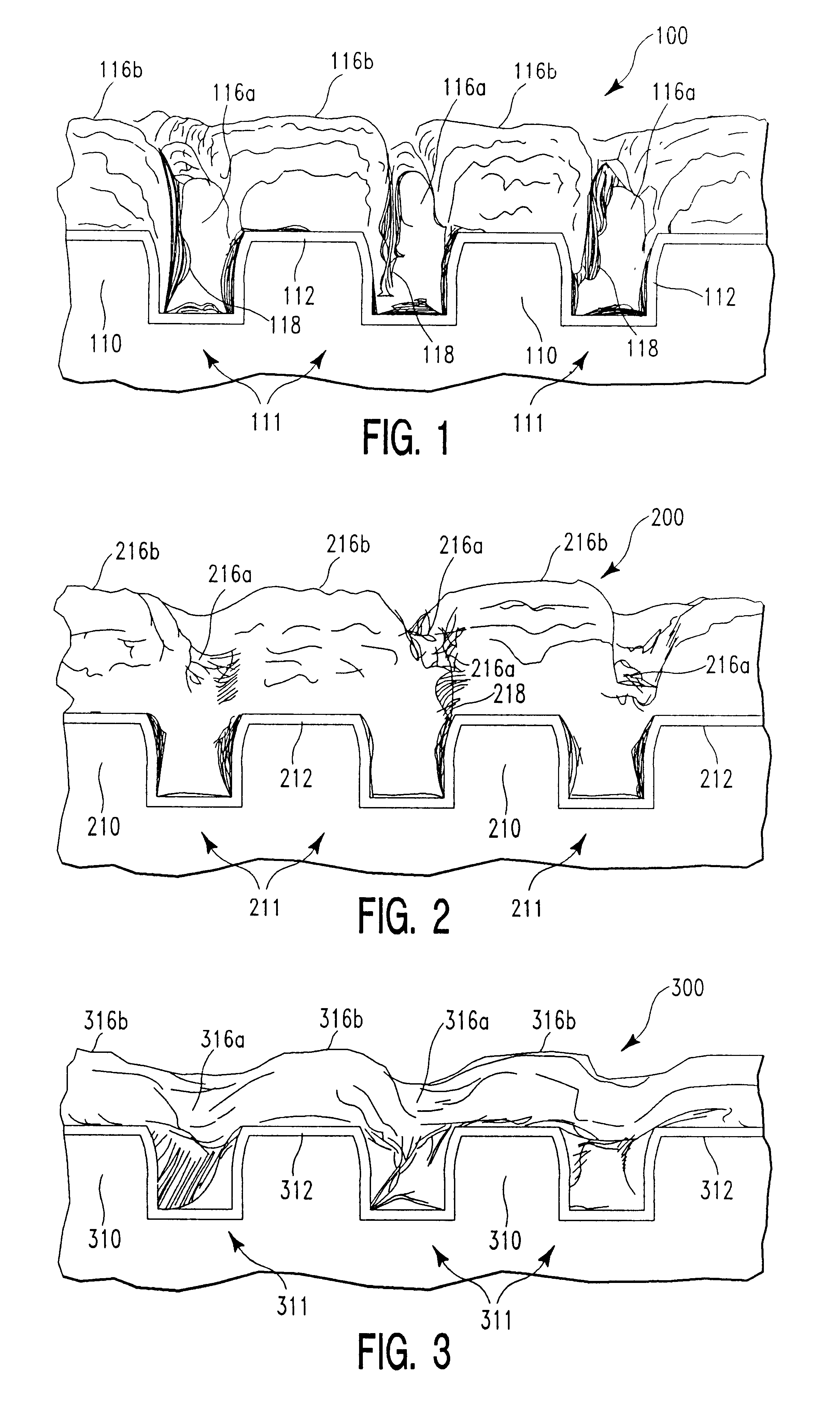

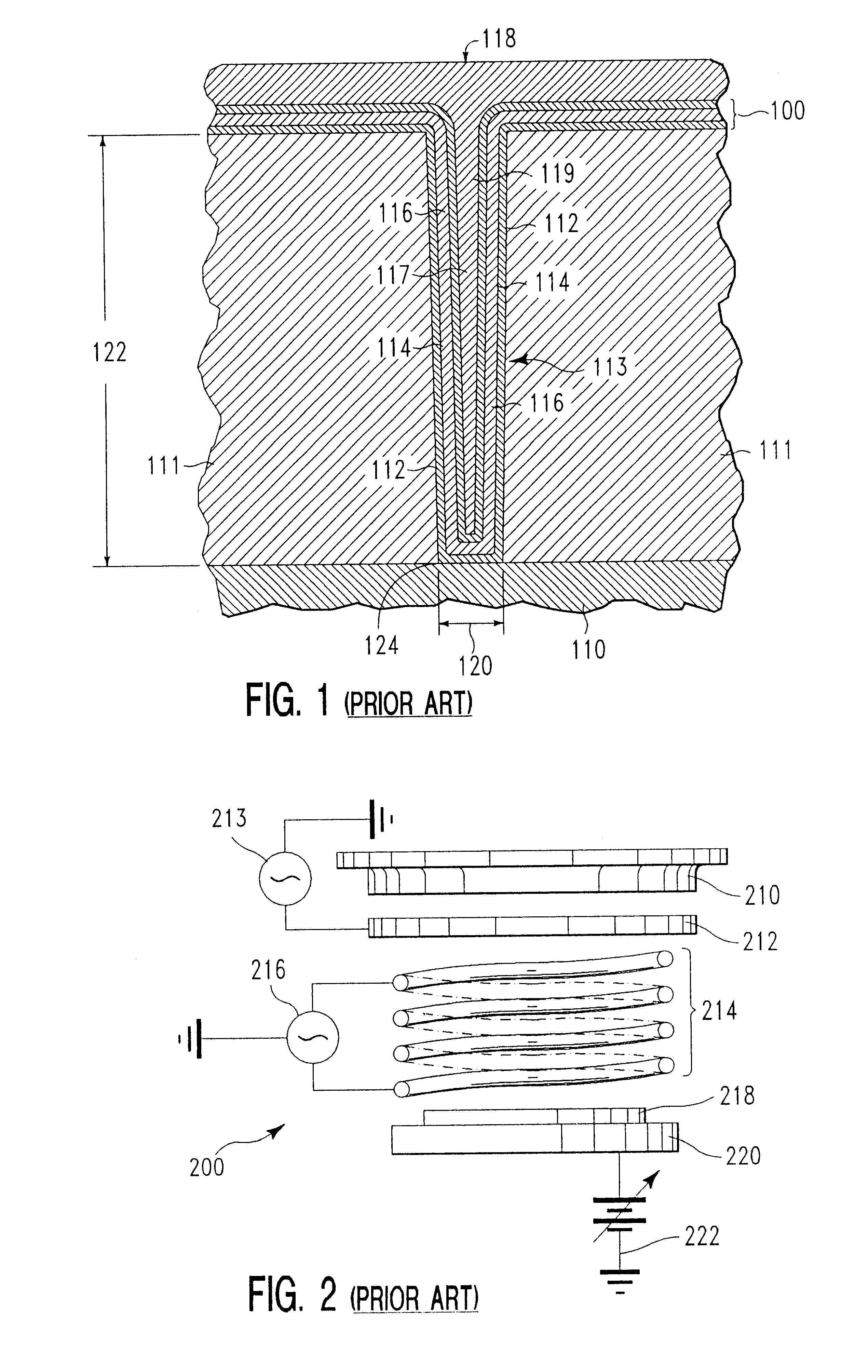

Low temperature integrated via and trench fill process and apparatus

InactiveUS6139697AInhibition formationFacilitated DiffusionSemiconductor/solid-state device detailsVacuum evaporation coatingAir exposureCopper

The present invention relates generally to an improved process for providing complete via fill on a substrate and planarization of metal layers to form continuous, void-free contacts or vias in sub-half micron applications. In one aspect of the invention, a refractory layer is deposited onto a substrate having high aspect ratio contacts or vias formed thereon. A CVD metal layer, such as CVD Al or CVD Cu, is then deposited onto the refractory layer at low temperatures to provide a conformal wetting layer for a PVD Cu. Next, a PVD Cu is deposited onto the previously formed CVD Cu layer at a temperature below that of the melting point temperature of the metal. The resulting CVD / PVD Cu layer is substantially void-free. The metallization process is preferably carried out in an integrated processing system that includes both a PVD and CVD processing chamber so that once the substrate is introduced into a vacuum environment, the metallization of the vias and contacts occurs without the formation of an oxide layer over the CVD Cu layer. The via fill process of the present invention is also successful with air-exposure between the CVD Cu and PVD Cu steps.

Owner:APPLIED MATERIALS INC

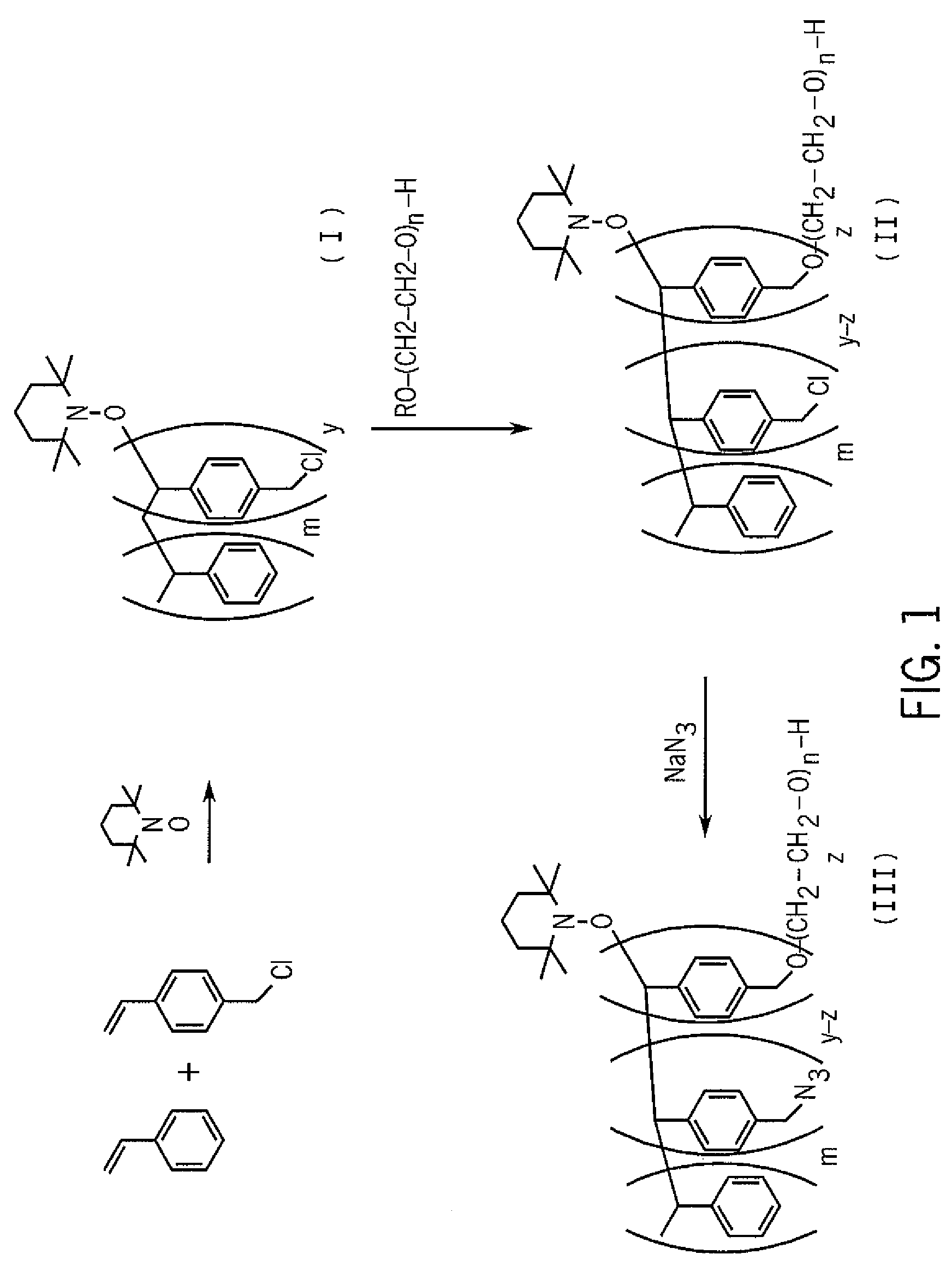

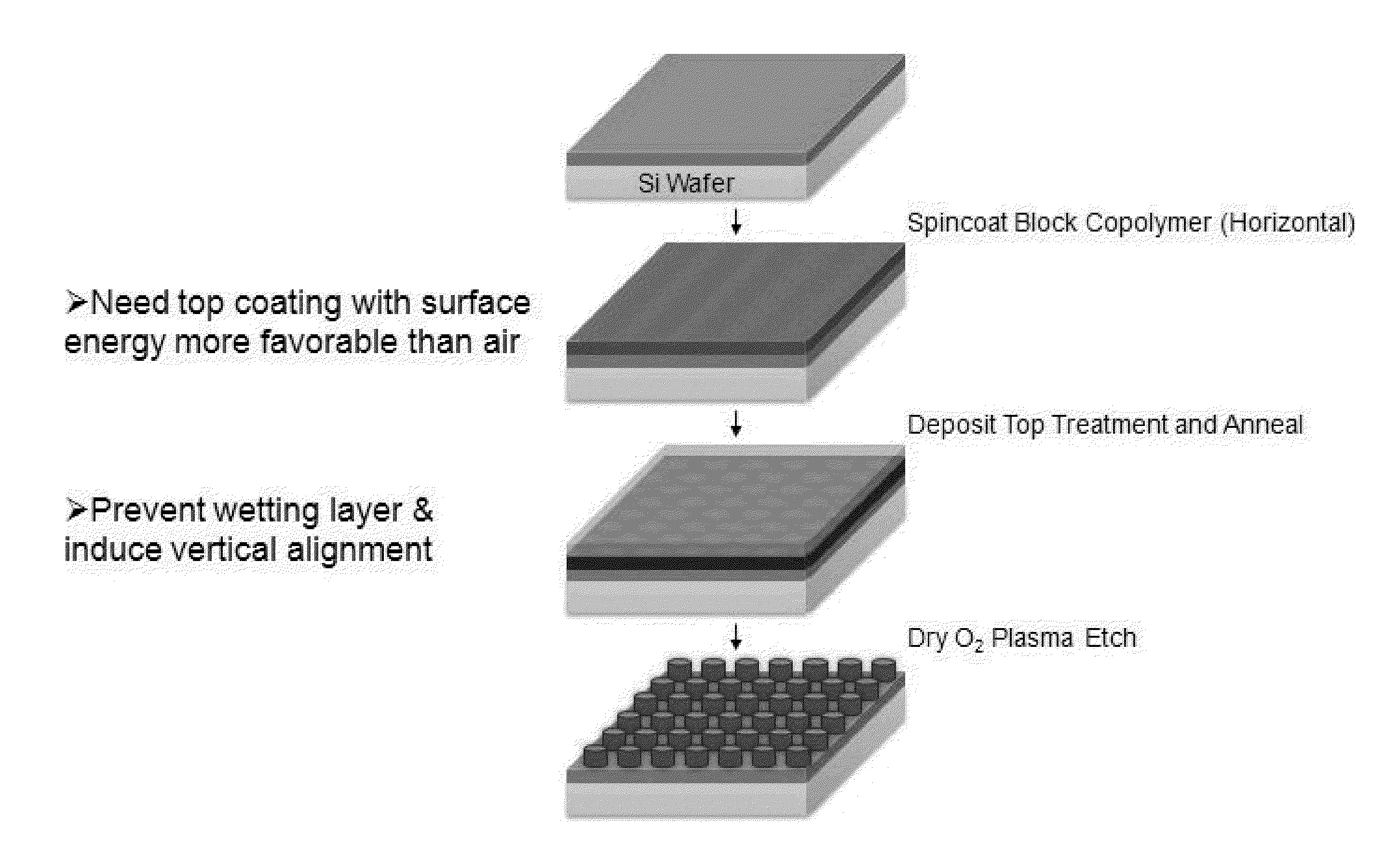

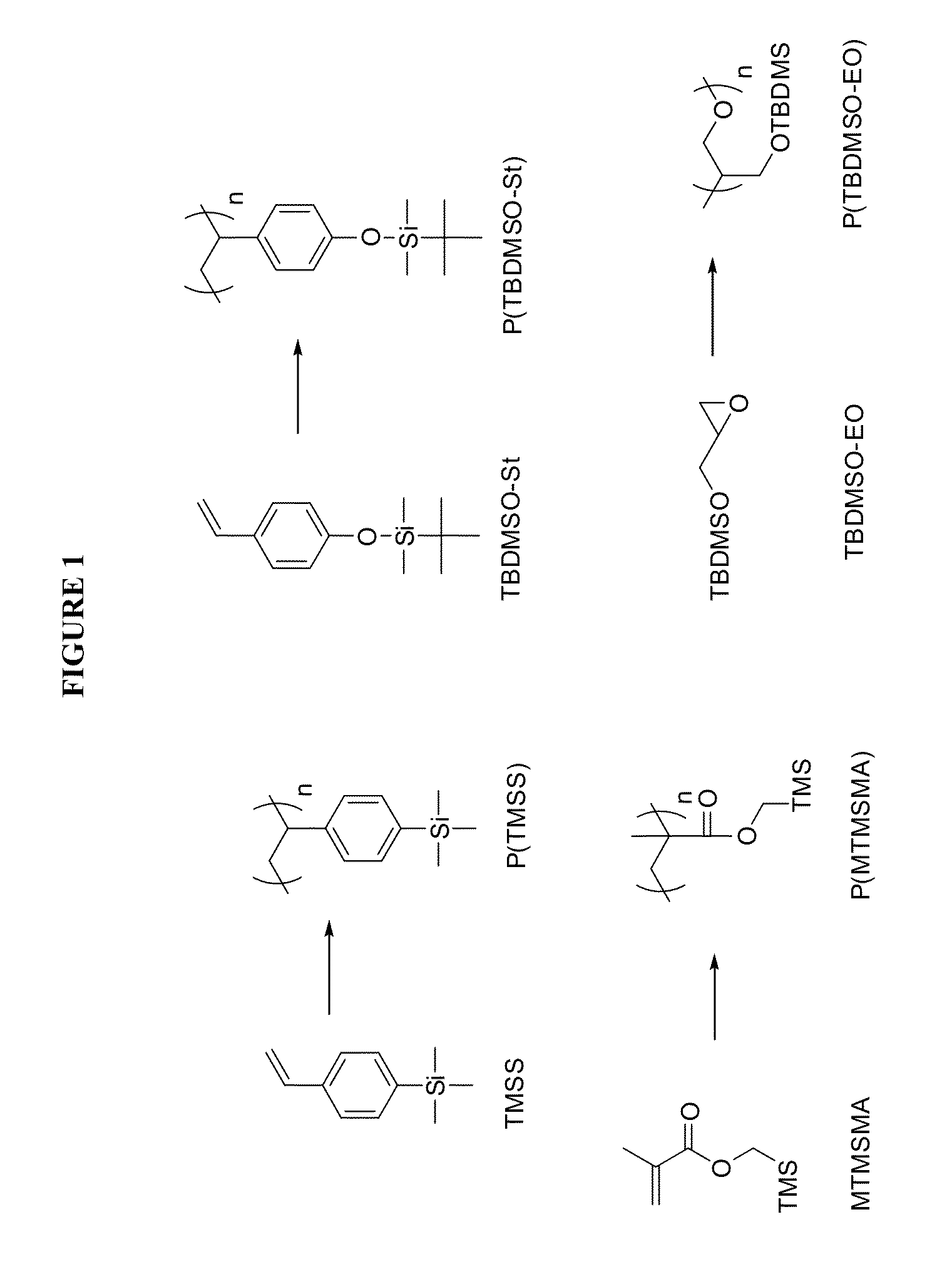

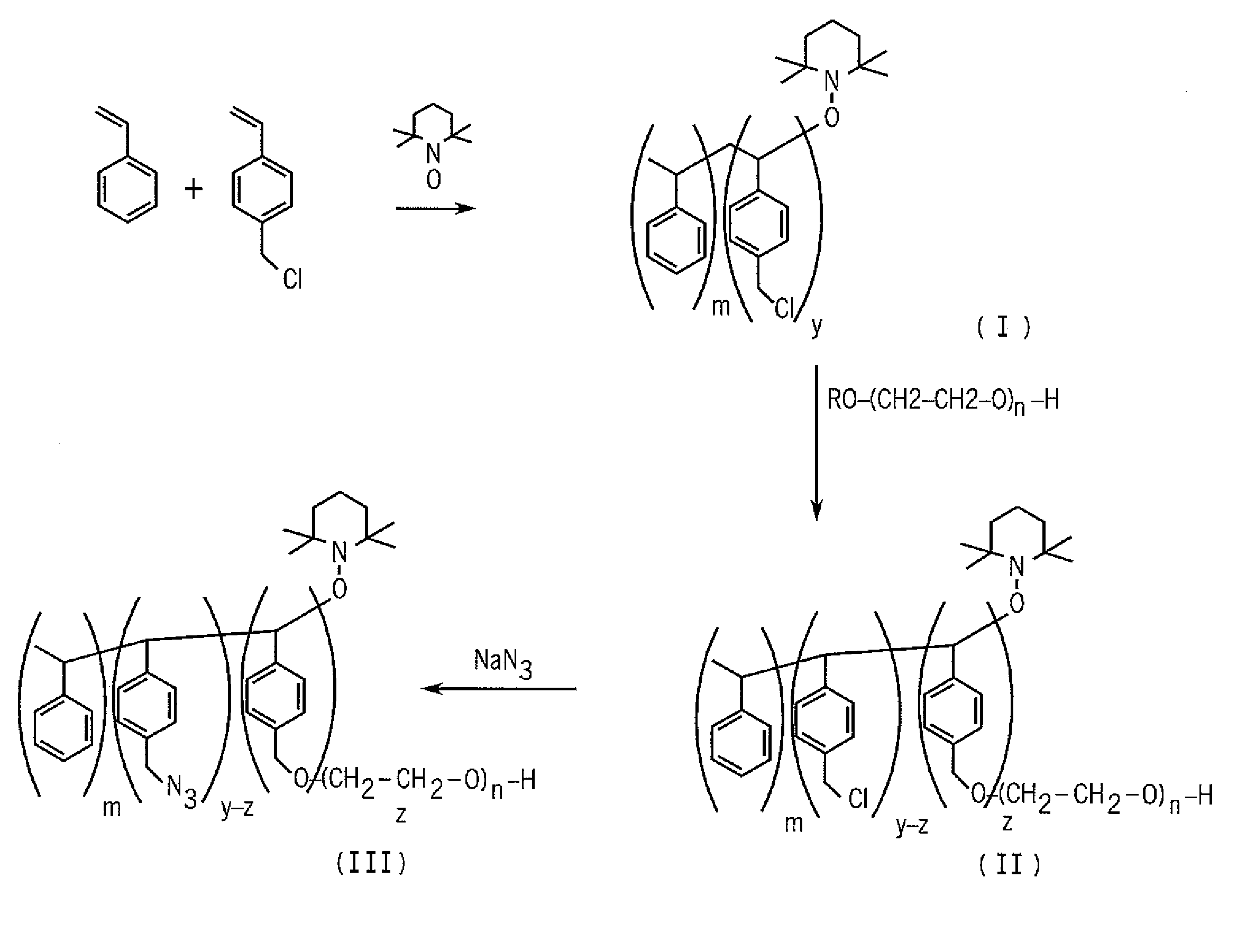

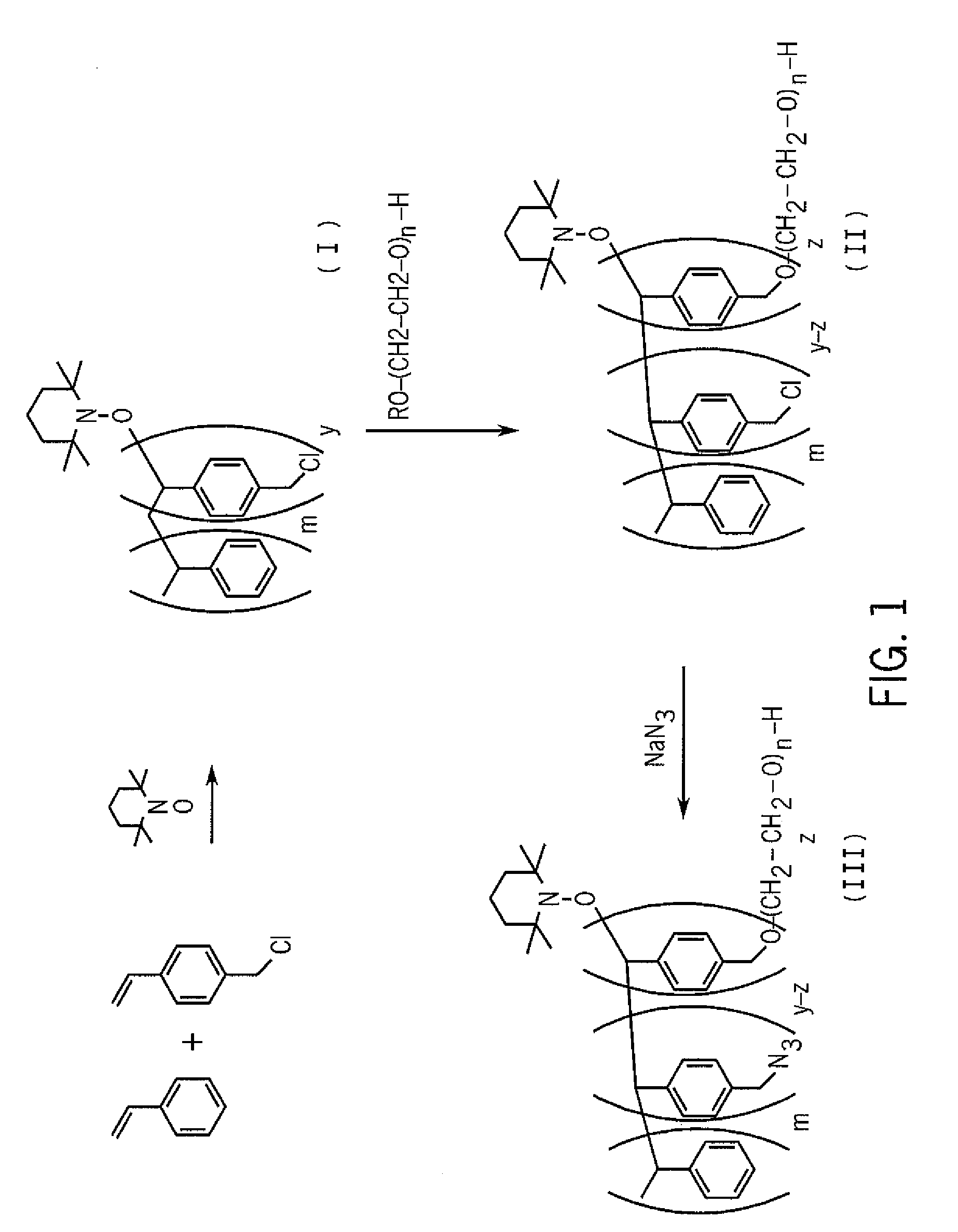

Crosslinkable Graft Polymer Non-Preferentially Wetted by Polystyrene and Polyethylene Oxide

ActiveUS20080318005A1Material nanotechnologyDecorative surface effectsPolyethylene oxidePolymer science

Methods for fabricating a random graft PS-r-PEO copolymer and its use as a neutral wetting layer in the fabrication of sublithographic, nanoscale arrays of elements including openings and linear microchannels utilizing self-assembling block copolymers, and films and devices formed from these methods are provided. In some embodiments, the films can be used as a template or mask to etch openings in an underlying material layer.

Owner:MICRON TECH INC

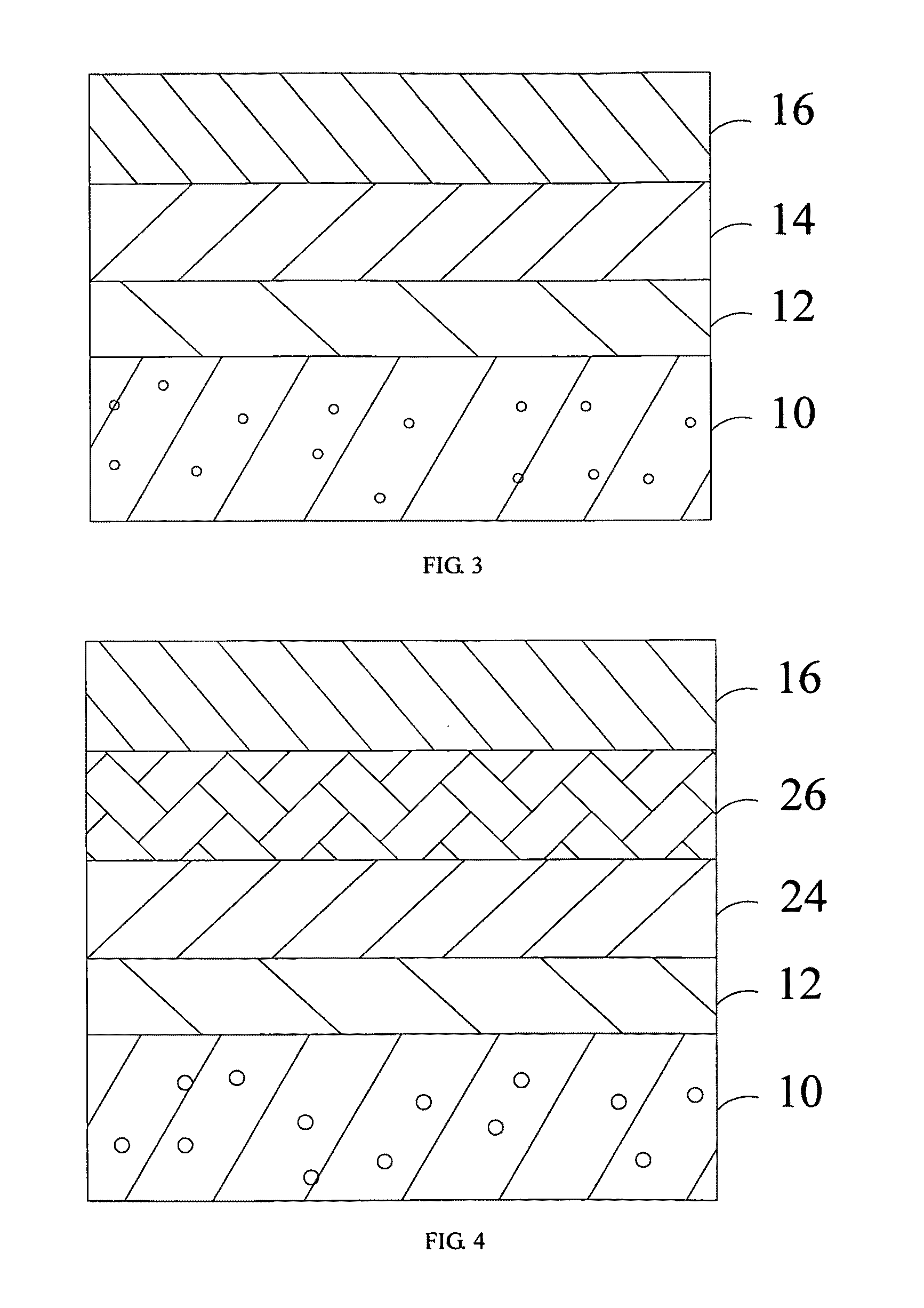

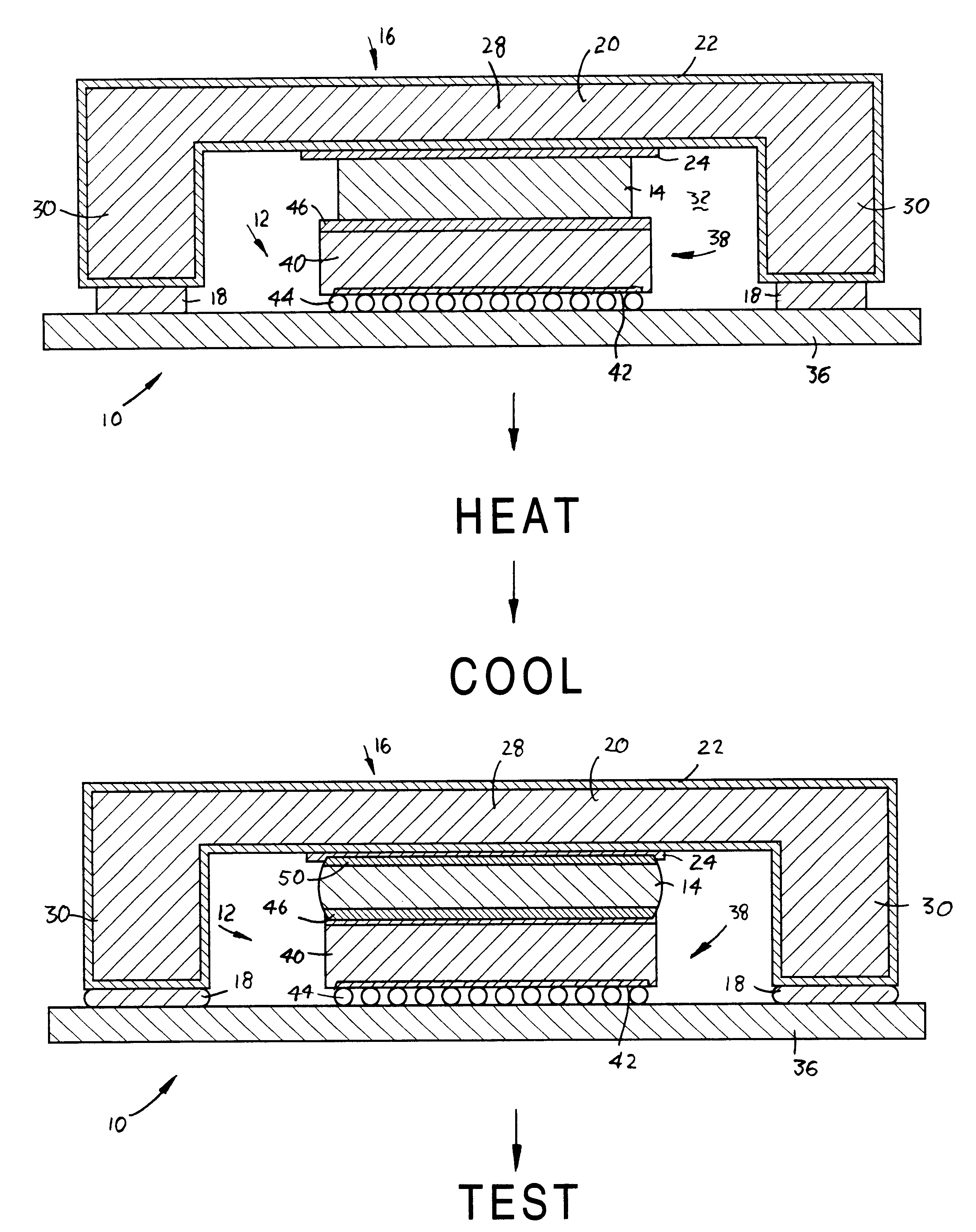

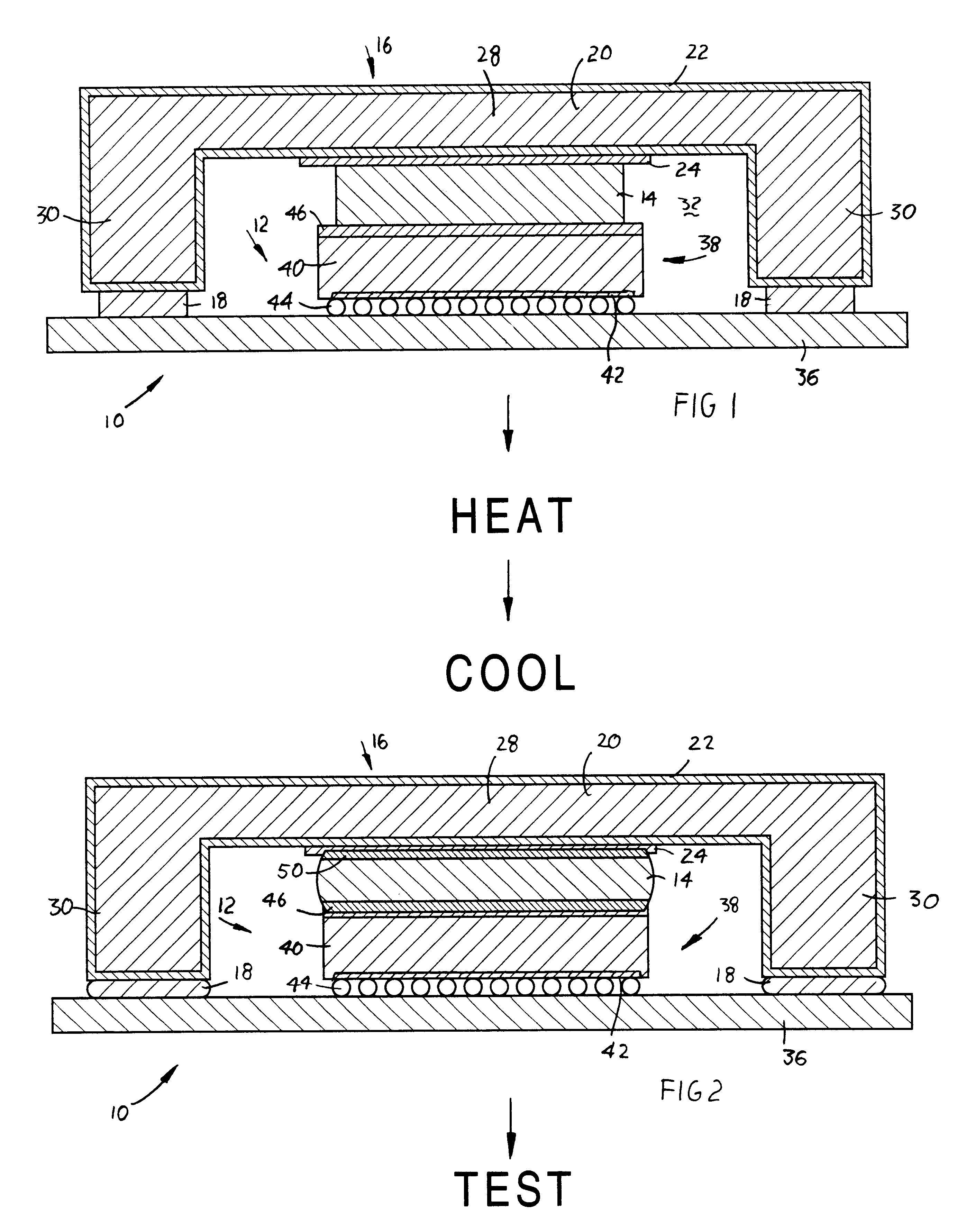

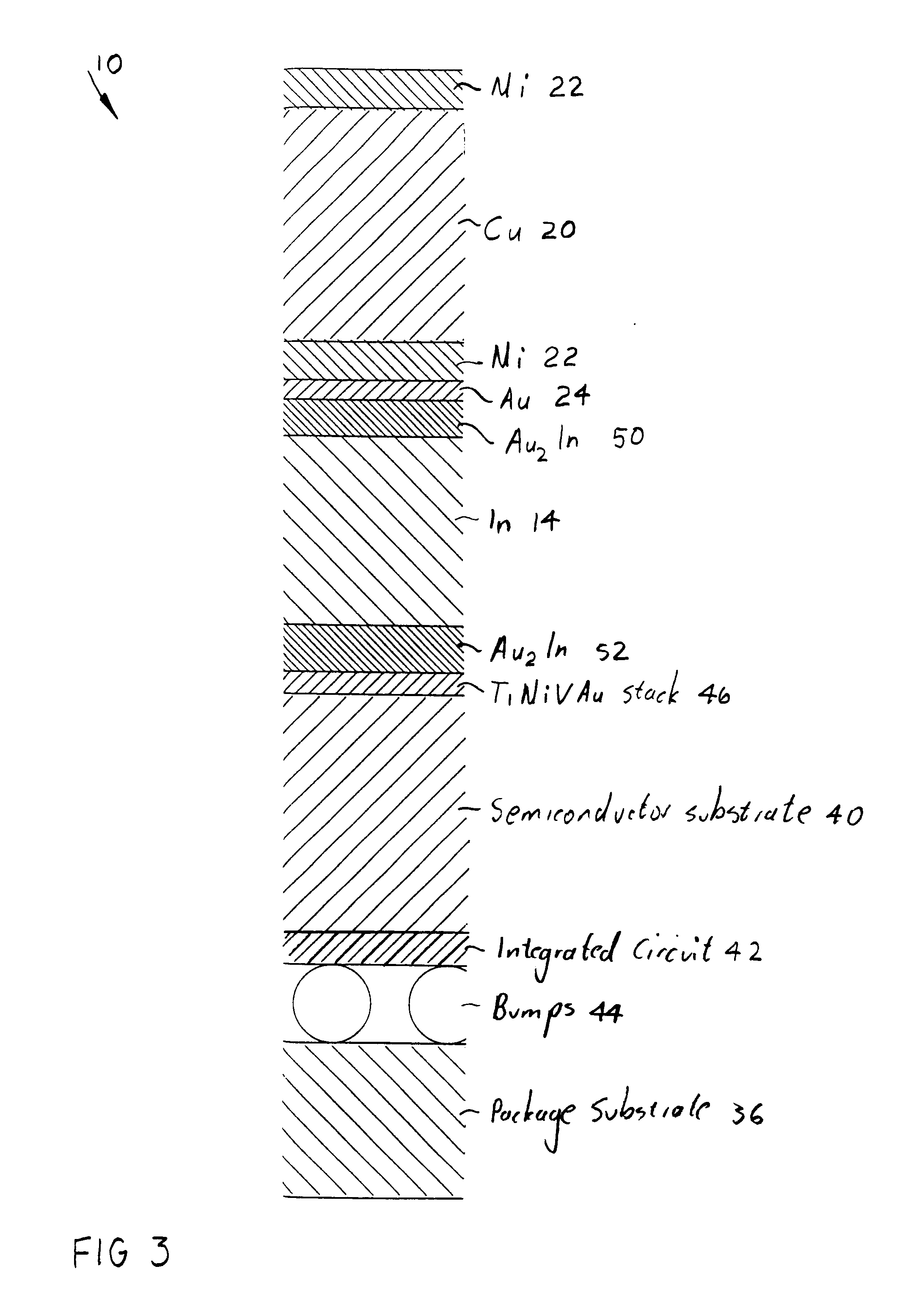

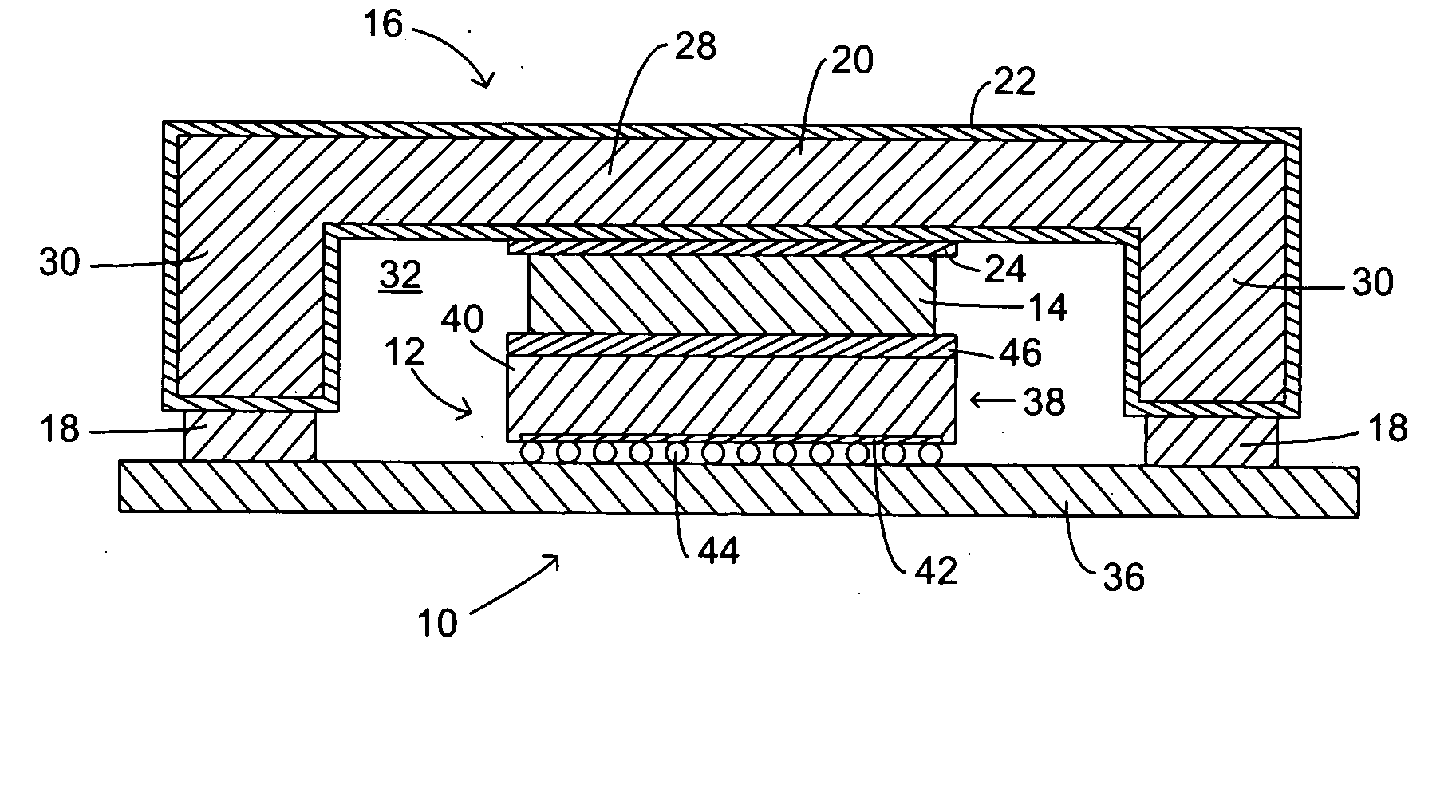

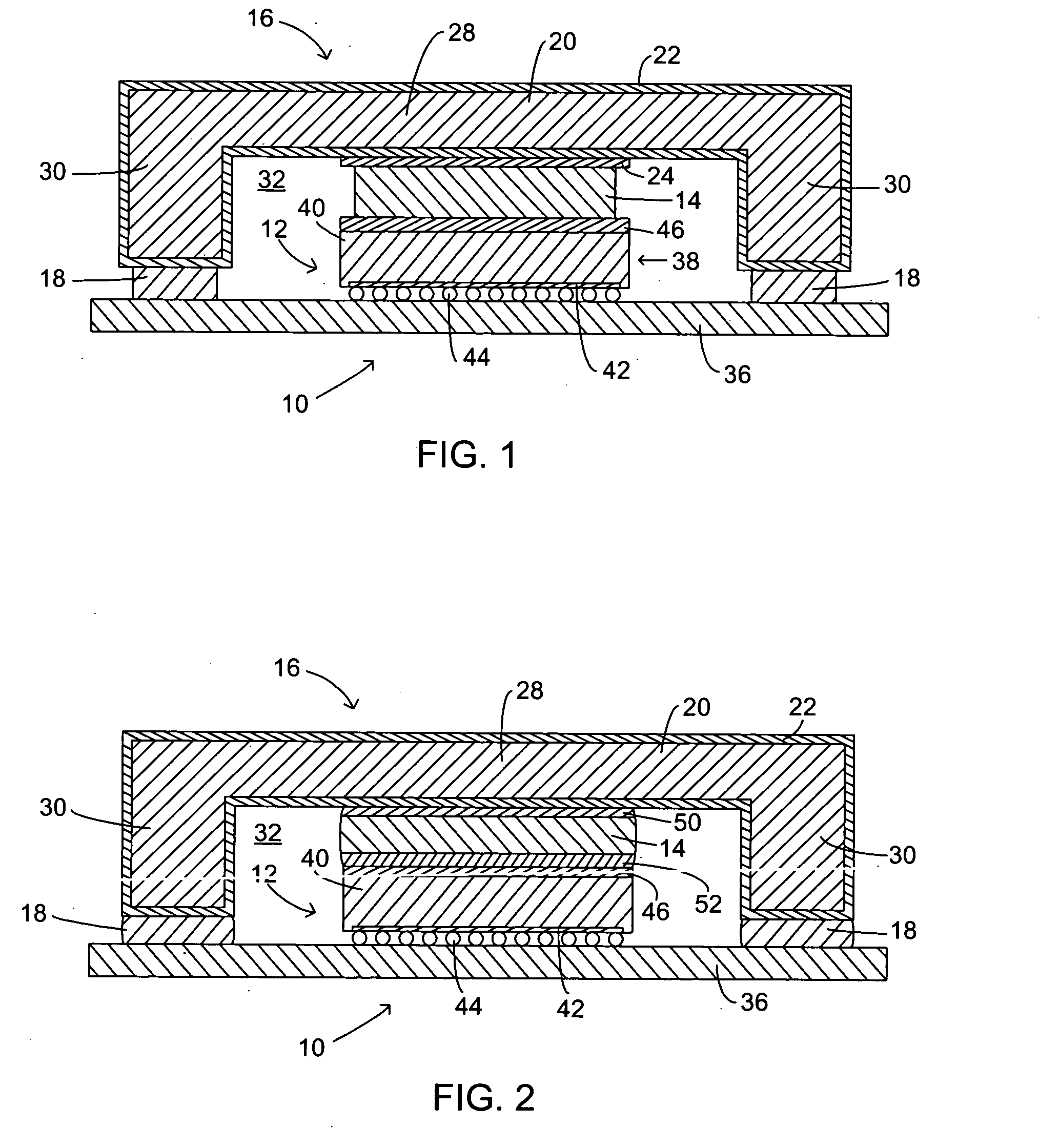

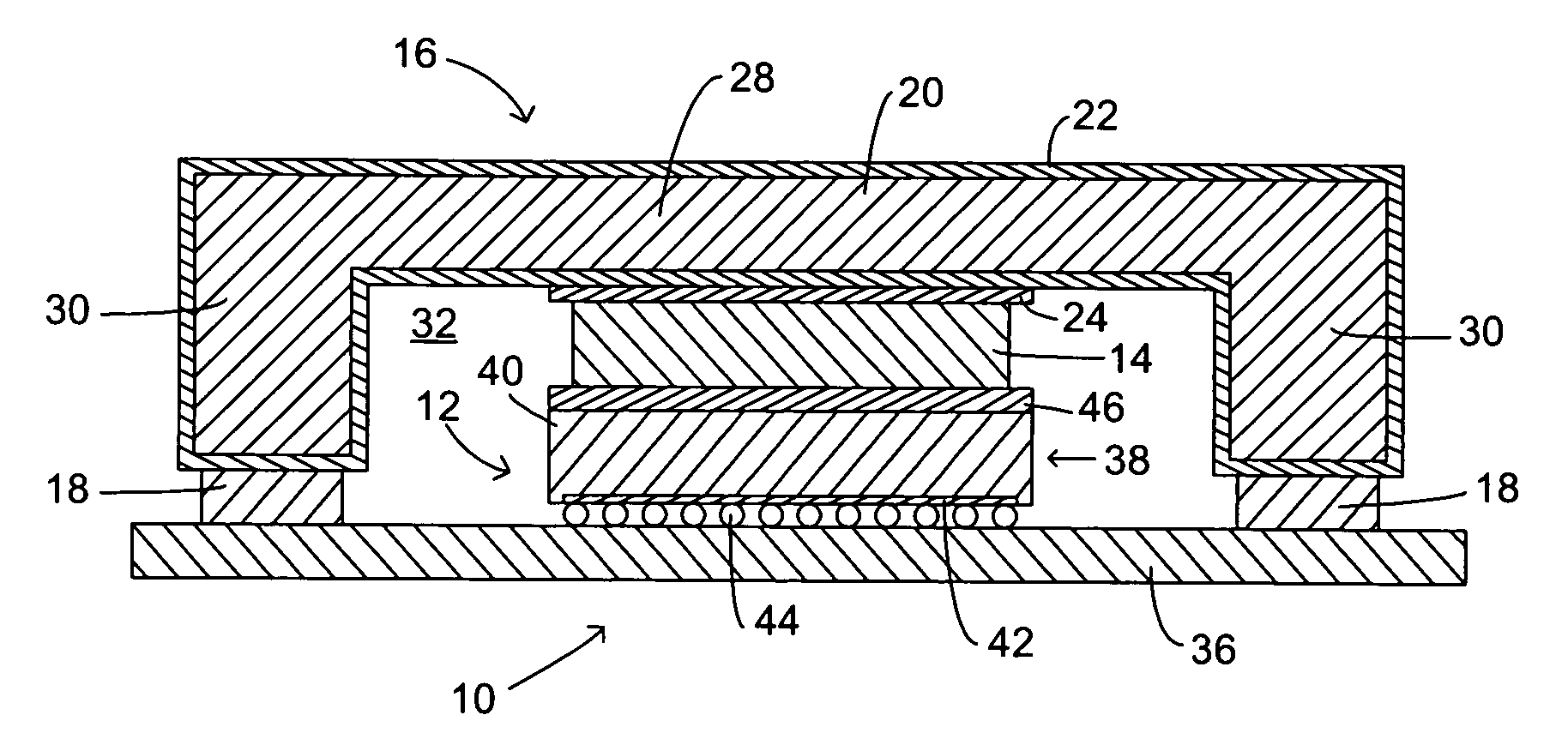

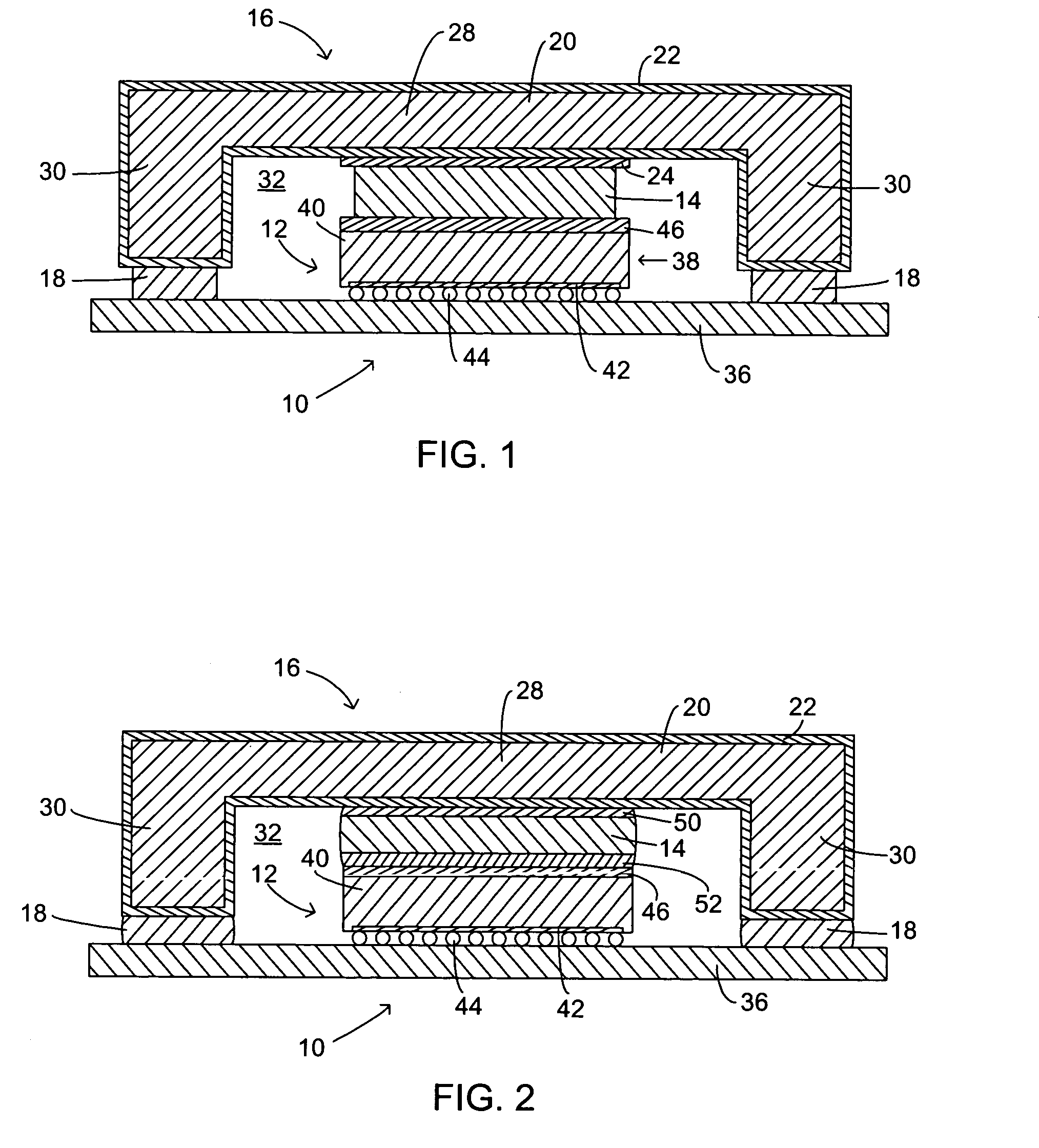

Electronic assembly having an indium wetting layer on a thermally conductive body

ActiveUS20050280142A1Semiconductor/solid-state device detailsSolid-state devicesIndiumElectronic assemblies

Embodiments include electronic packages and methods for forming electronic packages. One method includes providing a die and a thermal interface material on the die. A metal body is adapted to fit over the die. A wetting layer of a material comprising indium is formed on the metal body. The thermal interface material on the die is brought into contact with the wetting layer of material comprising indium. The thermal interface material is heated to form a bond between the thermal interface material and the wetting layer so that the thermal interface material is coupled to the metal body, and to form a bond between the thermal interface material and the die so that the thermal interface material is coupled to the die.

Owner:INTEL CORP

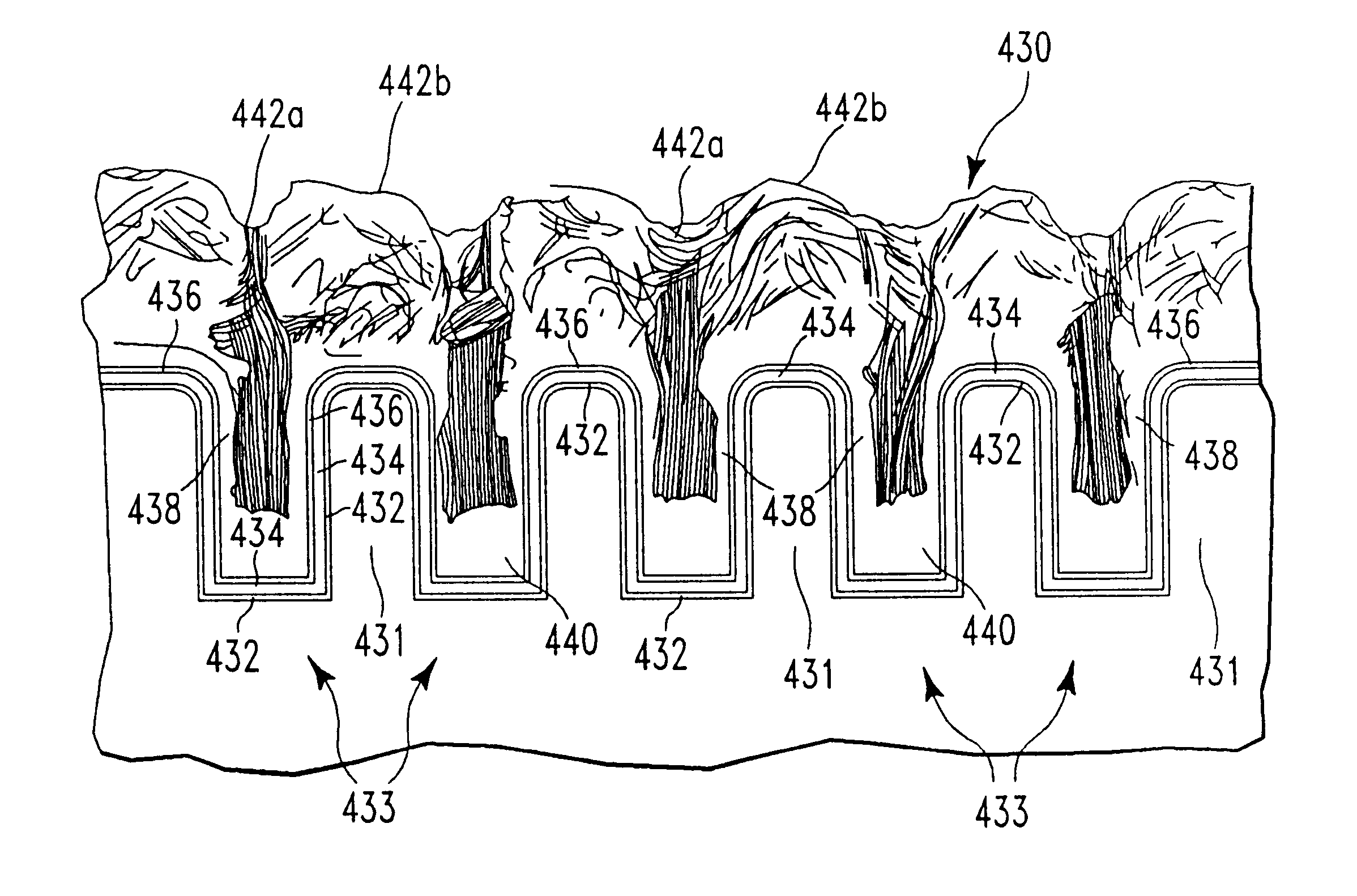

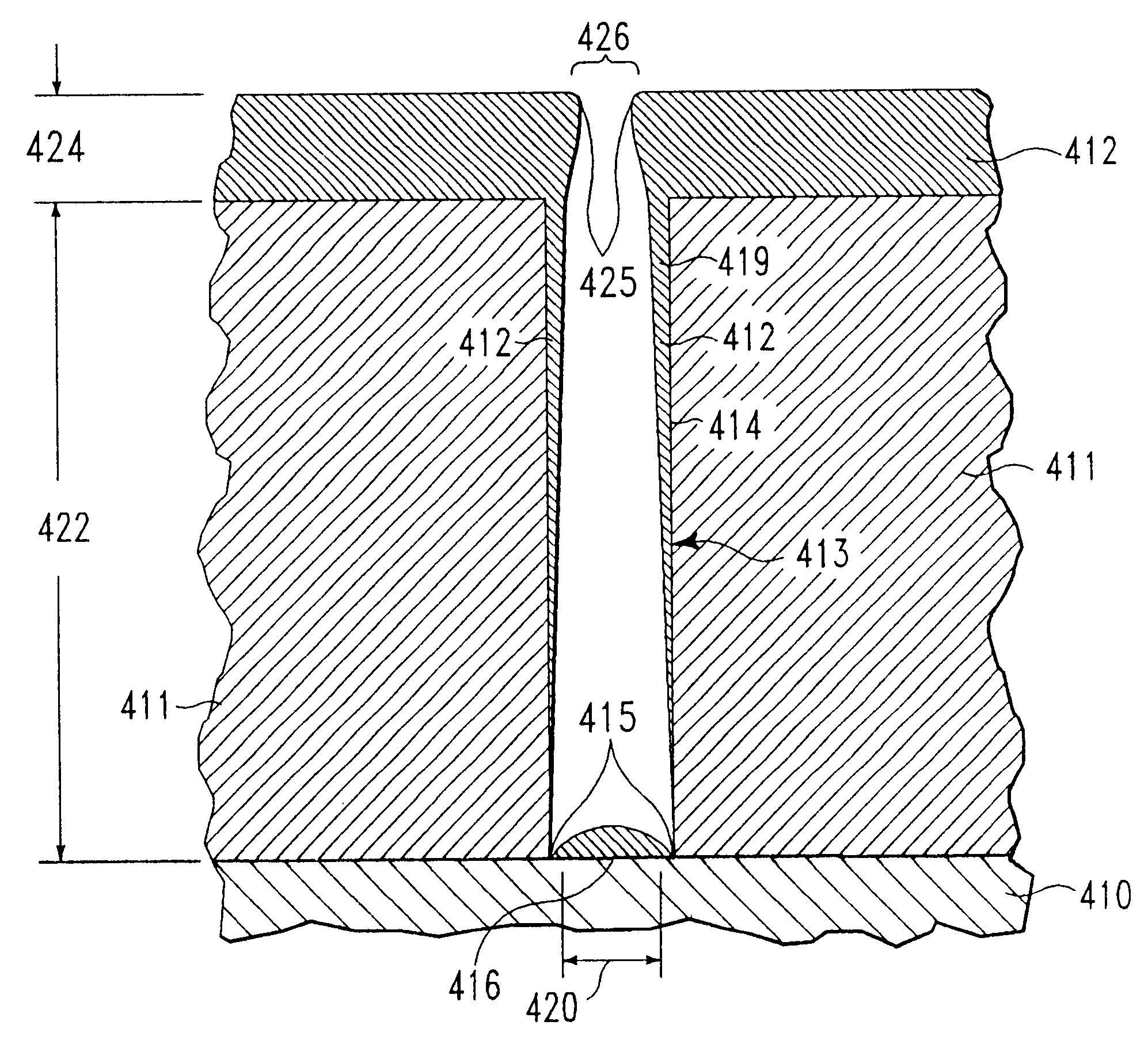

Method of sputtering copper to fill trenches and vias

InactiveUS6605197B1Vacuum evaporation coatingSemiconductor/solid-state device manufacturingSputteringEvaporation

The present disclosure pertains to a method of filling features (typically trenches or vias) on a semiconductor workpiece surface with copper using sputtering techniques previously believed incapable of achieving a copper fill. In particular, when the feature is to be filled with a single, continuous application of sputtered copper, the surface of the substrate to which the sputtered copper is applied should range between about 200° C. and about 600° C.; preferably the surface temperature of the substrate ranges between about 300° C. and about 500° C. When the feature is to be filled using a thin wetting layer of copper, followed by a fill layer of copper, the wetting layer may be applied by sputtering techniques or by other methods such as evaporation or CVD, while the fill layer of copper is applied using sputtering techniques. The thin wetting layer of copper is applied at a substrate surface temperature ranging between about 20° C. to about 250° C., and subsequently the temperature of the substrate is increased, with the application of the sputtered copper fill layer beginning at above at least about 200° C. and continuing while the substrate temperature is increased to a temperature as high as about 600° C. Preferably the substrate temperature during application of the sputtered fill layer ranges between about 300° C. and about 500° C.

Owner:APPLIED MATERIALS INC

Damage-free sculptured coating deposition

We disclose a method of applying a sculptured layer of material on a semiconductor feature surface using ion deposition sputtering, wherein a surface onto which the sculptured layer is applied is protected to resist erosion and contamination by impacting ions of a depositing layer. A first protective layer of material is deposited on a substrate surface using traditional sputtering or ion deposition sputtering, in combination with sufficiently low substrate bias that a surface onto which the layer is applied is not eroded away or contaminated during deposition of the protective layer. Subsequently, a sculptured second layer of material is applied using ion deposition sputtering at an increased substrate bias, to sculpture a shape from a portion of the first protective layer of material and the second layer of depositing material. The method is particularly applicable to the sculpturing of barrier layers, wetting layers, and conductive layers upon semiconductor feature surfaces.

Owner:APPLIED MATERIALS INC

Electronic assembly having an indium wetting layer on a thermally conductive body

ActiveUS7362580B2Semiconductor/solid-state device detailsSolid-state devicesIndiumElectronic assemblies

Embodiments include electronic packages and methods for forming electronic packages. One method includes providing a die and a thermal interface material on the die. A metal body is adapted to fit over the die. A wetting layer of a material comprising indium is formed on the metal body. The thermal interface material on the die is brought into contact with the wetting layer of material comprising indium. The thermal interface material is heated to form a bond between the thermal interface material and the wetting layer so that the thermal interface material is coupled to the metal body, and to form a bond between the thermal interface material and the die so that the thermal interface material is coupled to the die.

Owner:INTEL CORP

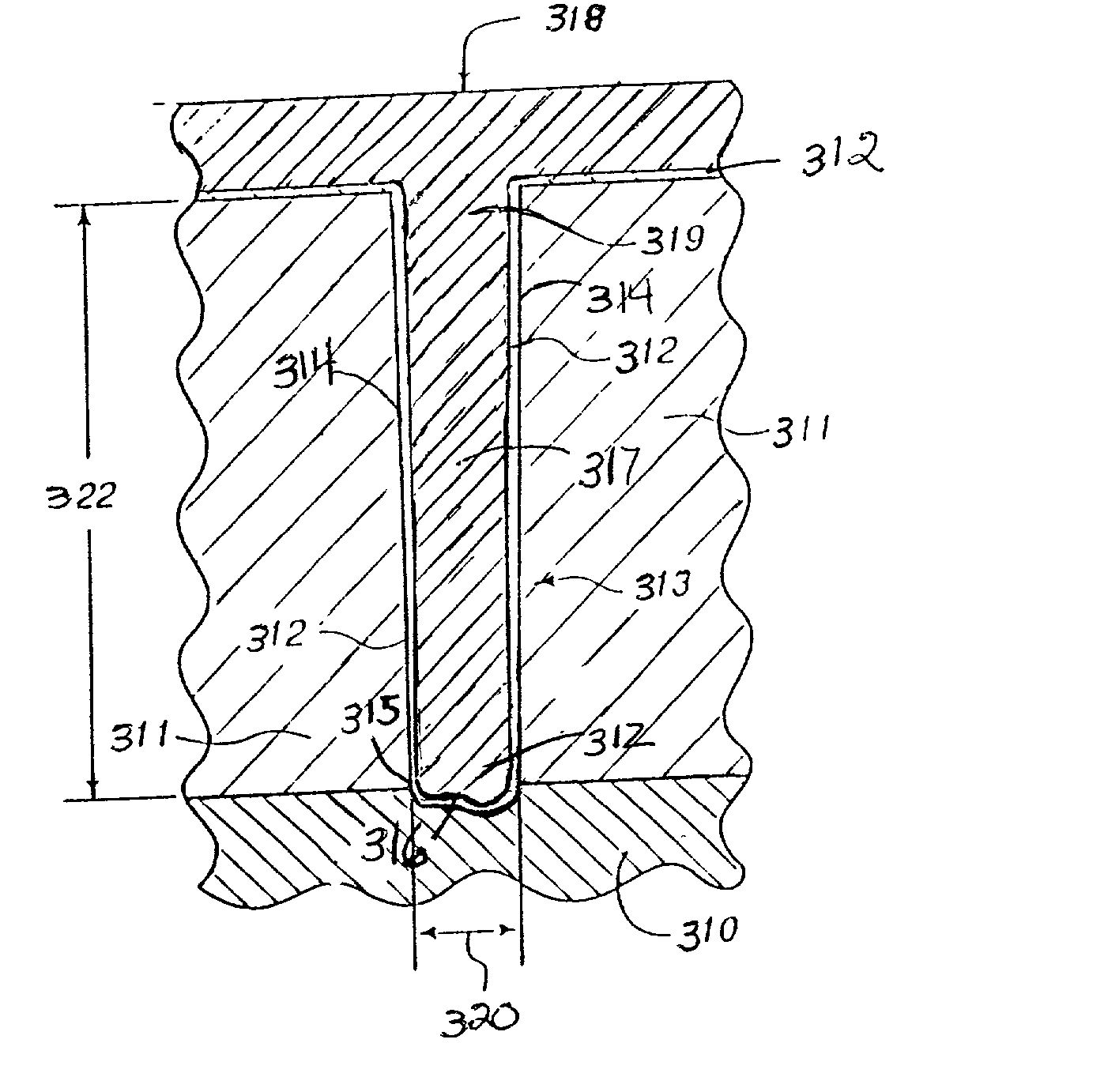

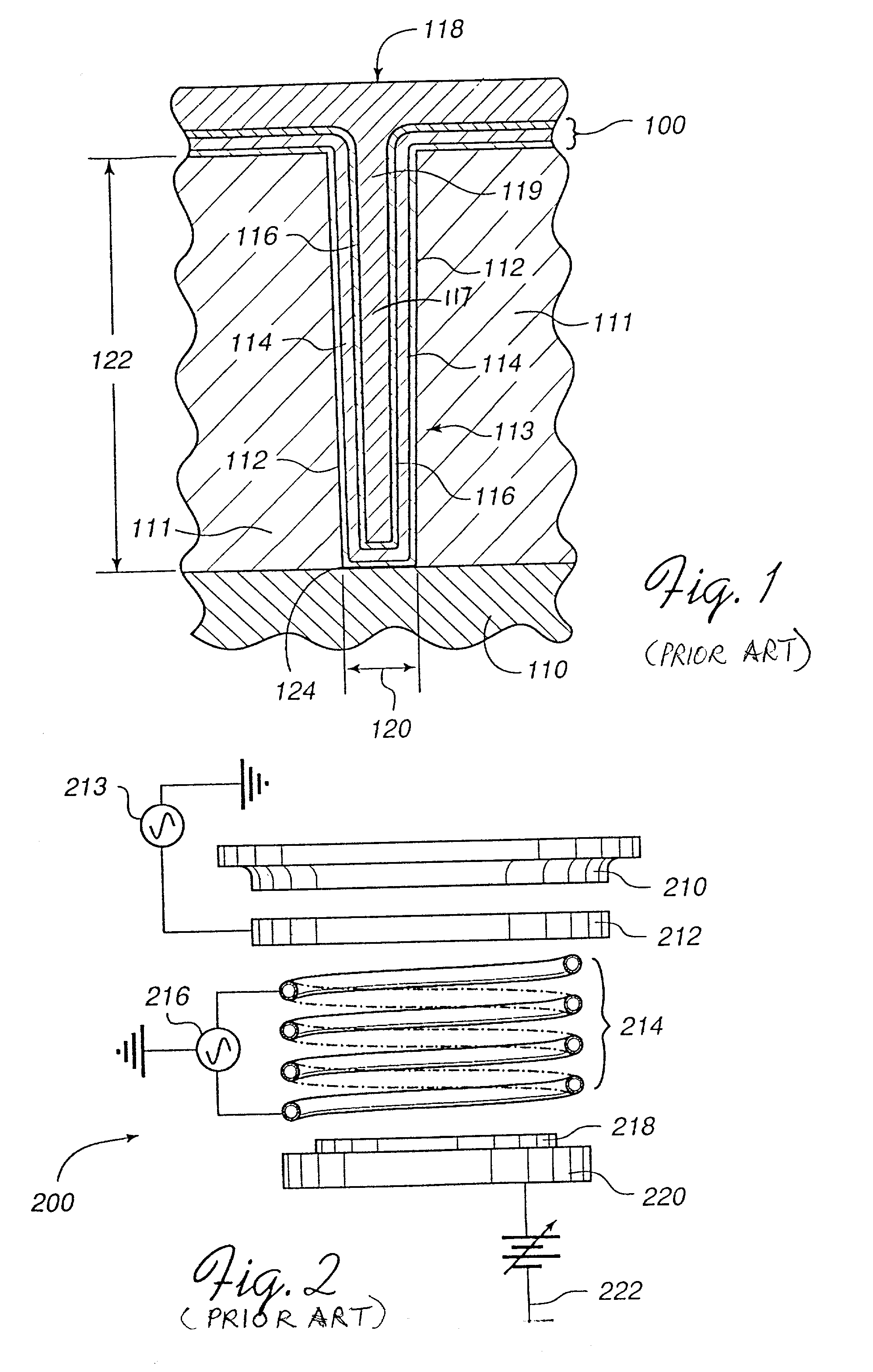

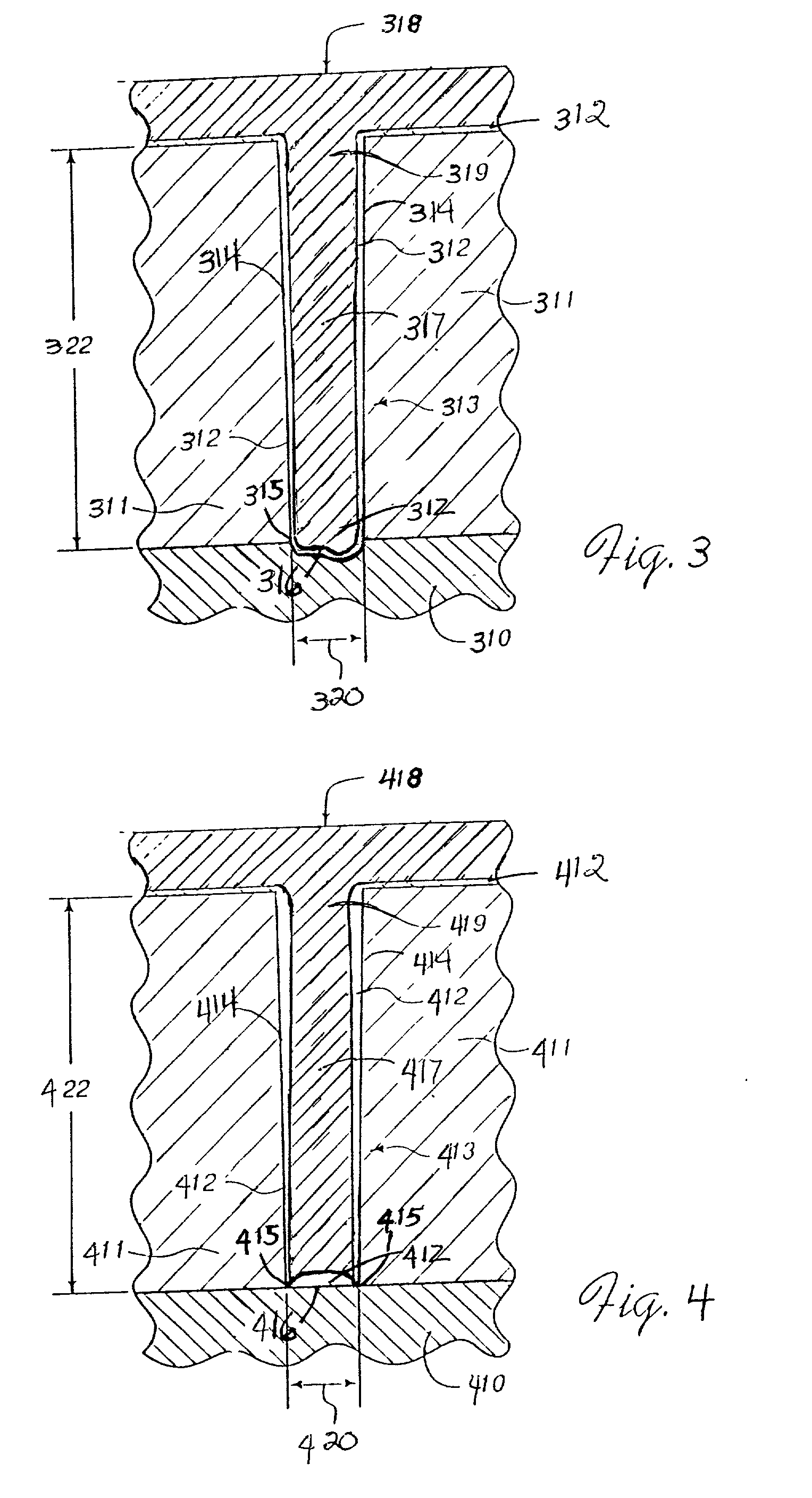

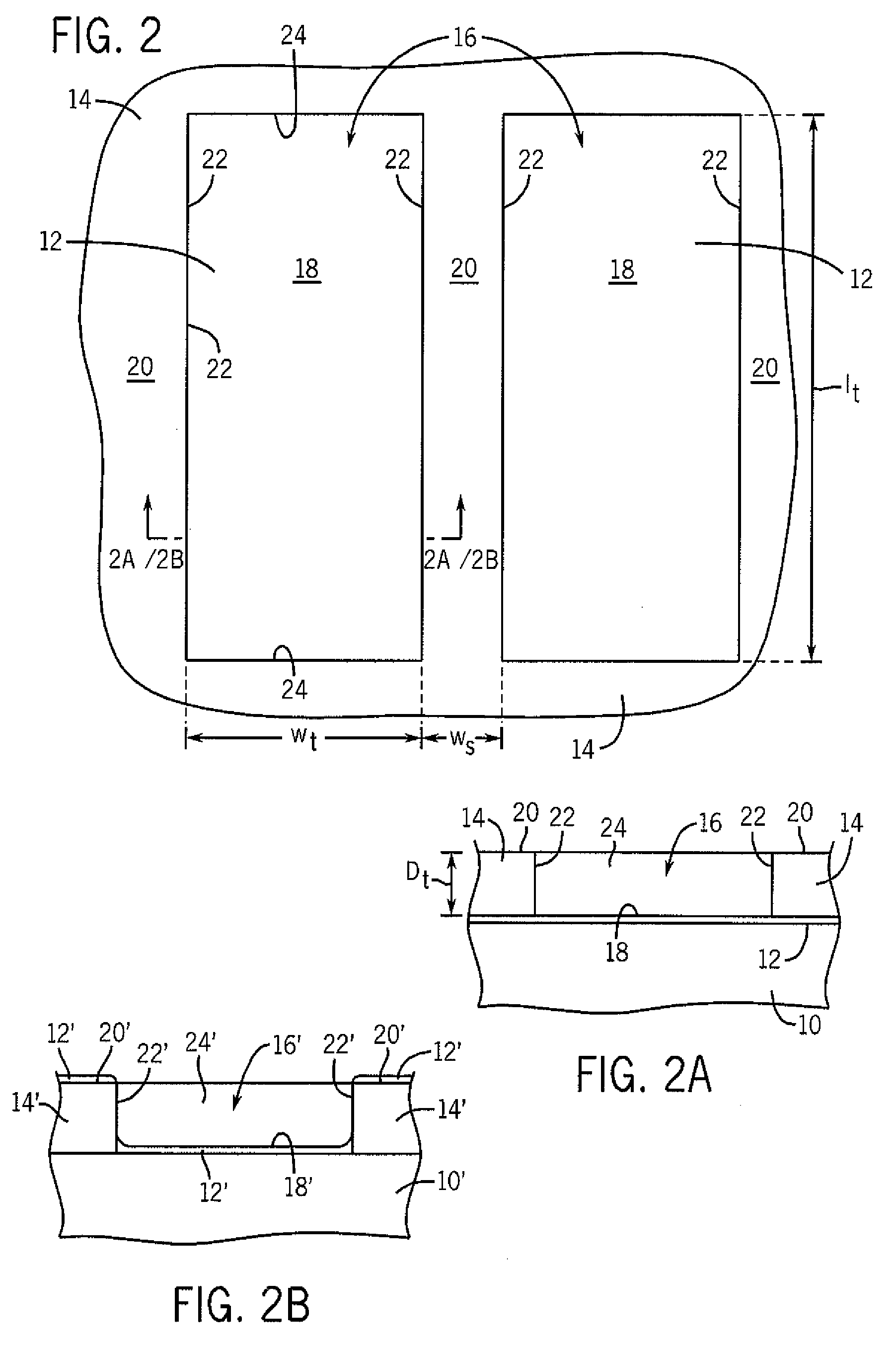

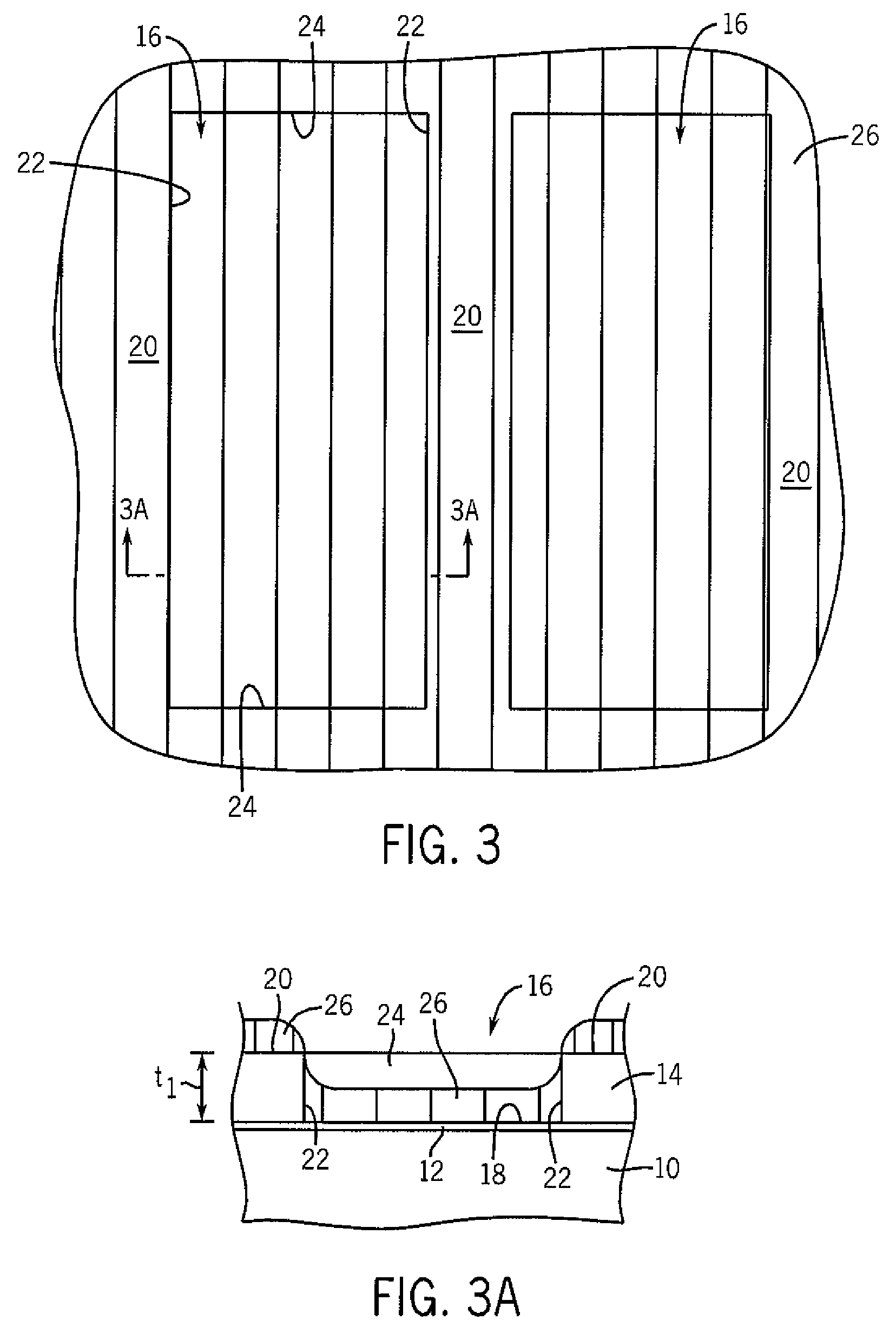

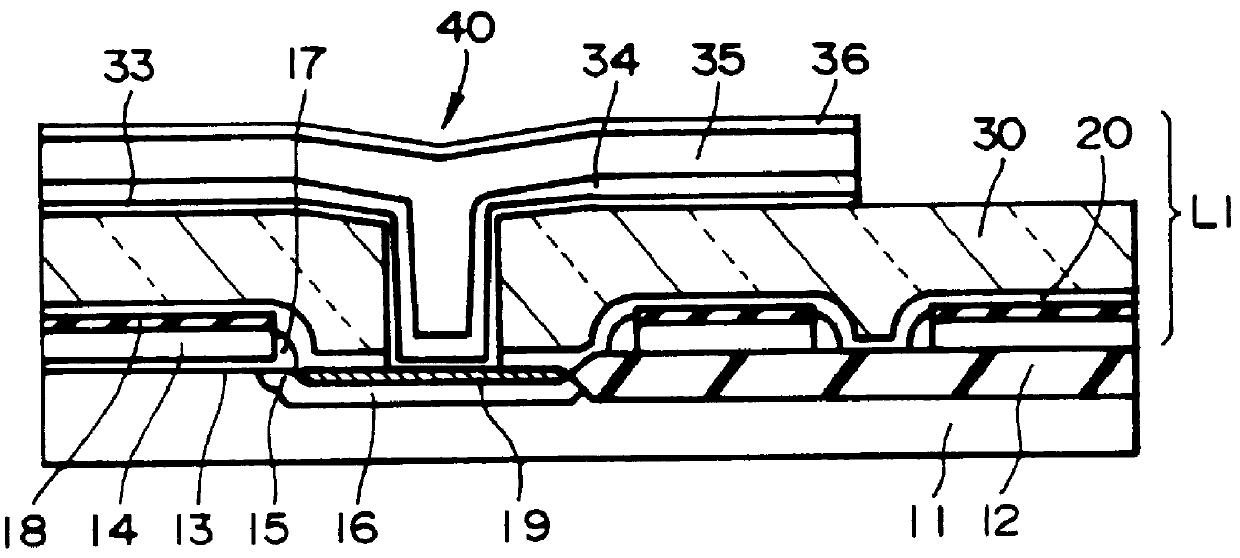

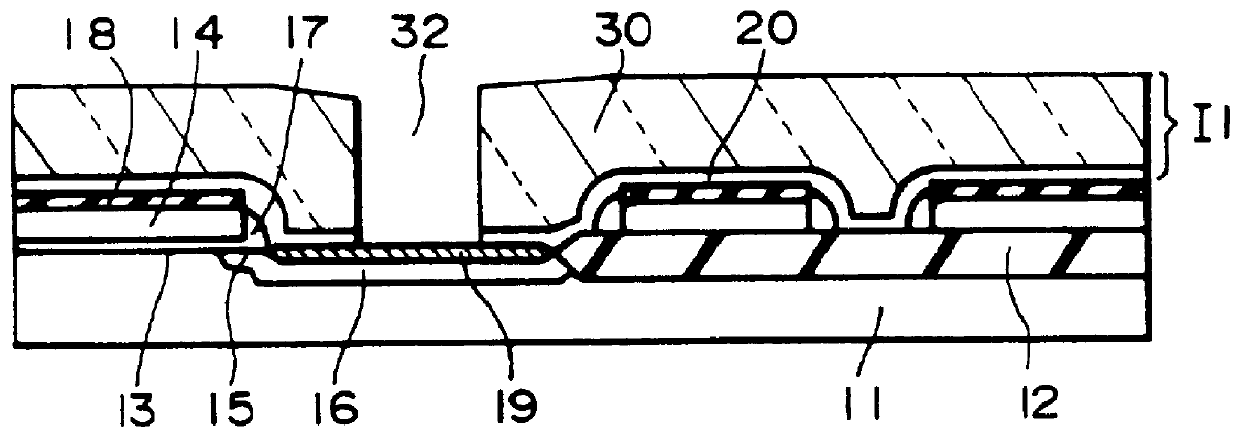

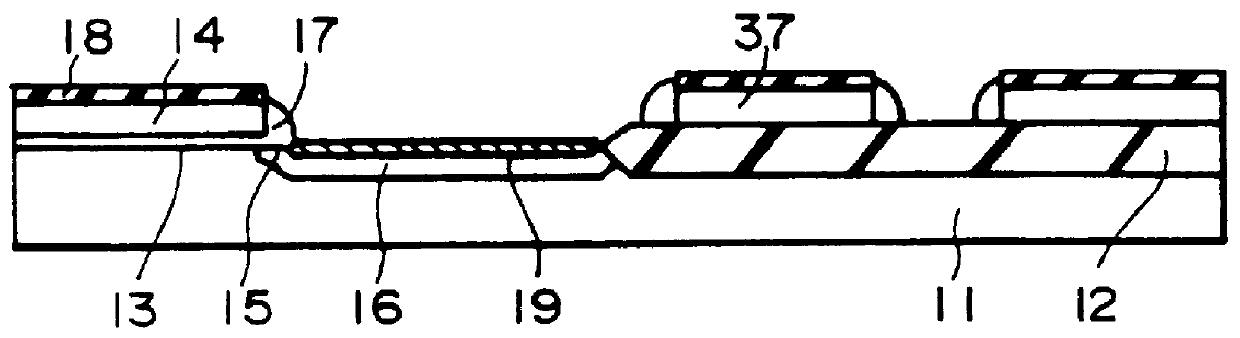

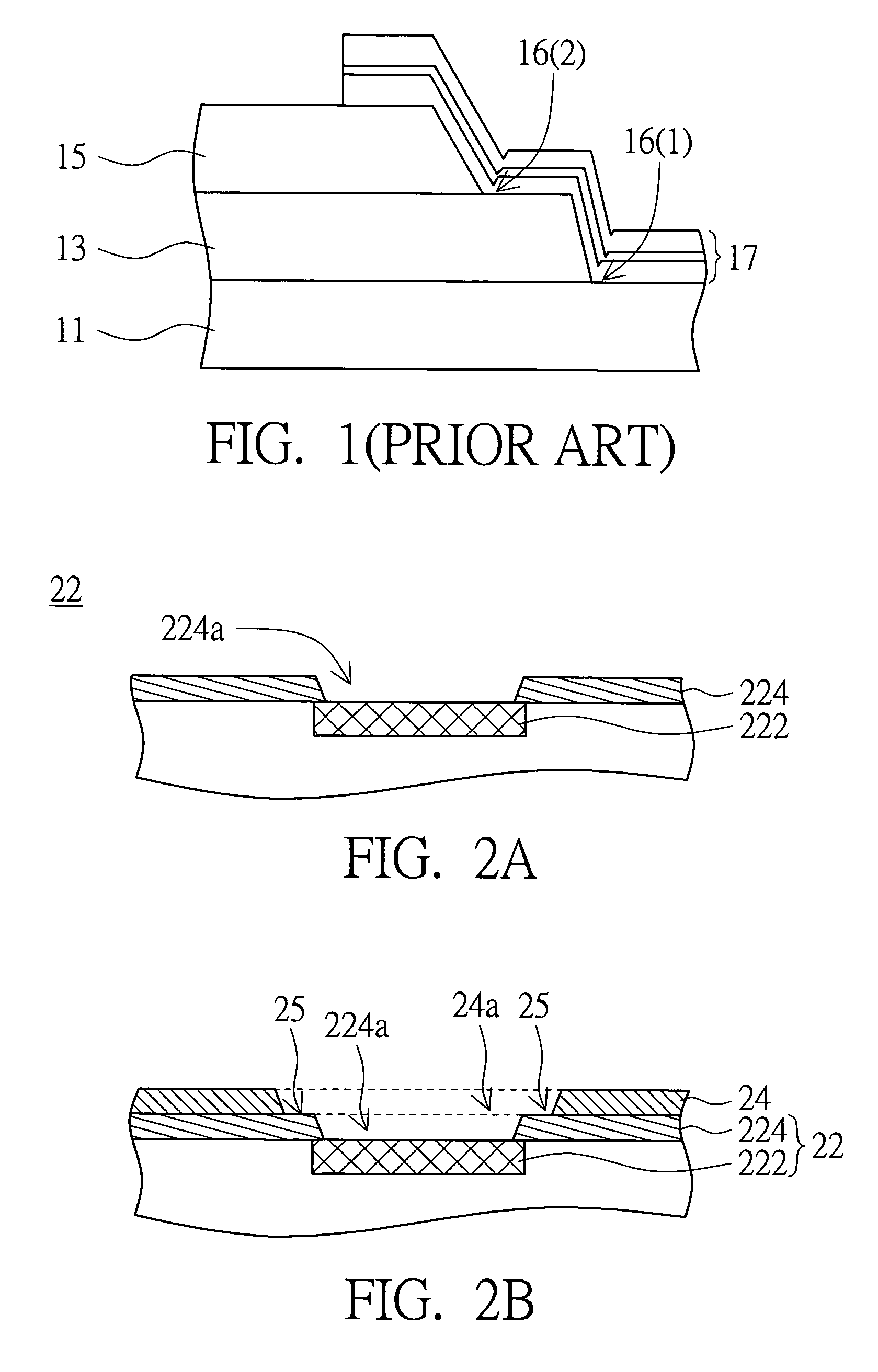

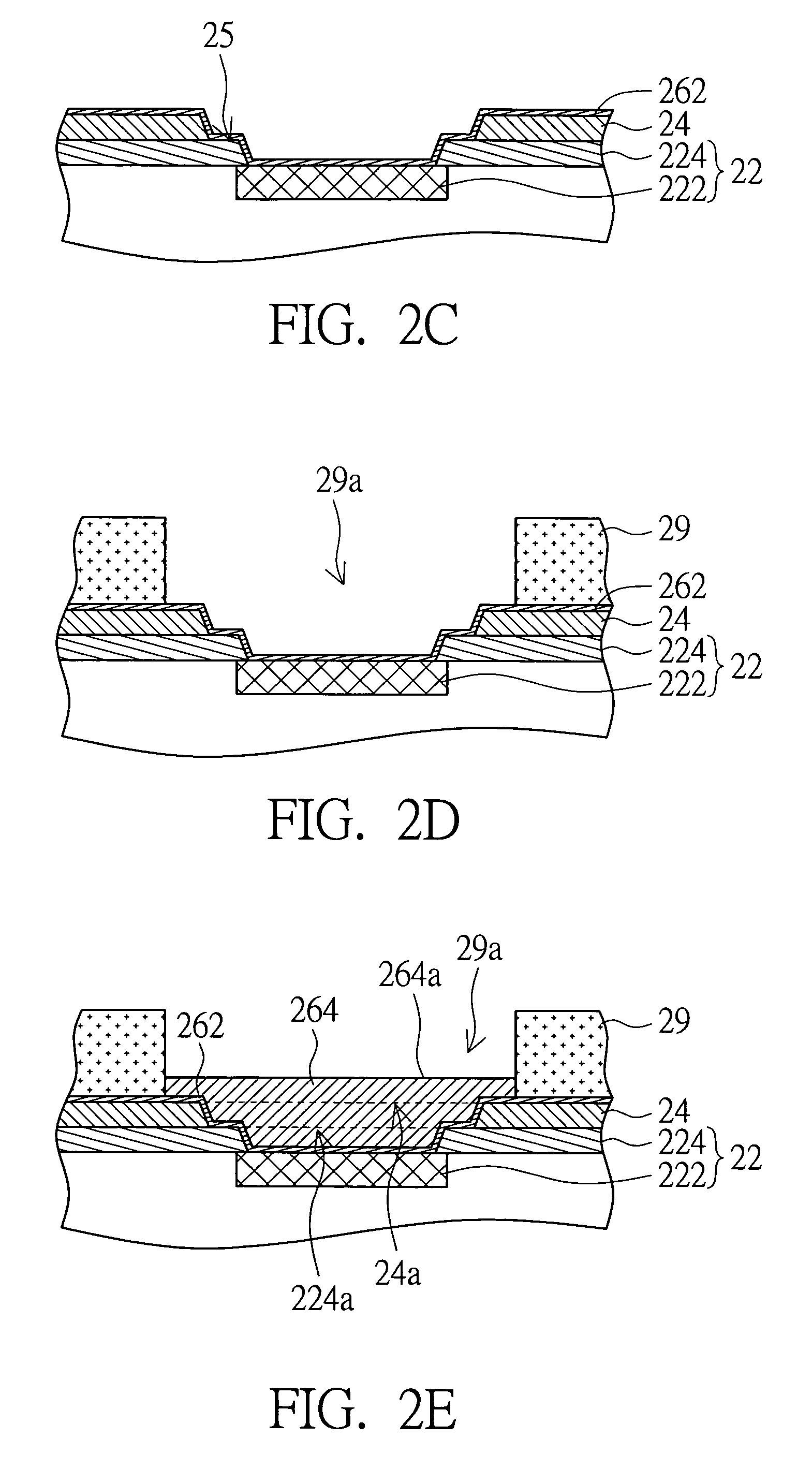

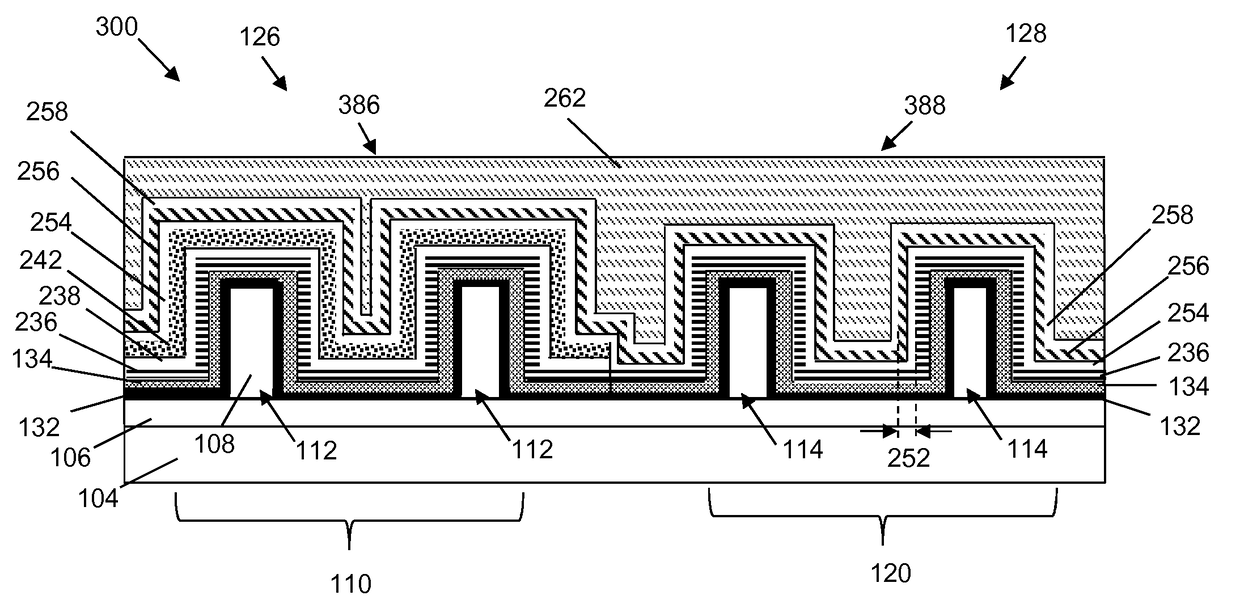

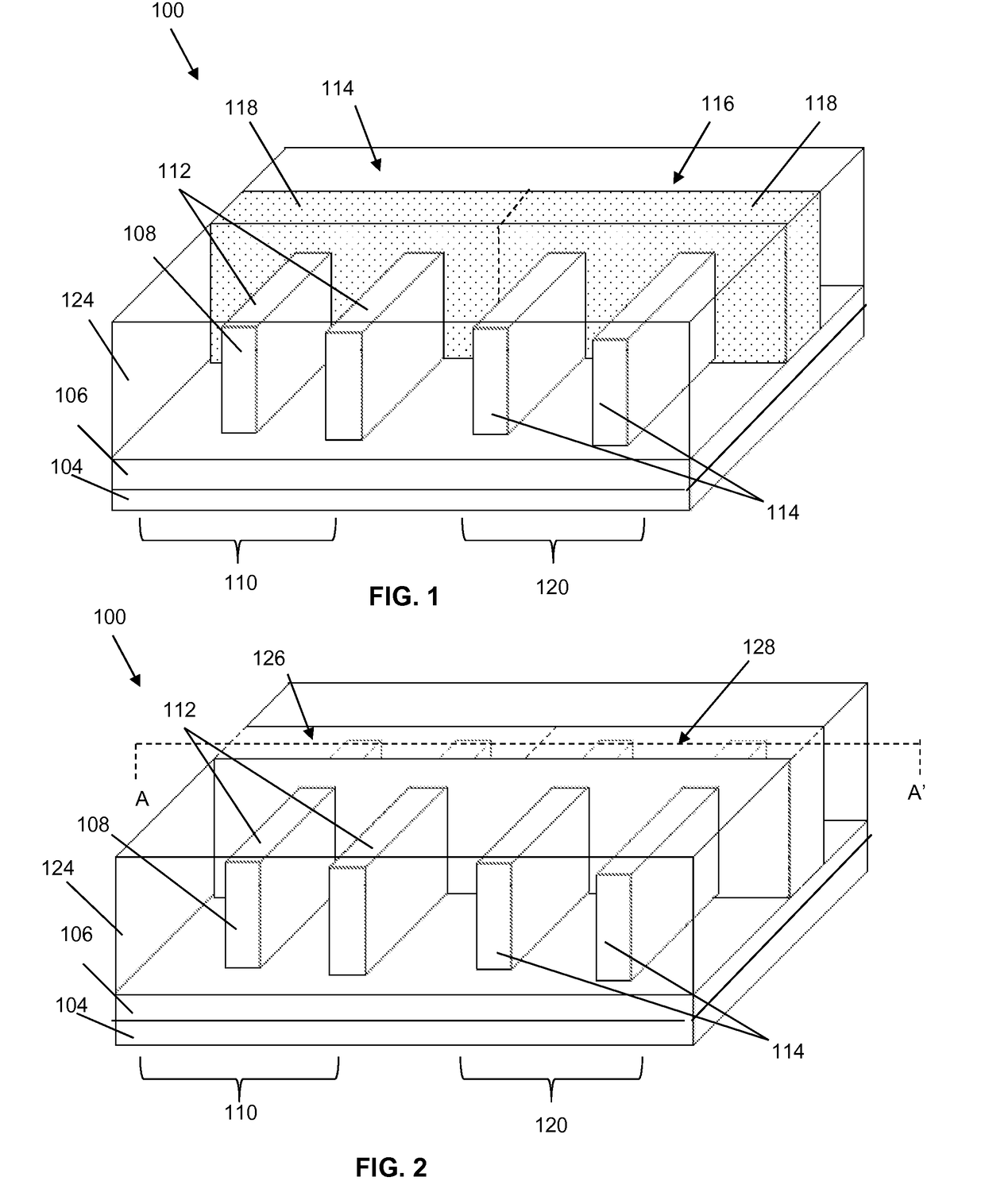

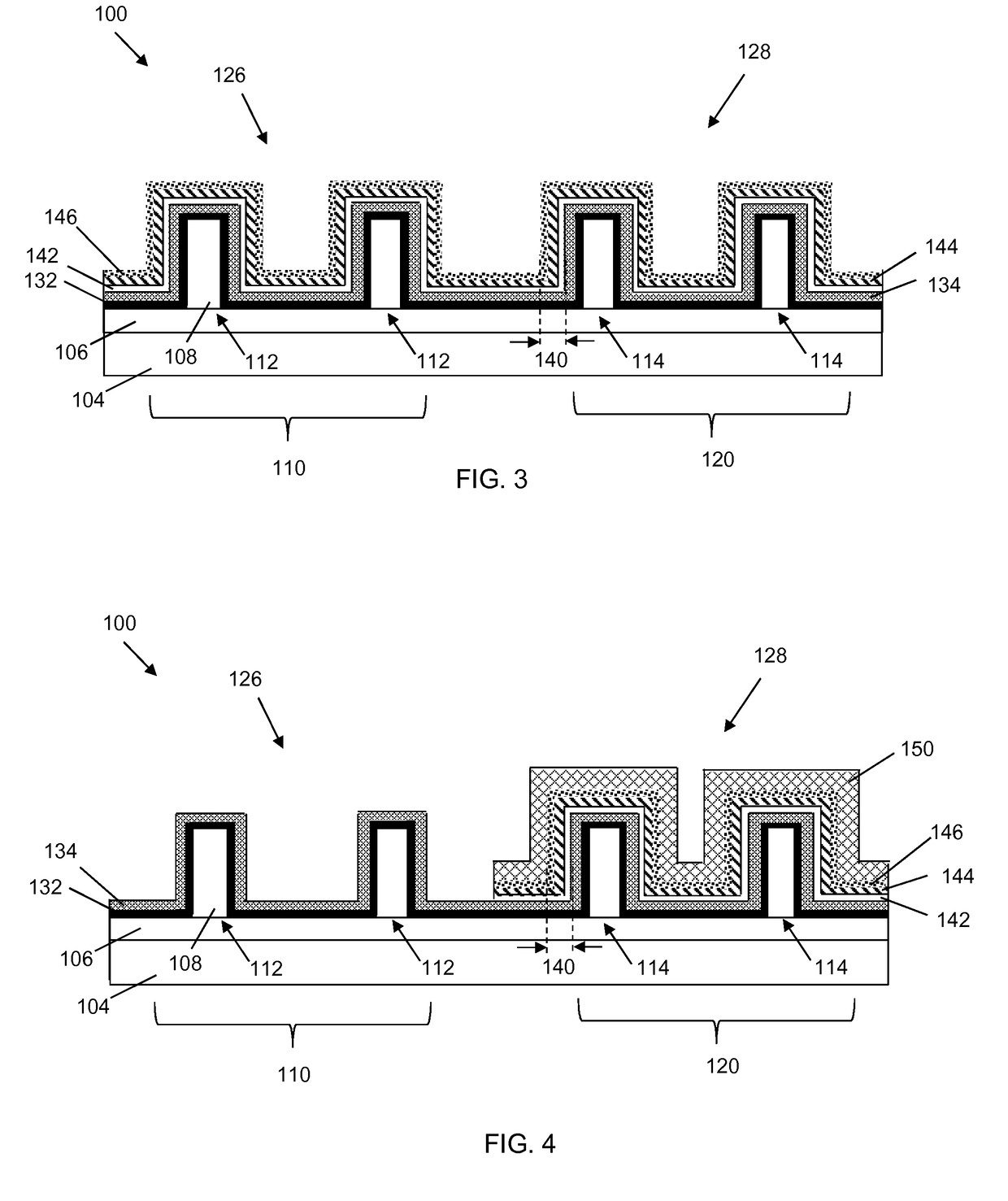

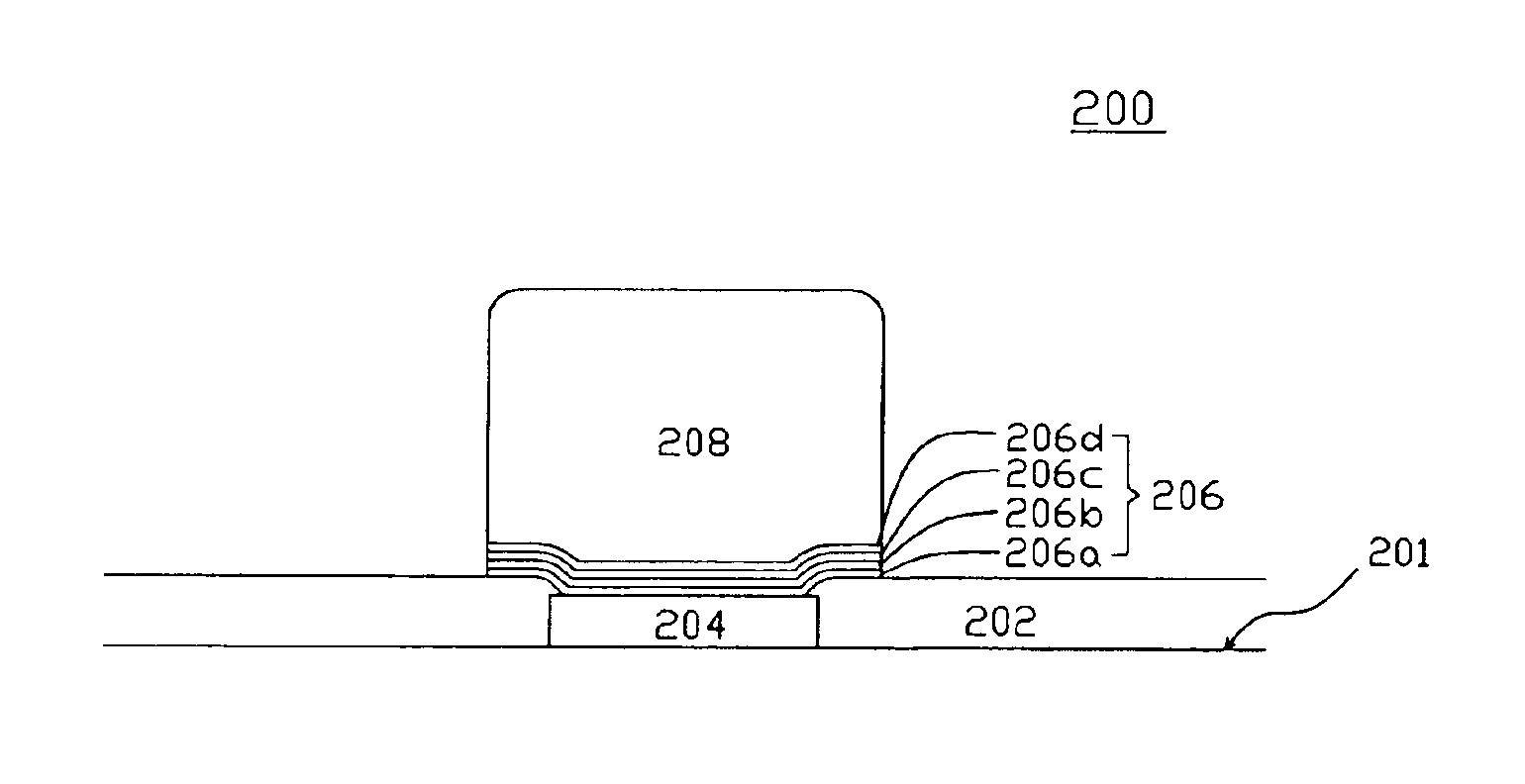

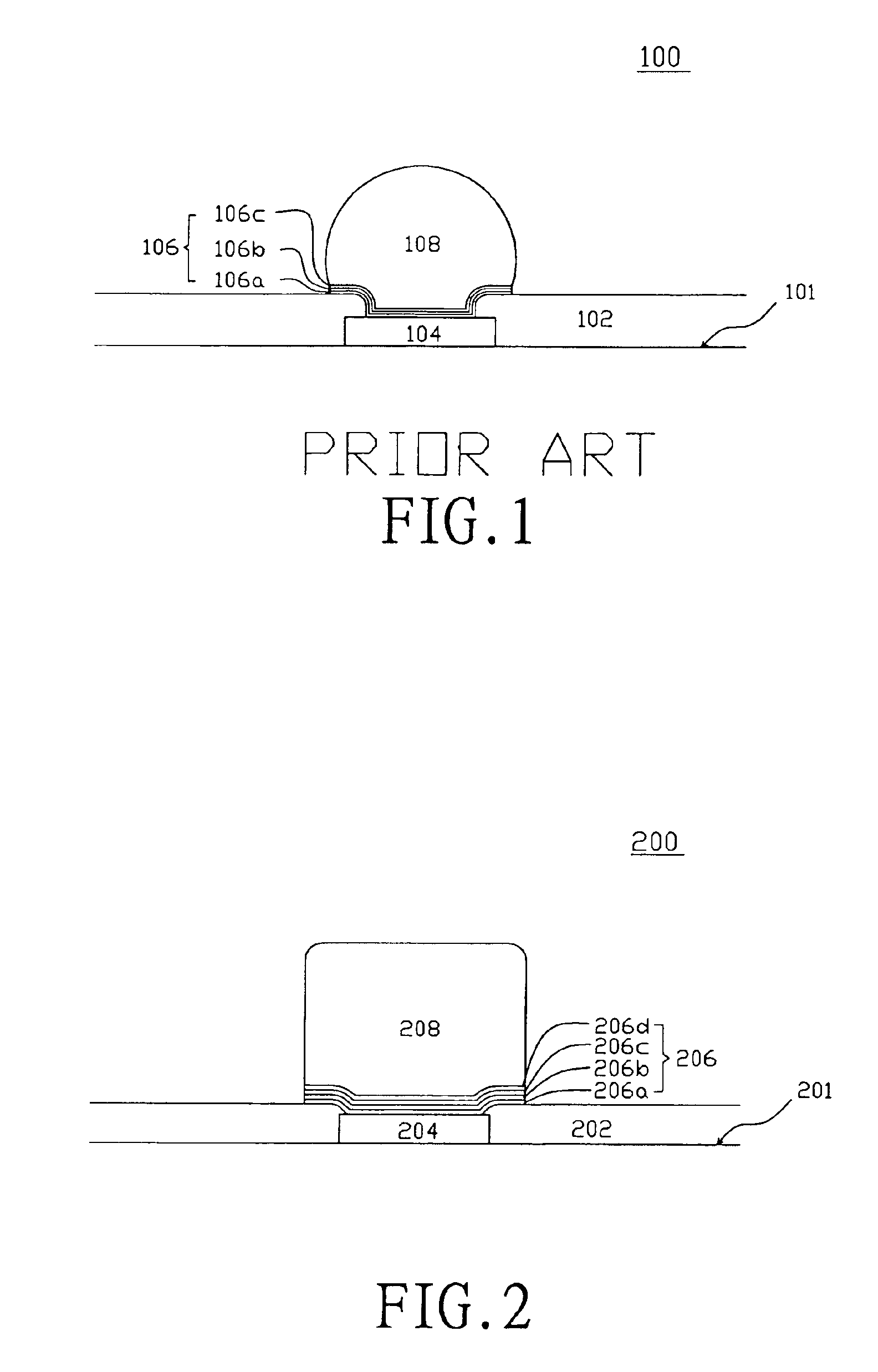

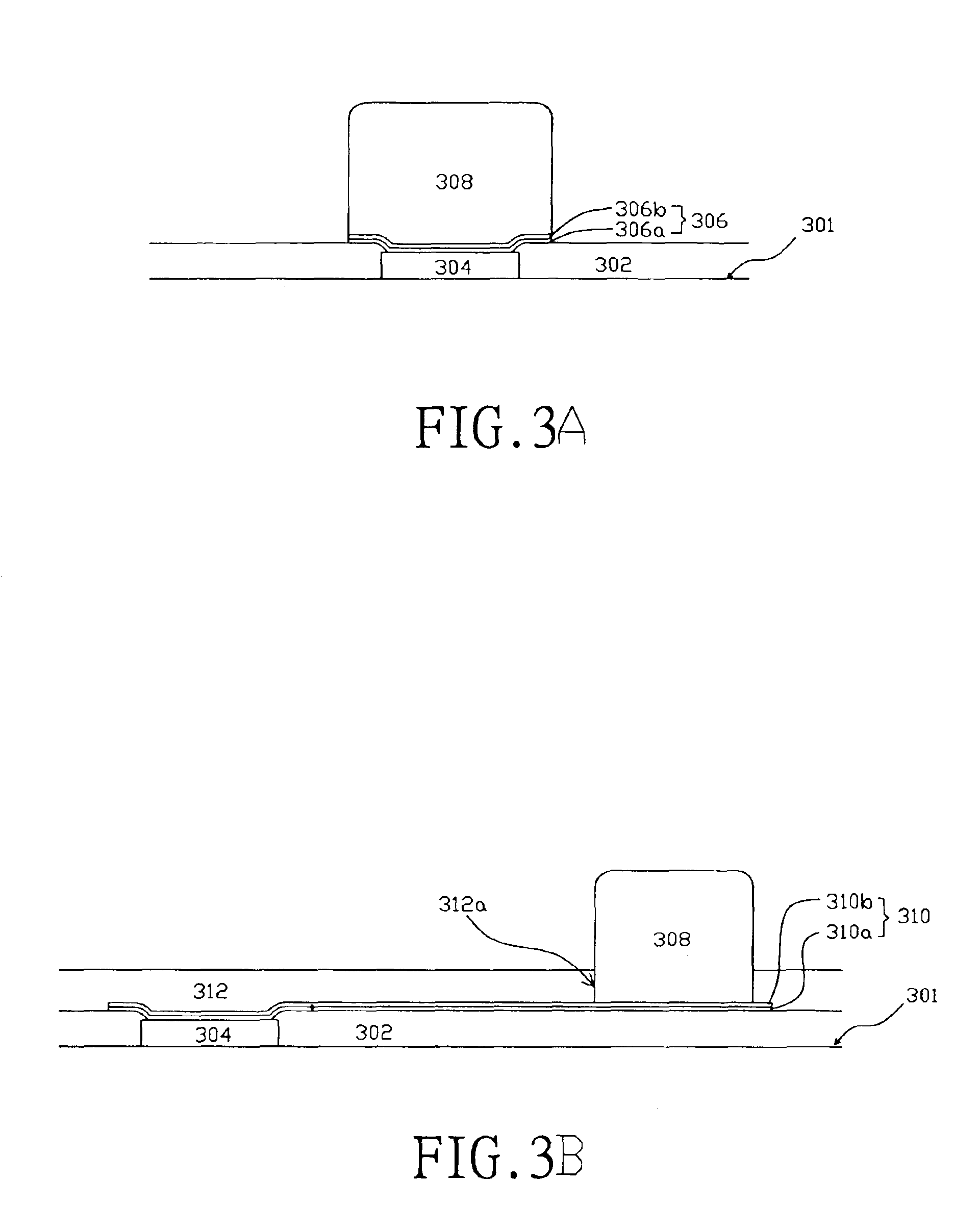

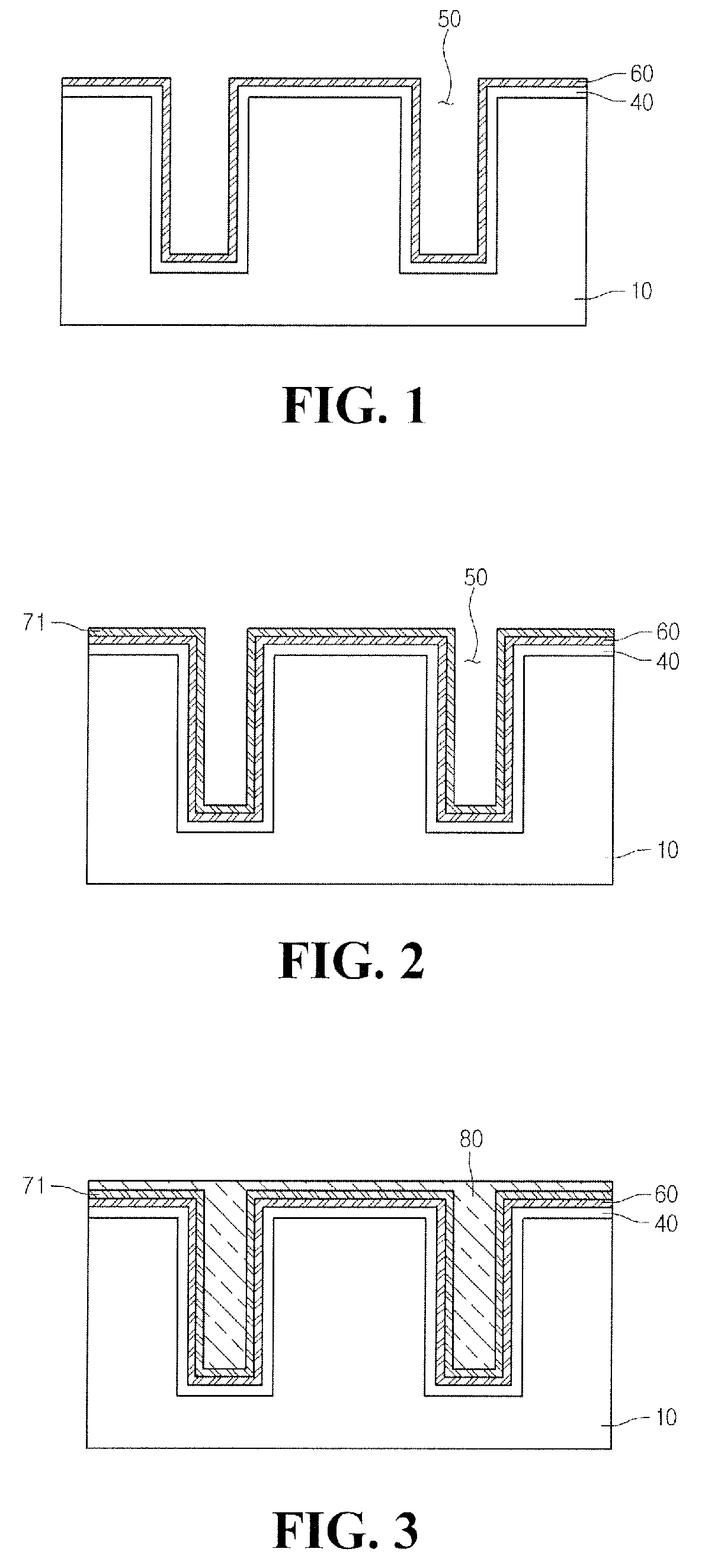

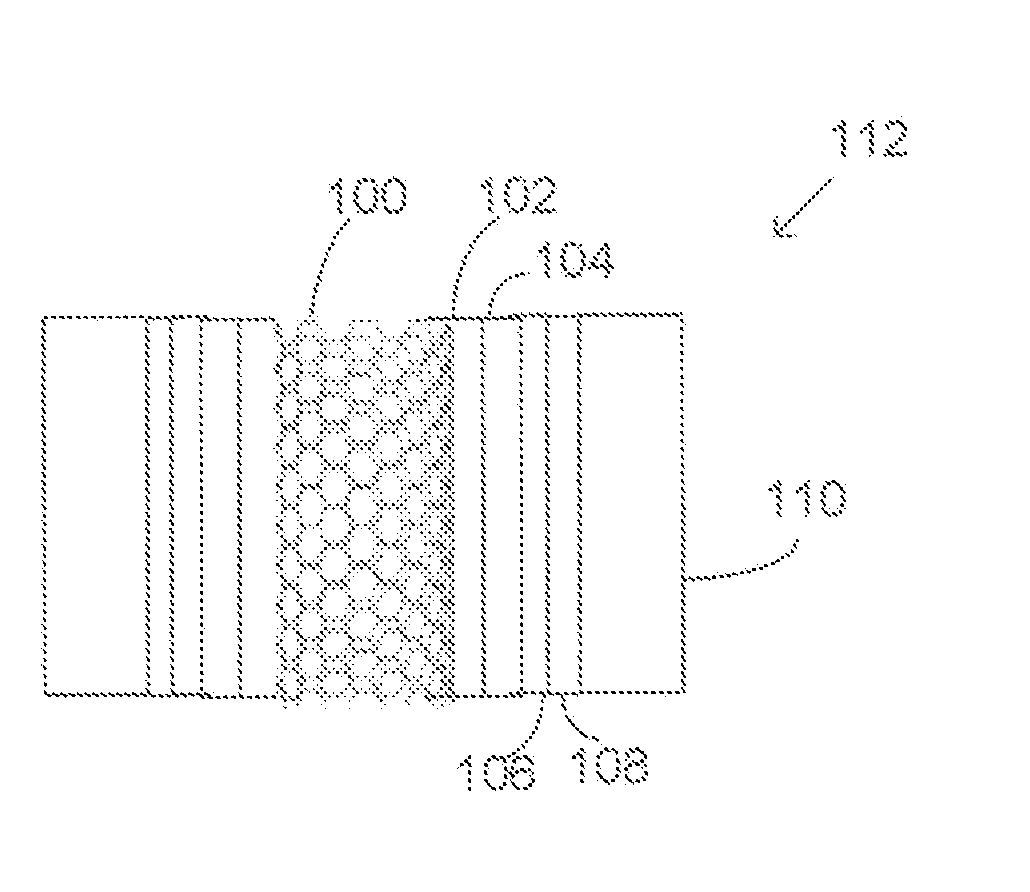

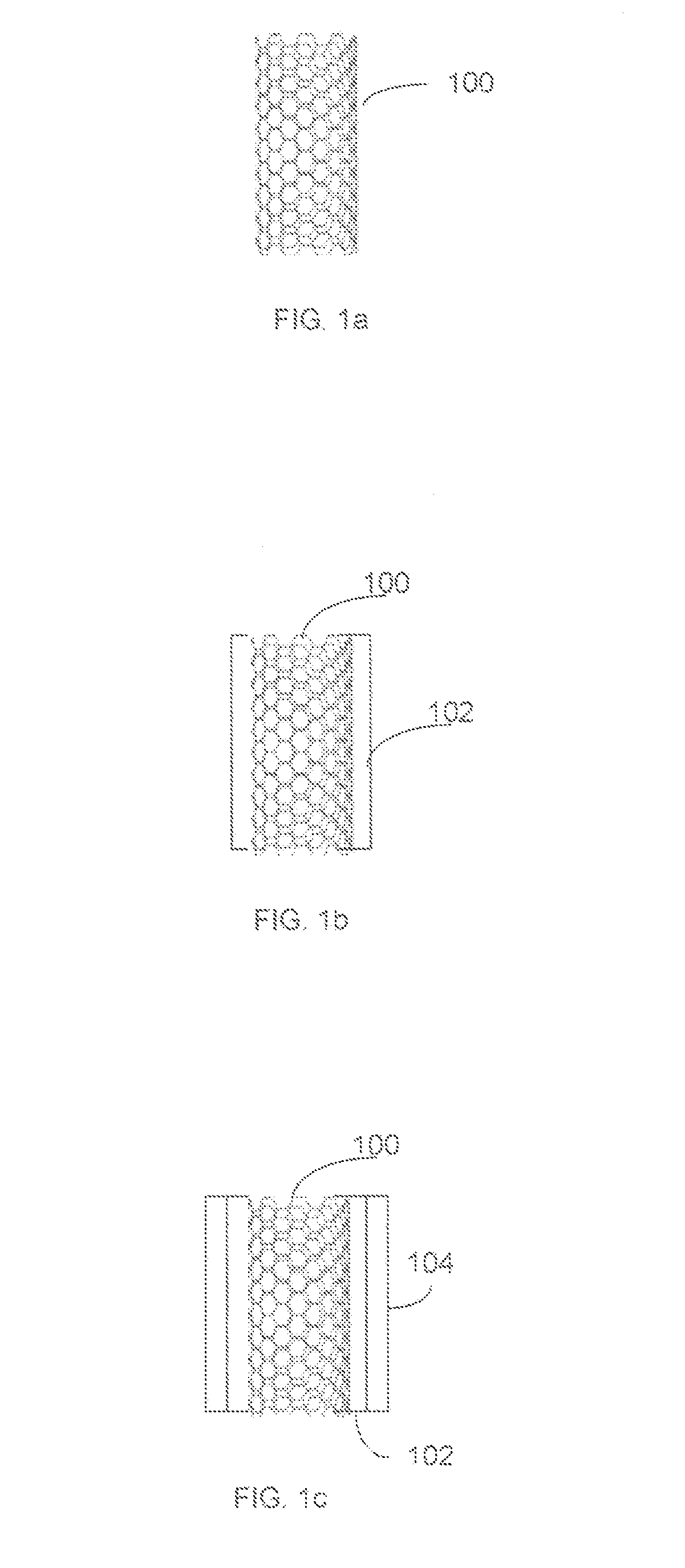

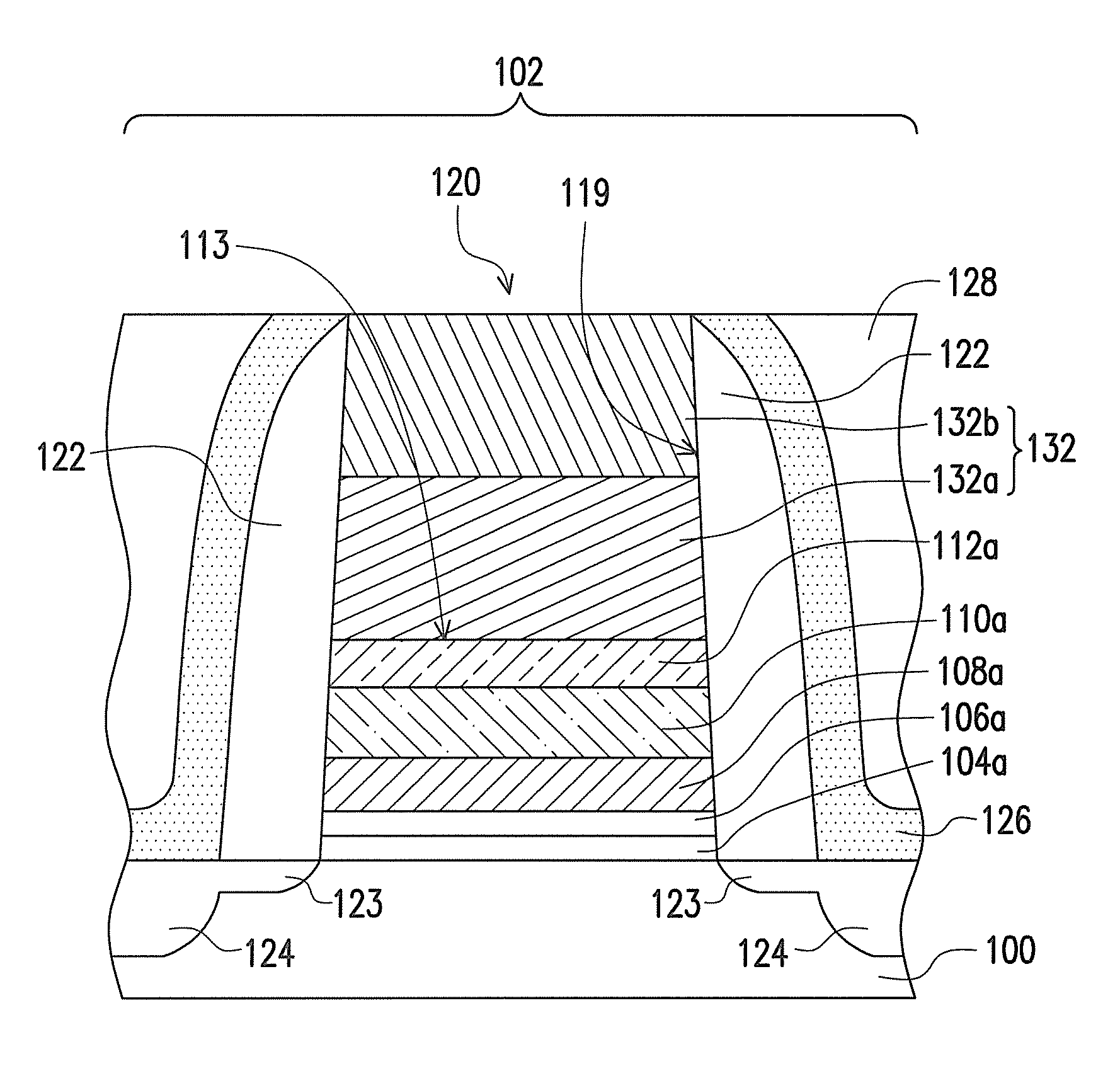

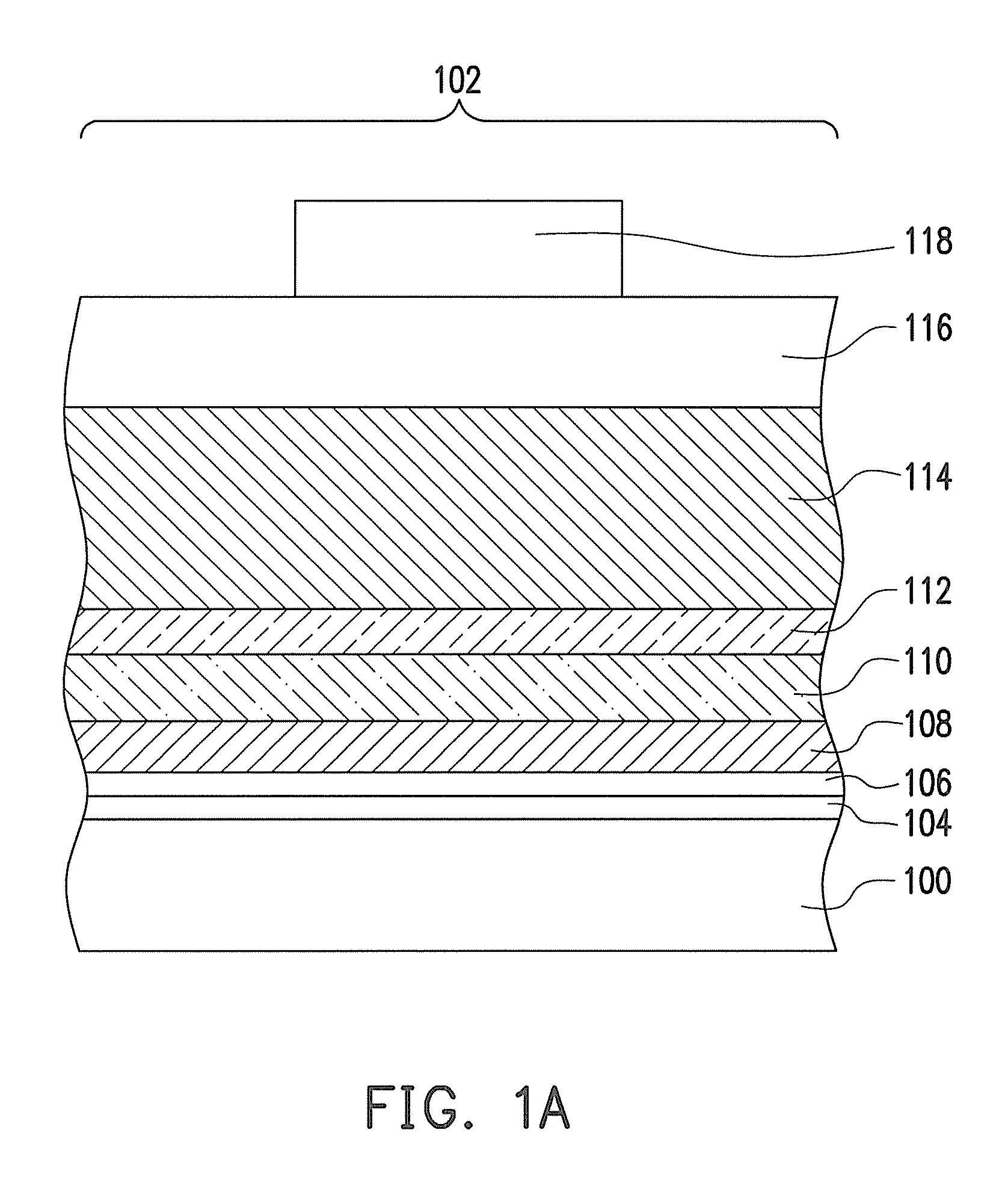

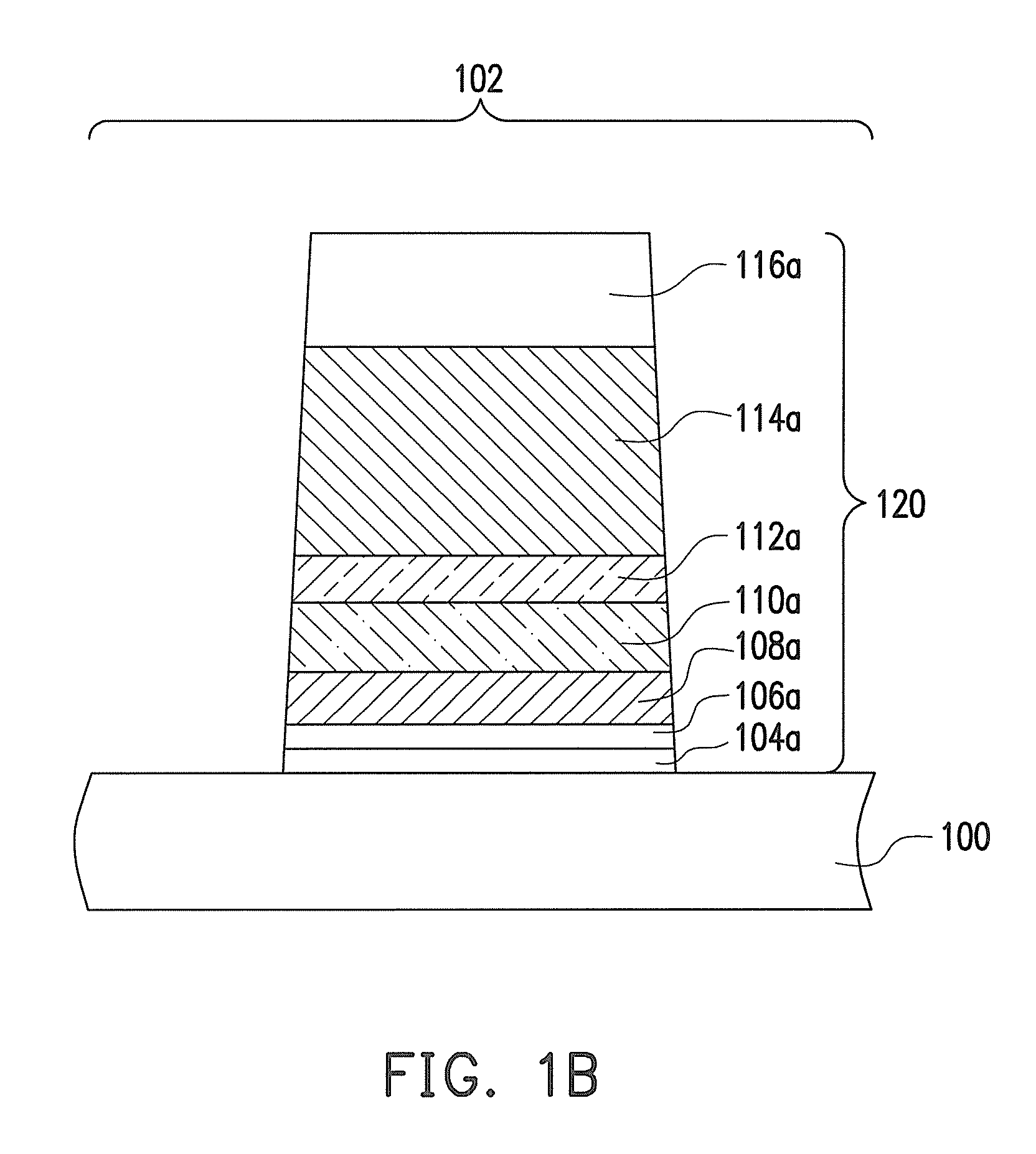

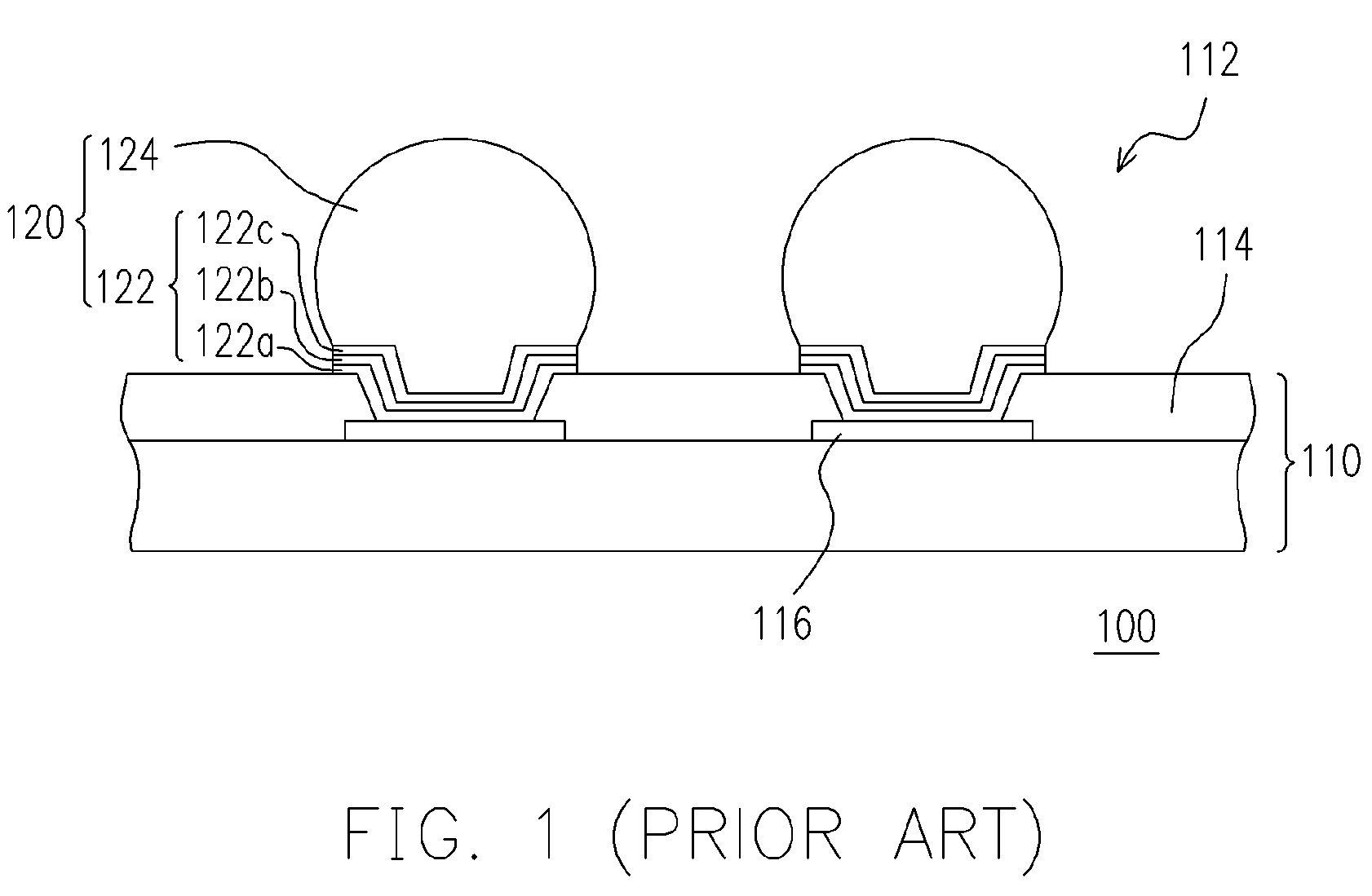

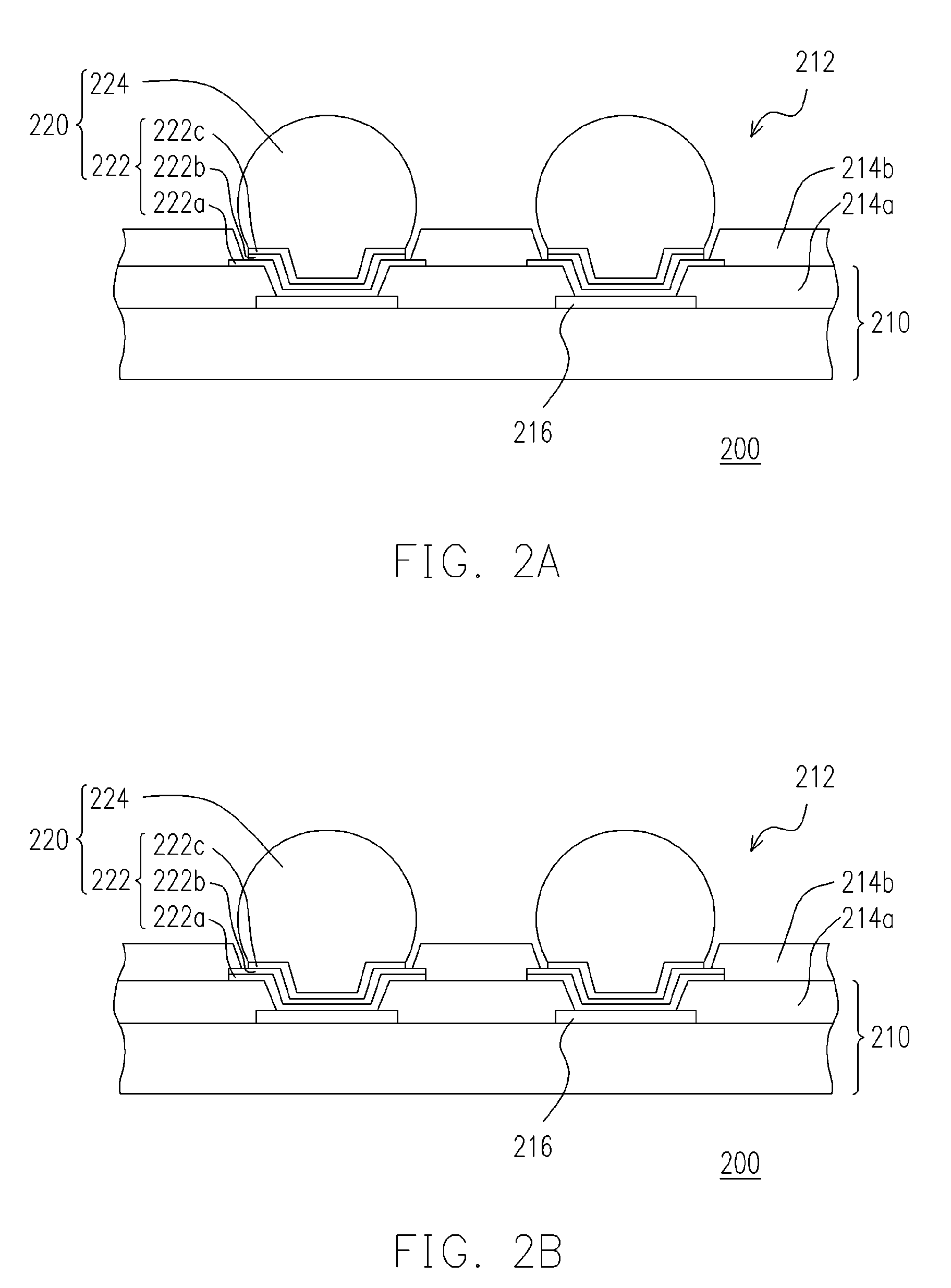

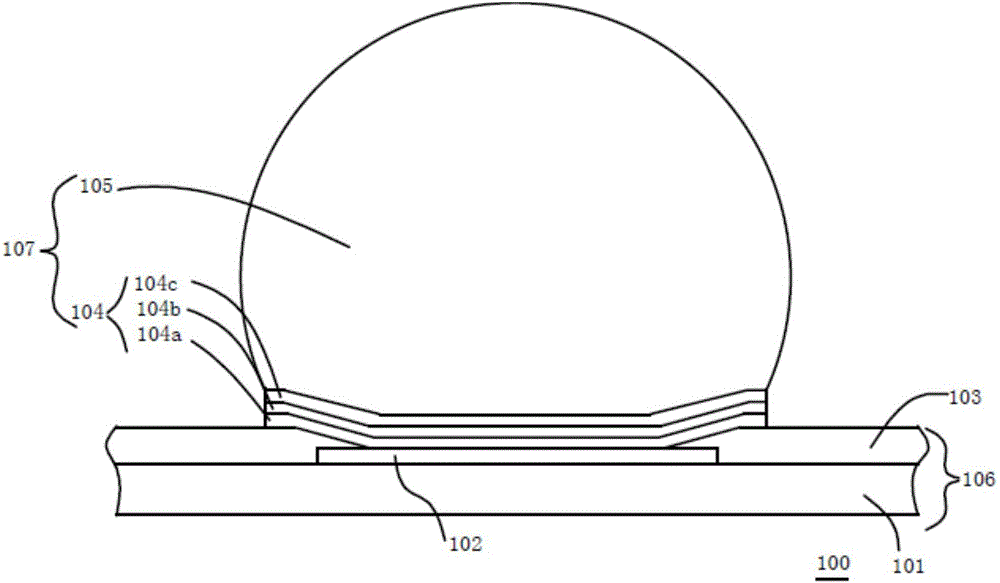

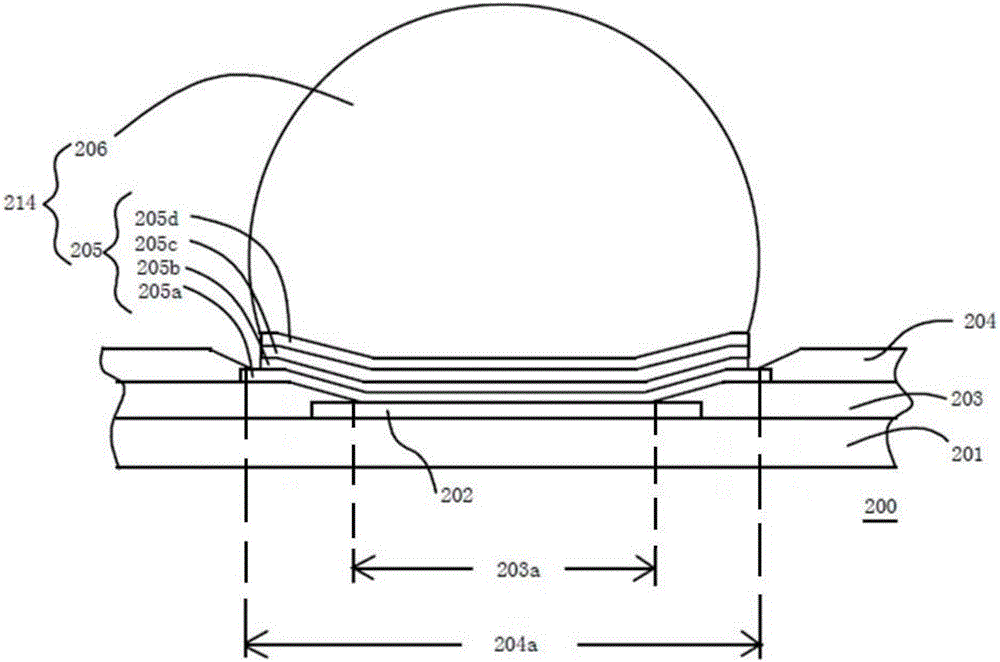

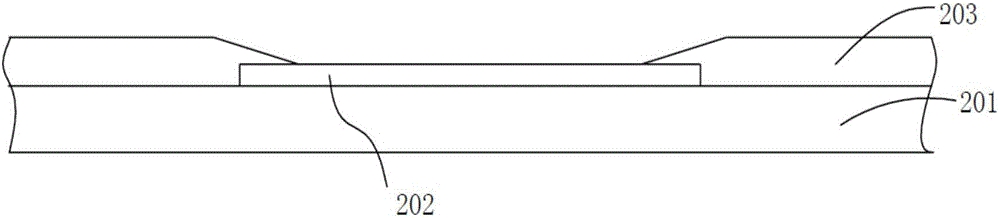

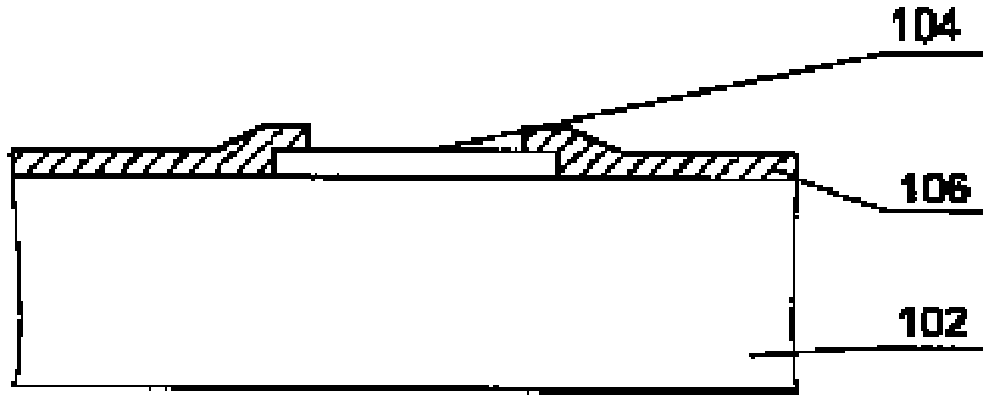

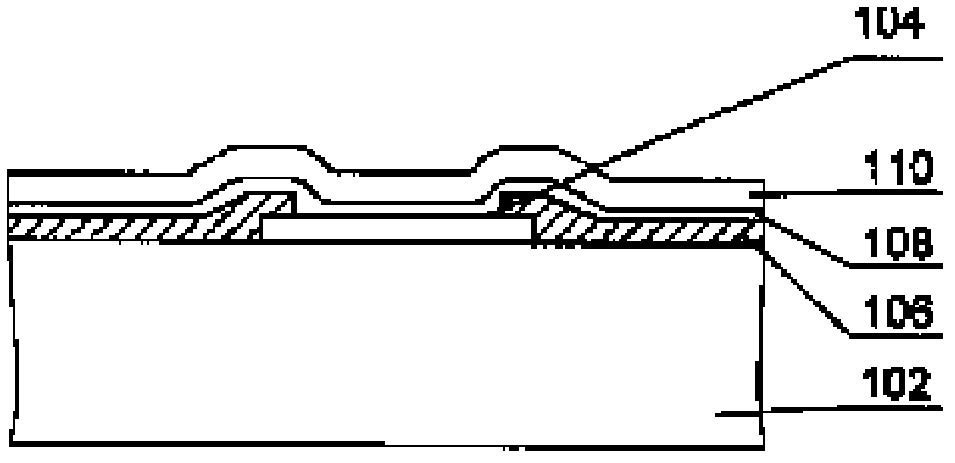

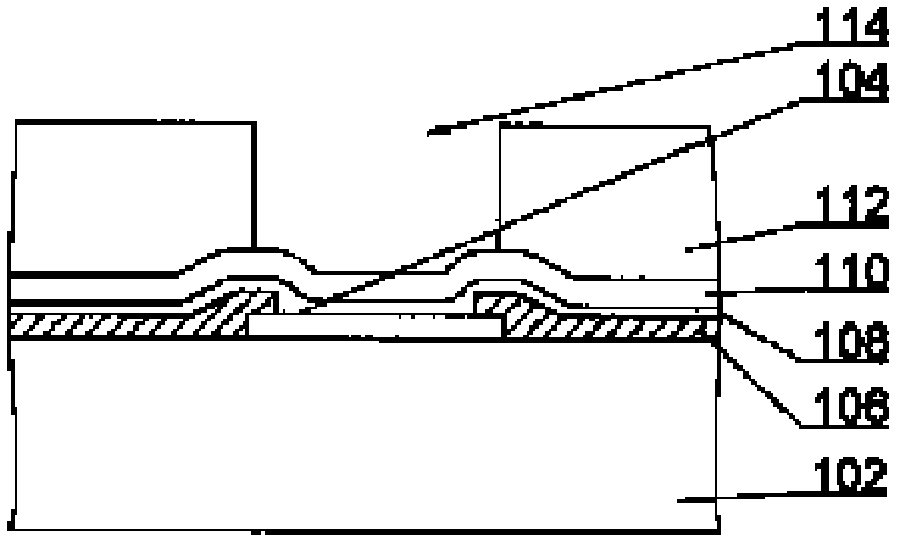

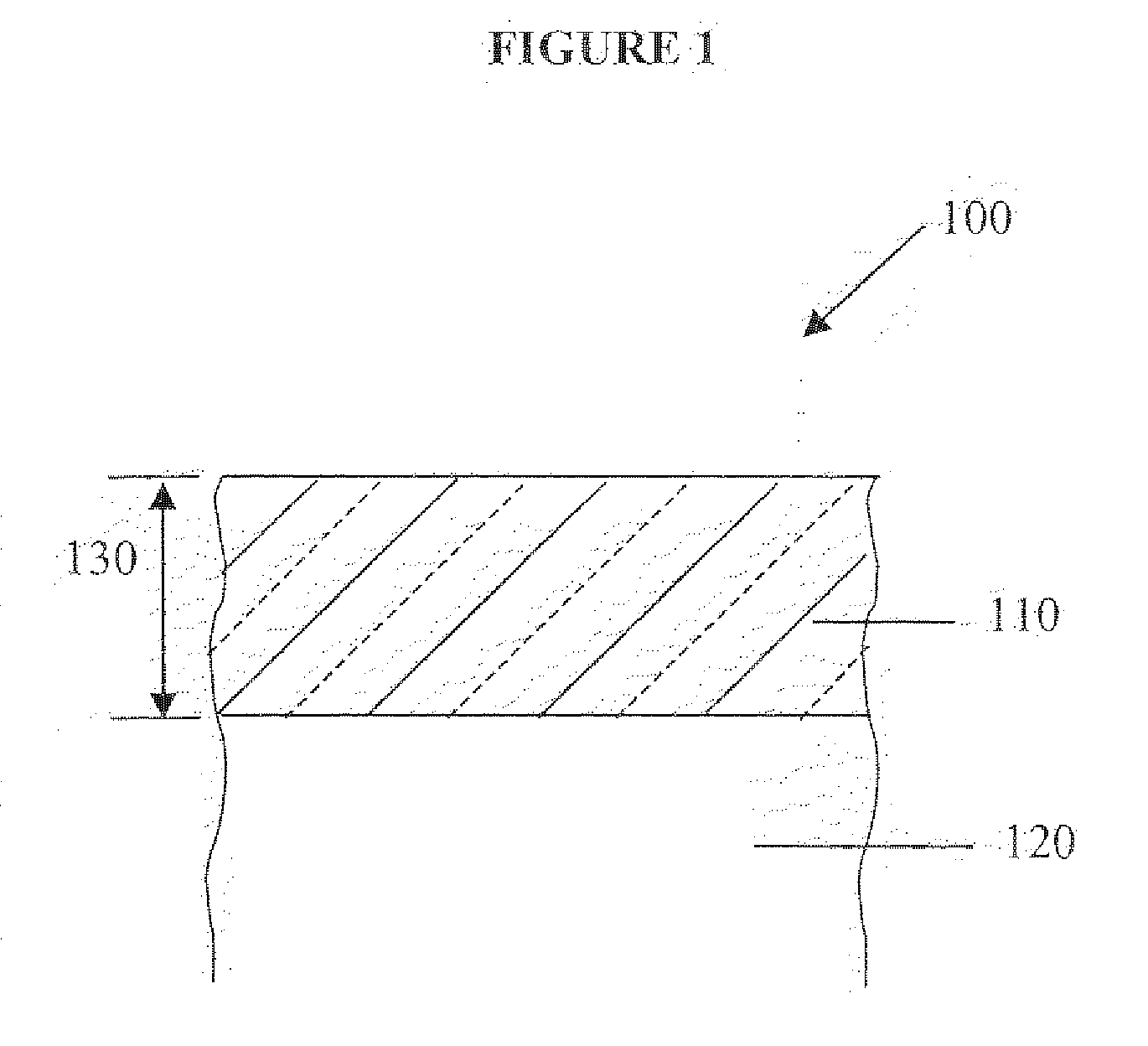

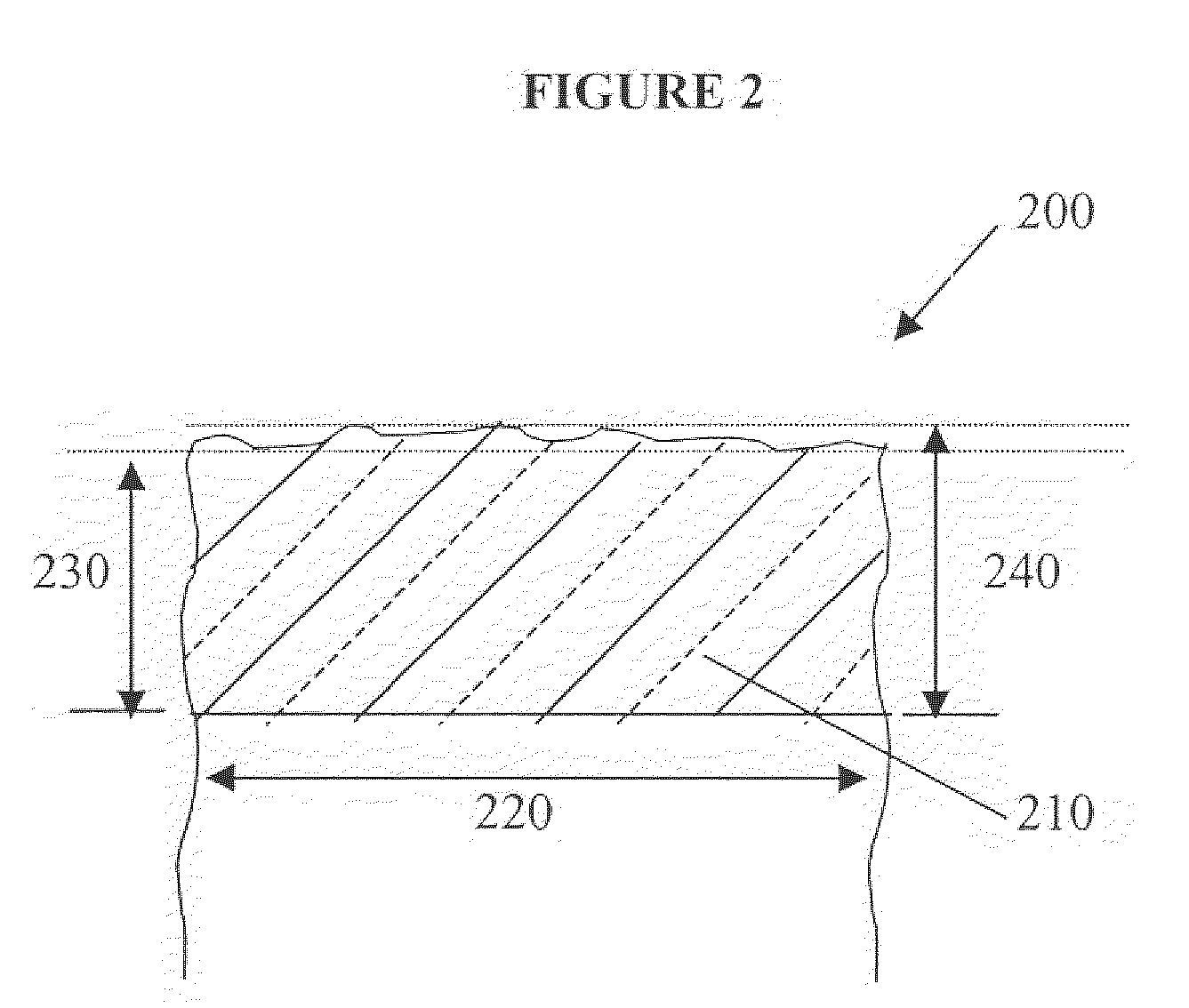

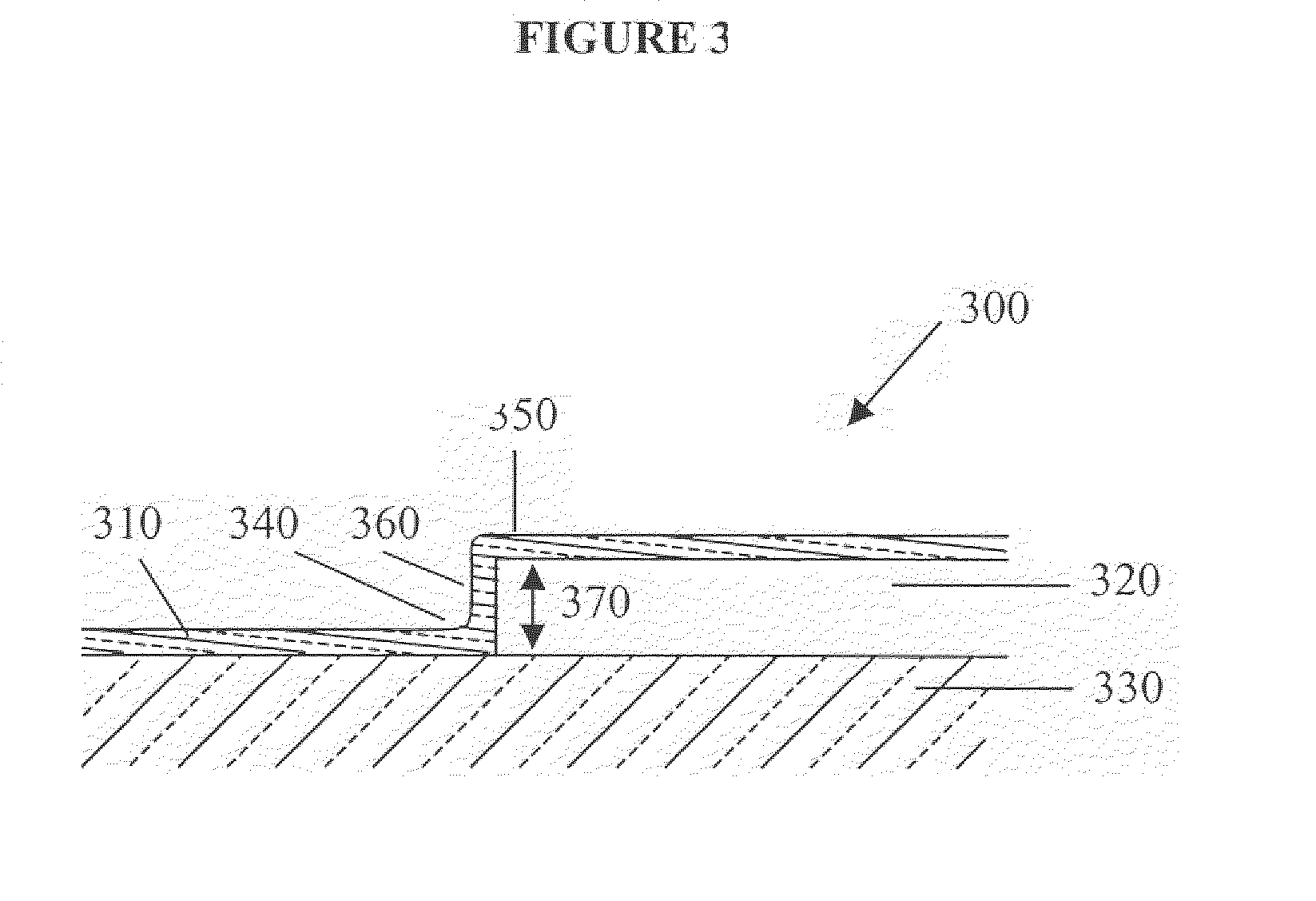

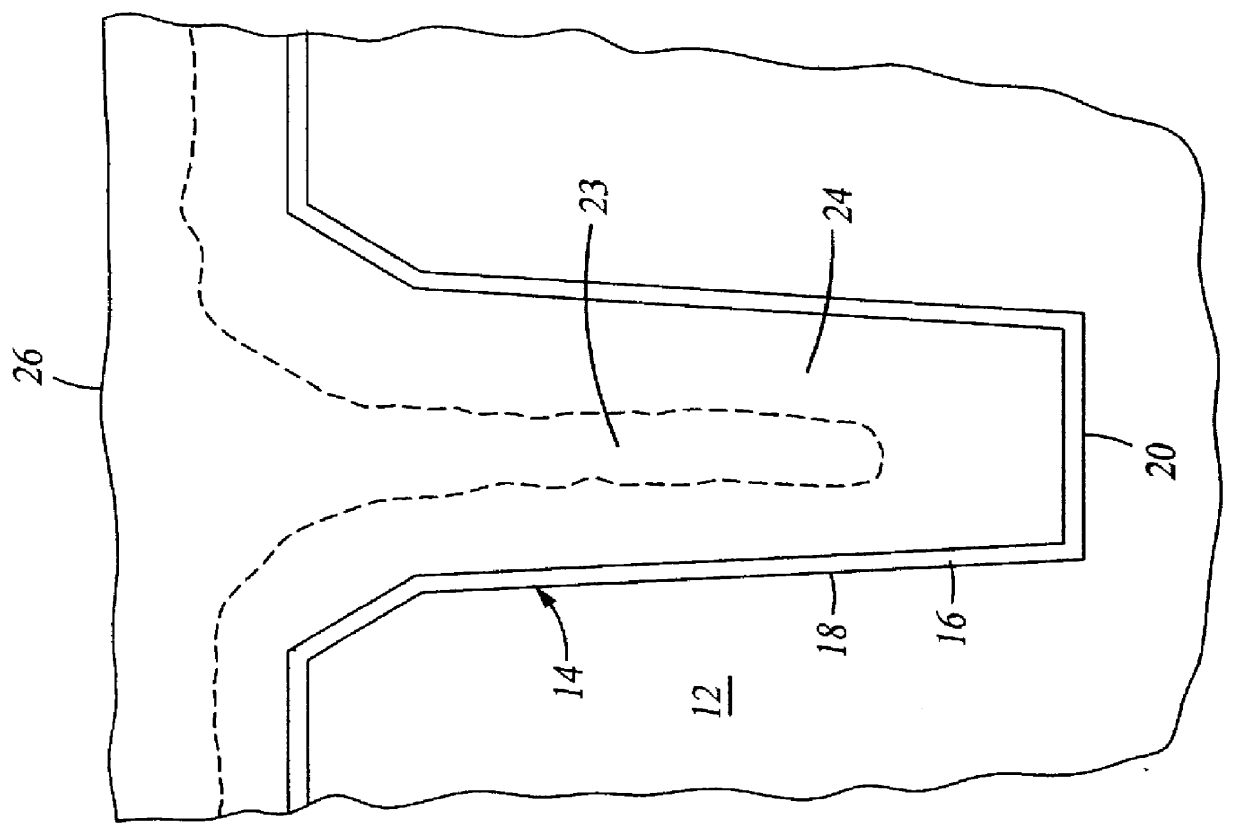

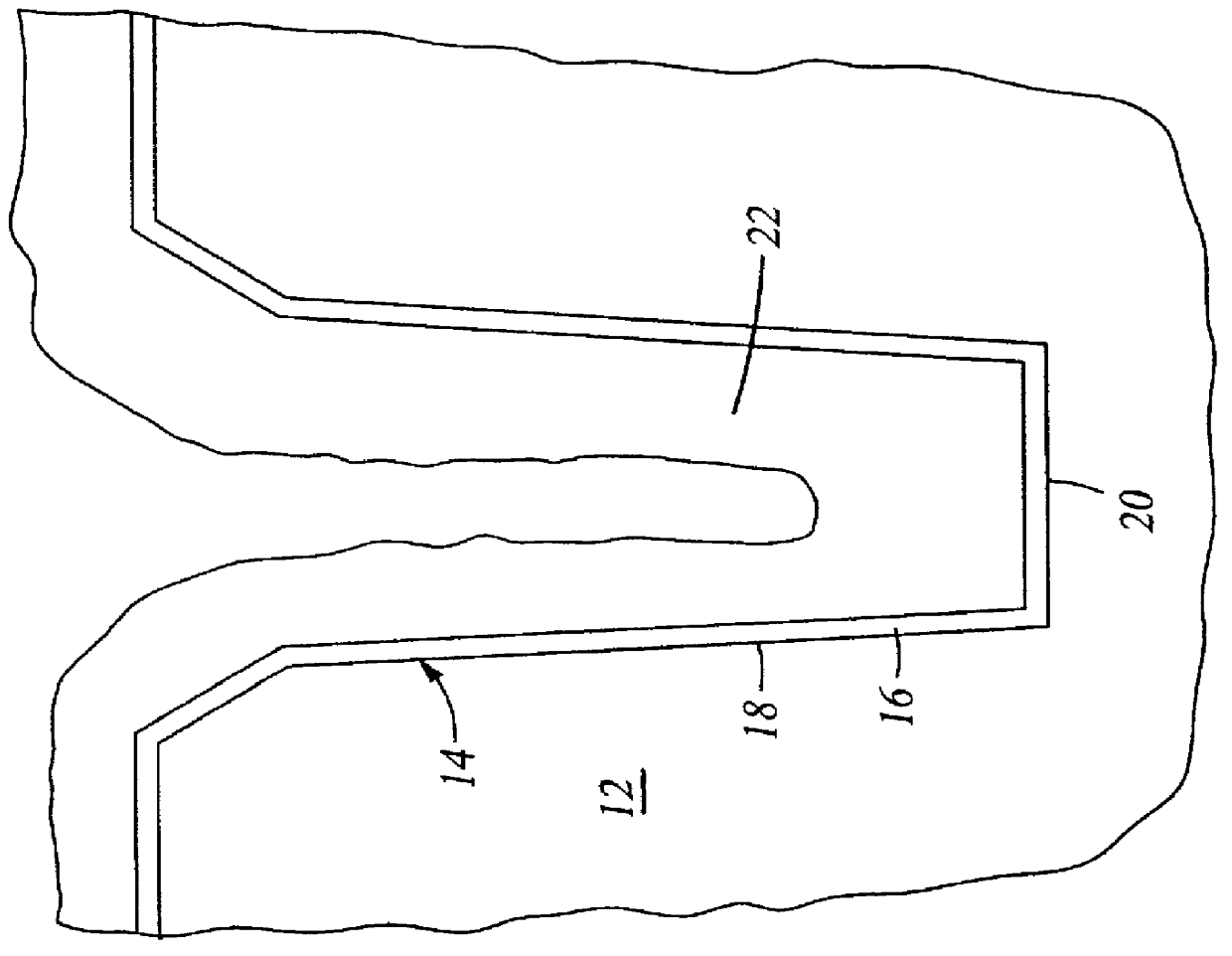

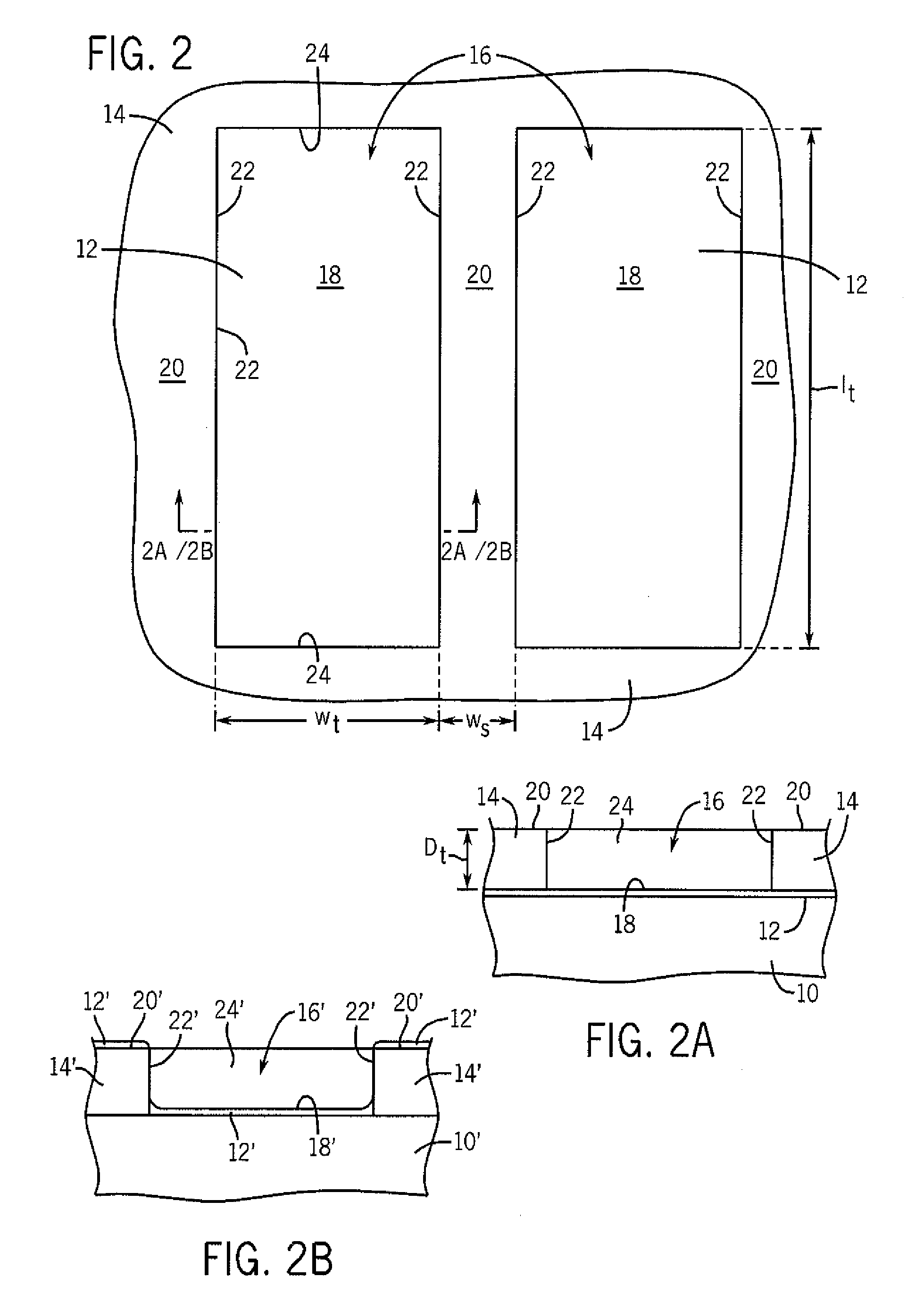

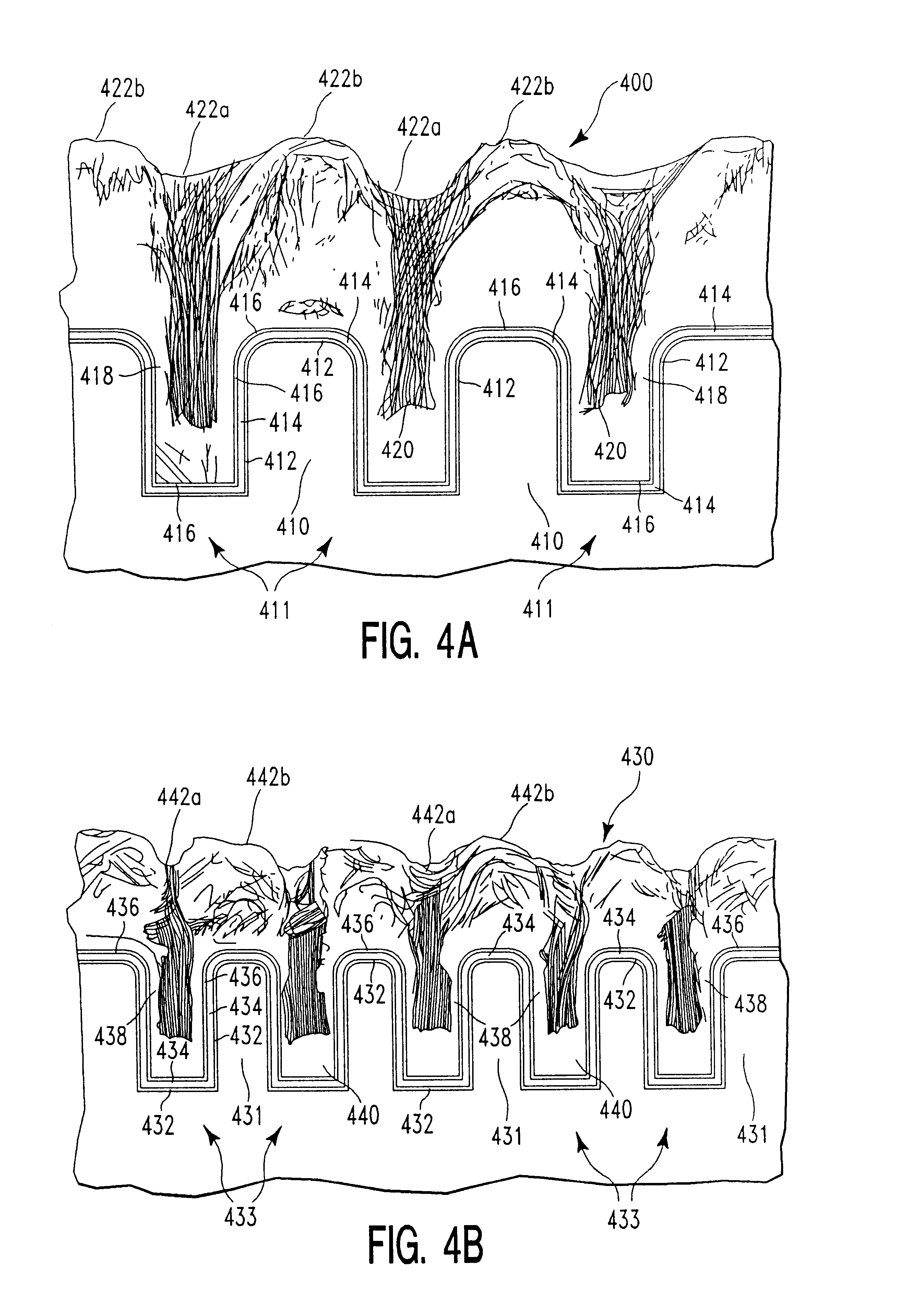

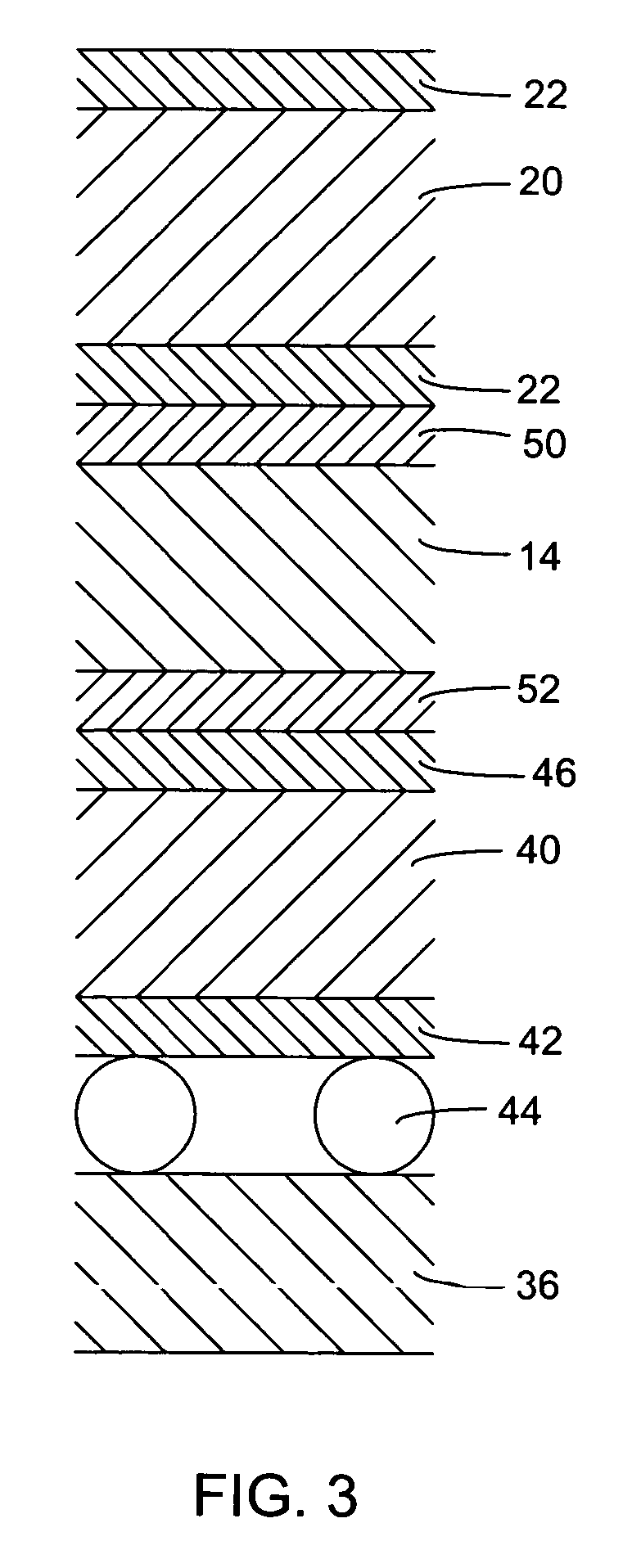

[wafer structure and bumping process thereof]

InactiveUS20050006759A1Improve adhesionExtend equipment lifeSemiconductor/solid-state device detailsSolid-state devicesEngineeringActive surface

The present invention provides a wafer structure having a plurality of bonding pad, an adhesion layer, a barrier layer, a wetting layer, a plurality of bump, a first passivation layer and a second passivation layer. The bonding pads are disposed on the active surface of the wafer and exposed by the first passivation layer. The second passivation layer is disposed on the first passivation layer and exposing the bonding pads. An adhesion layer is disposed on the bonding pad and covers a portion of the first passivation layer. The second passivation layer covers the first passivation layer and a portion of the adhesion layer. The barrier layer and the wetting layer are sequentially disposed on the adhesion layer and the bumps are disposed on the wetting layer.

Owner:ADVANCED SEMICON ENG INC

Damage-free sculptured coating deposition

We disclose a method of applying a sculptured layer of material on a semiconductor feature surface using ion deposition sputtering, wherein a surface onto which the sculptured layer is applied is protected to resist erosion and contamination by impacting ions of a depositing layer, said method comprising the steps of: a) applying a first portion of a sculptured layer with sufficiently low substrate bias that a surface onto which said sculptured layer is applied is not eroded away or contaminated in an amount which is harmful to said semiconductor device performance or longevity; and b) applying a subsequent portion of said sculptured layer with sufficiently high substrate bias to sculpture a shape from said the first portion, while depositing additional layer material. The method is particularly applicable to the sculpturing of barrier layers, wetting layers, and conductive layers upon semiconductor feature surfaces and is especially helpful when the conductive layer is copper. In the application of a barrier layer, a first portion of barrier layer material is deposited on the substrate surface using standard sputtering techniques or using an ion deposition plasma, but in combination with sufficiently low substrate bias voltage (including at no applied substrate voltage) that the surfaces impacted by ions are not sputtered in an amount which is harmful to device performance or longevity. Subsequently, a second portion of barrier material is applied using ion deposition sputtering at increased substrate bias voltage which causes resputtering (sculpturing) of the first portion of barrier layer material, while enabling a more anisotropic deposition of newly depositing material. A conductive material, and particularly a copper seed layer applied to the feature may be accomplished using the same sculpturing technique as that described above with reference to the barrier layer.

Owner:APPLIED MATERIALS INC

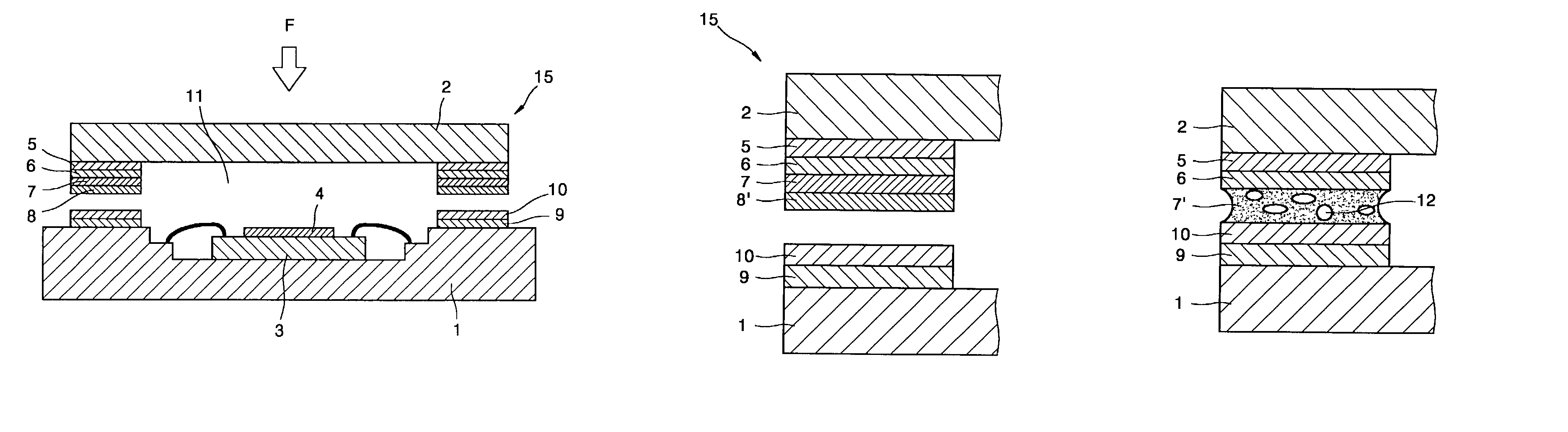

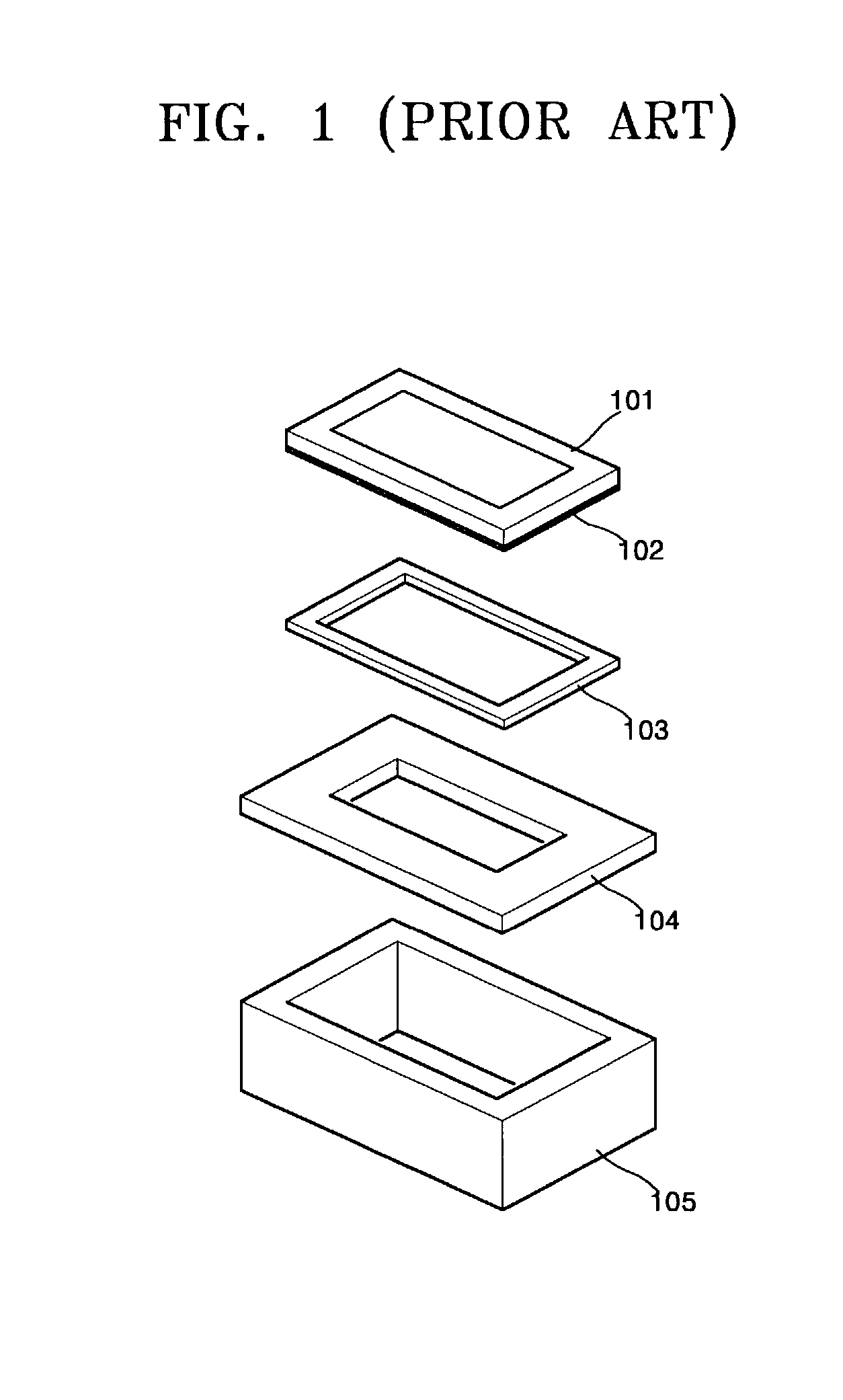

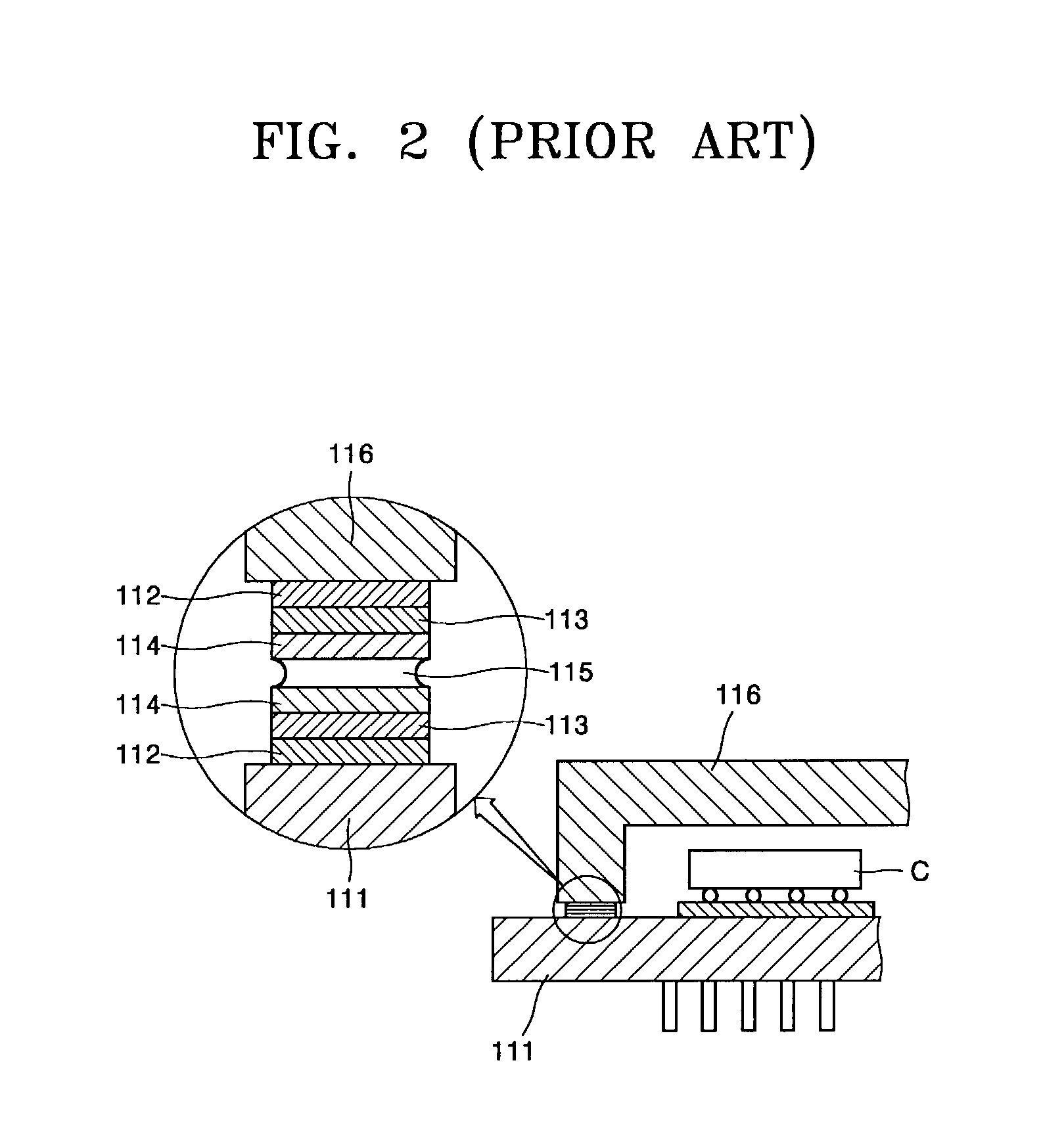

Low temperature hermetic sealing method having passivation layer

ActiveUS7065867B2Improve equipment reliabilityPrevent water penetrationWave amplification devicesDecorative surface effectsHermetic sealEngineering

A hermetic sealing method, which is capable of preventing oxidation of a micro-electromechanical system (MEMS) and sealing the MEMS at a low temperature. A low temperature hermetic sealing method having a passivation layer includes depositing a junction layer, a wetting layer, and a solder layer on a prepared lid frame, depositing a first protection layer for preventing oxidation on the solder layer and forming a lid, preparing a package base on which a device is disposed, and in which a metal layer and a second protection layer are formed around the device, and assembling the lid and the package base, heating, and sealing them. The protection layer is laminated on the solder layer that is formed by the lid, thereby preventing oxidation without using a flux. The low temperature hermetic sealing method having a passivation layer is suitable for sealing a device, such as the MEMS, which is sensitive to heat, water and other by-products.

Owner:SAMSUNG ELECTRONICS CO LTD

Crosslinkable graft polymer non-preferentially wetted by polystyrene and polyethylene oxide

Methods for fabricating a random graft PS-r-PEO copolymer and its use as a neutral wetting layer in the fabrication of sublithographic, nanoscale arrays of elements including openings and linear microchannels utilizing self-assembling block copolymers, and films and devices formed from these methods are provided. In some embodiments, the films can be used as a template or mask to etch openings in an underlying material layer.

Owner:MICRON TECH INC

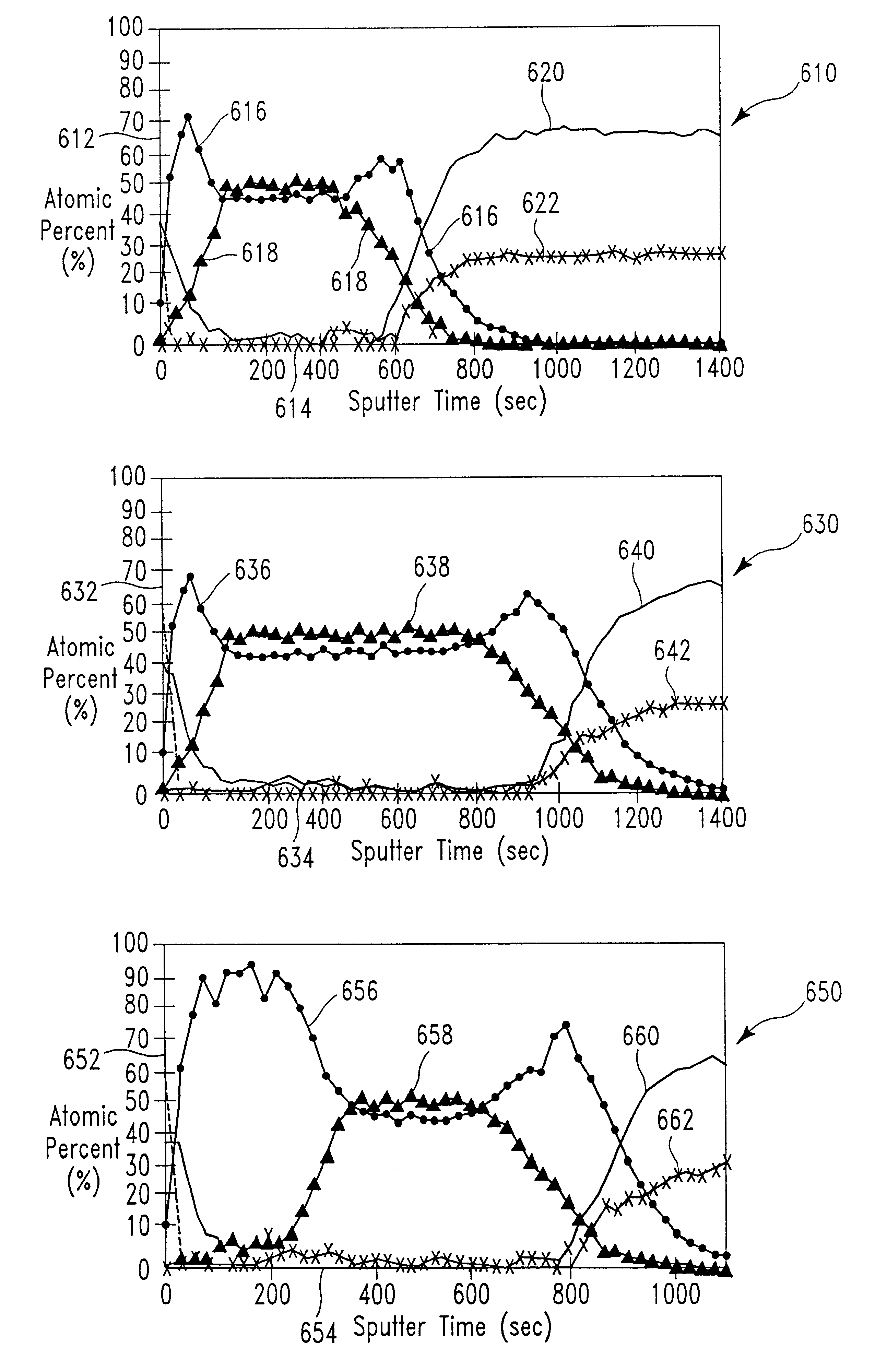

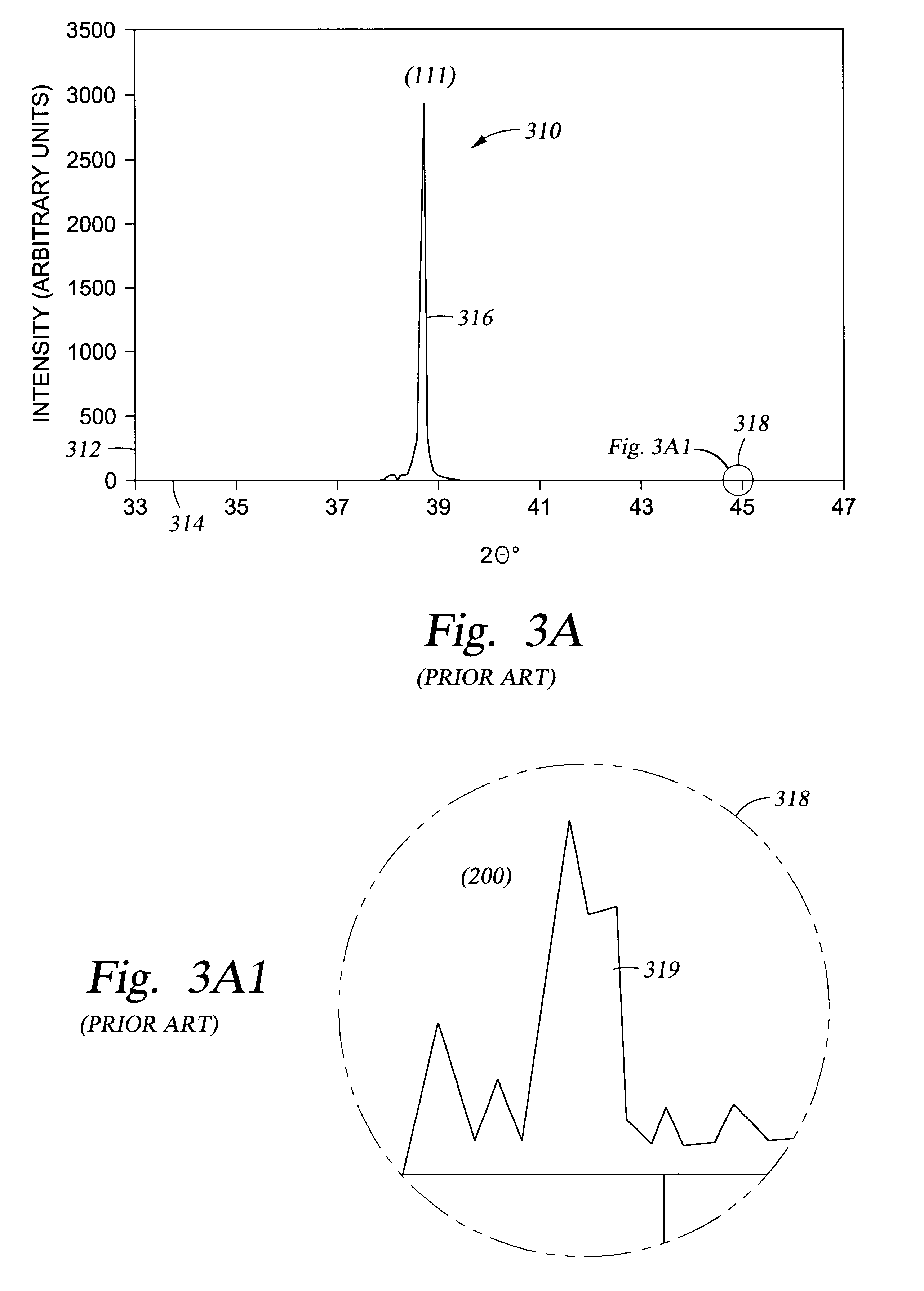

Ti/Tinx underlayer which enables a highly <111> oriented aluminum interconnect

InactiveUS6420260B1Semiconductor/solid-state device detailsSolid-state devicesCrystal orientationTitanium

The present disclosure pertains to particular Ti / TiN / TiNx barrier / wetting layer structures which enable the warm aluminum filling of high aspect vias while providing an aluminum fill exhibiting a high degree of aluminum <111> crystal orientation. It has been discovered that an improved Ti / TiN / TiNx barrier layer deposited using IMP techniques can be obtained by increasing the thickness of the first layer of Ti to range from greater than about 100 Å to about 500 Å (the feature geometry controls the upper thickness limit); by decreasing the thickness of the TiN second layer to range from greater than about 100 Å to less than about 800 Å (preferably less than about 600 Å); and, by controlling the application of the TiNx third layer to provide a Ti content ranging from about 50 atomic percent titanium (stoichiometric) to about 100 atomic percent titanium. Preferably the TiNx third layer is formed at the end of the deposition of the TiN second layer and exhibits a Ti content gradient which begins at a stoichiometric, 50 atomic percent, Ti content and ends at a Ti content of about 100 atomic percent. The thickness of the TiNx third layer preferably ranges from about 15 Å to about 500 Å. The improved Ti / TiN / TiNx barrier layer enables the deposit of a warm aluminum interconnect or a warm aluminum via fill where the aluminum exhibits a high <111> crystallographic content. Further, the aluminum layer obtained exhibits a reflectivity of 150 percent or greater at 436 nm. A Ti / TiN / TiNx barrier layer having this structure, used to line a contact via, enables complete filling of via with sputtered warm aluminum, where the feature size of the via or aperture, is about 0.25 micron or less and the aspect ratio ranges from about 5:1 to as high as about 6:1.

Owner:APPLIED MATERIALS INC

Semiconductor device and method of fabricating the same

InactiveUS6107182ASuppress generationReduce in quantitySemiconductor/solid-state device detailsSemiconductor/solid-state device manufacturingDielectricSemiconductor

A semiconductor device having a contact structure that can exhibit superlative step coverage without causing voids or wiring discontinuities, using aluminum or aluminum alloys as a conductive substance for via-holes. A method of fabricating the semiconductor device comprises, for at least one layer of wiring regions above the first wiring region on a semiconductor substrate, the following steps (a) to (f): (a) a step of forming a via-hole in a second interlayer dielectric formed above the first wiring region on a semiconductor substrate; (b) a degassing step for removing gaseous components included within the interlayer dielectric by a heat treatment under reduced pressure and at the substrate temperature of 300 DEG C. to 550 DEG C.; (c) a step of forming a wetting layer on the surface of the interlayer dielectric and the via-hole; (d) a step of cooling the substrate to a temperature of no more than 100 DEG C.; (e) a step of forming a first aluminum layer comprising one of aluminum and an alloy in which aluminum is the main component on the wetting layer at a temperature of no more than 200 DEG C.; and (f) a step of forming a second aluminum layer comprising one of aluminum and an alloy in which aluminum is the main component on the first aluminum layer at a temperature of at least 300 DEG C.

Owner:SEIKO EPSON CORP

Method of fabricating a wafer structure having a pad and a first protection layer and a second protection layer

ActiveUS7682960B2Quality improvementIncrease ratingsSolid-state devicesSemiconductor/solid-state device manufacturingResistProtection layer

A wafer structure and a method for fabricating the same are provided. First, a wafer having a pad and a first protection layer with a first opening is provided. Next, a second protection layer with a second opening is formed on the first protection layer. Part of the pad and the first protection layer are exposed from the openings. The edges of the openings construct a step structure. Following that, an adhesion layer is formed on the pad, the step structure and the second protection layer. Afterwards, a photo-resist layer with a third opening is formed on the adhesion layer. Then, a barrier layer is electroplated onto part of the adhesion layer. Further, a wetting layer is formed on the barrier layer, and then the photo-resist layer and part of the adhesion layer exposed outside the barrier layer are removed. Finally, a solder layer is printed onto the wetting layer.

Owner:ADVANCED SEMICON ENG INC

Method of preventing diffusion of copper through a tantalum-comprising barrier layer

InactiveUS20040171250A1Vacuum evaporation coatingSputtering coatingDevice materialConductive materials

We disclose a method of applying a sculptured layer of material on a semiconductor feature surface using ion deposition sputtering, wherein a surface onto which the sculptured layer is applied is protected to resist erosion and contamination by impacting ions of a depositing layer, said method comprising the steps of: a) applying a first portion of a sculptured layer with sufficiently low substrate bias that a surface onto which said sculptured layer is applied is not eroded away or contaminated in an amount which is harmful to said semiconductor device performance or longevity; and b) applying a subsequent portion of said sculptured layer with sufficiently high substrate bias to sculpture a shape from said the first portion, while depositing additional layer material. The method is particularly applicable to the sculpturing of barrier layers, wetting layers, and conductive layers upon semiconductor feature surfaces and is especially helpful when the conductive layer is copper. In the application of a barrier layer, a first portion of barrier layer material is deposited on the substrate surface using standard sputtering techniques or using an ion deposition plasma, but in combination with sufficiently low substrate bias voltage (including at no applied substrate voltage) that the surfaces impacted by ions are not sputtered in an amount which is harmful to device performance or longevity. Subsequently, a second portion of barrier material is applied using ion deposition sputtering at increased substrate bias voltage which causes resputtering (sculpturing) of the first portion of barrier layer material, while enabling a more anisotropic deposition of newly depositing material. A conductive material, and particularly a copper seed layer applied to the feature may be accomplished using the same sculpturing technique as that described above with reference to the barrier layer.

Owner:APPLIED MATERIALS INC

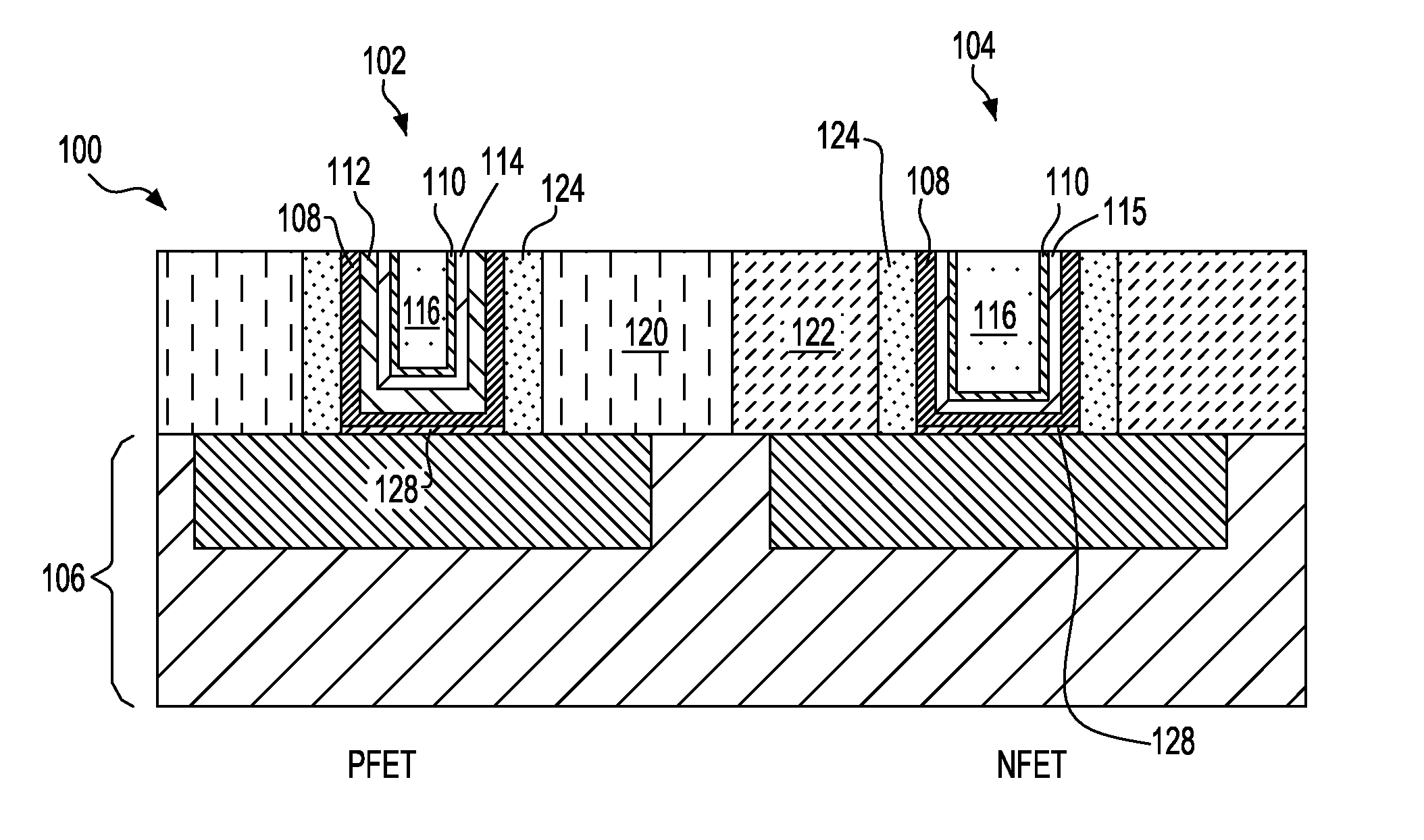

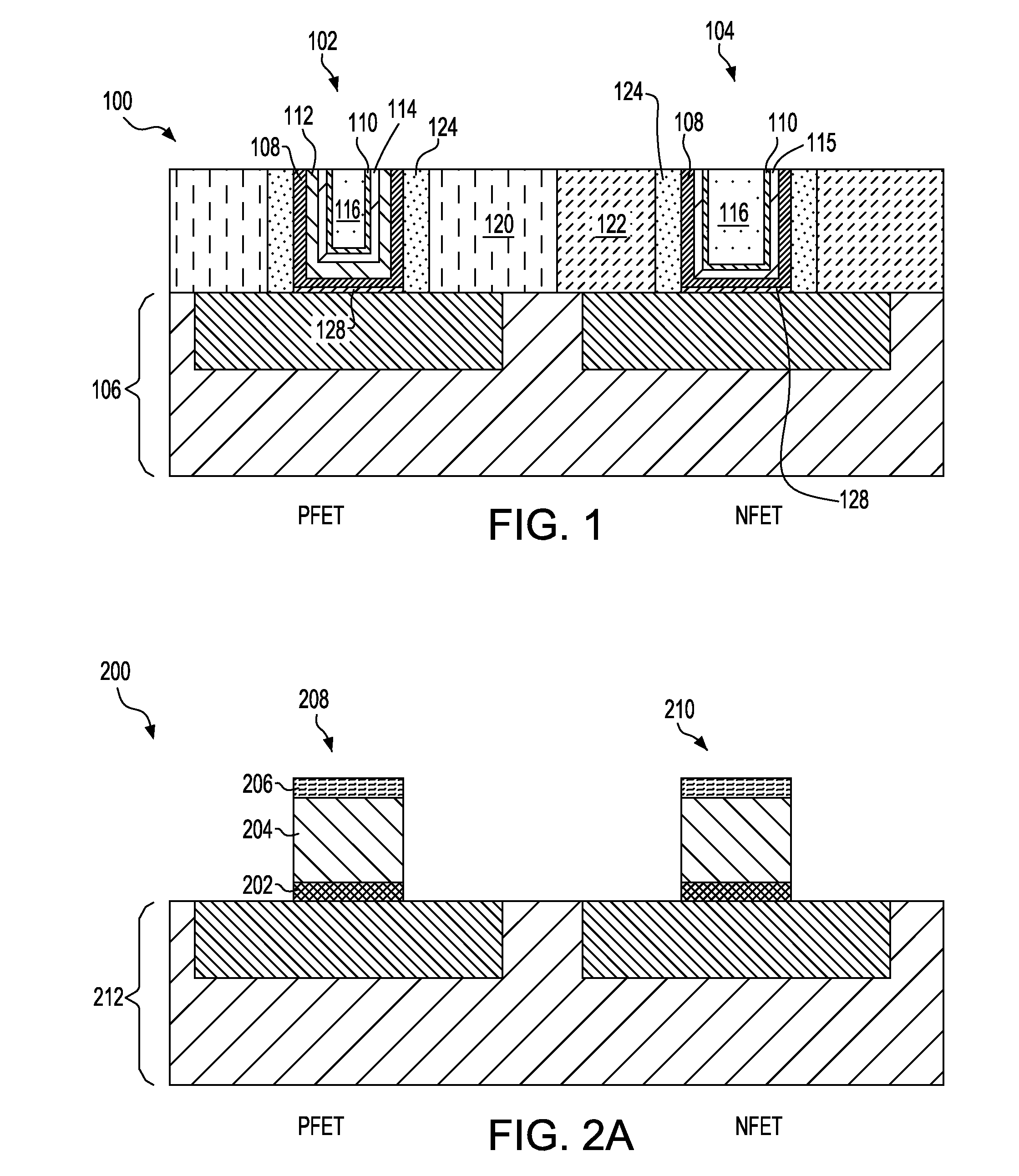

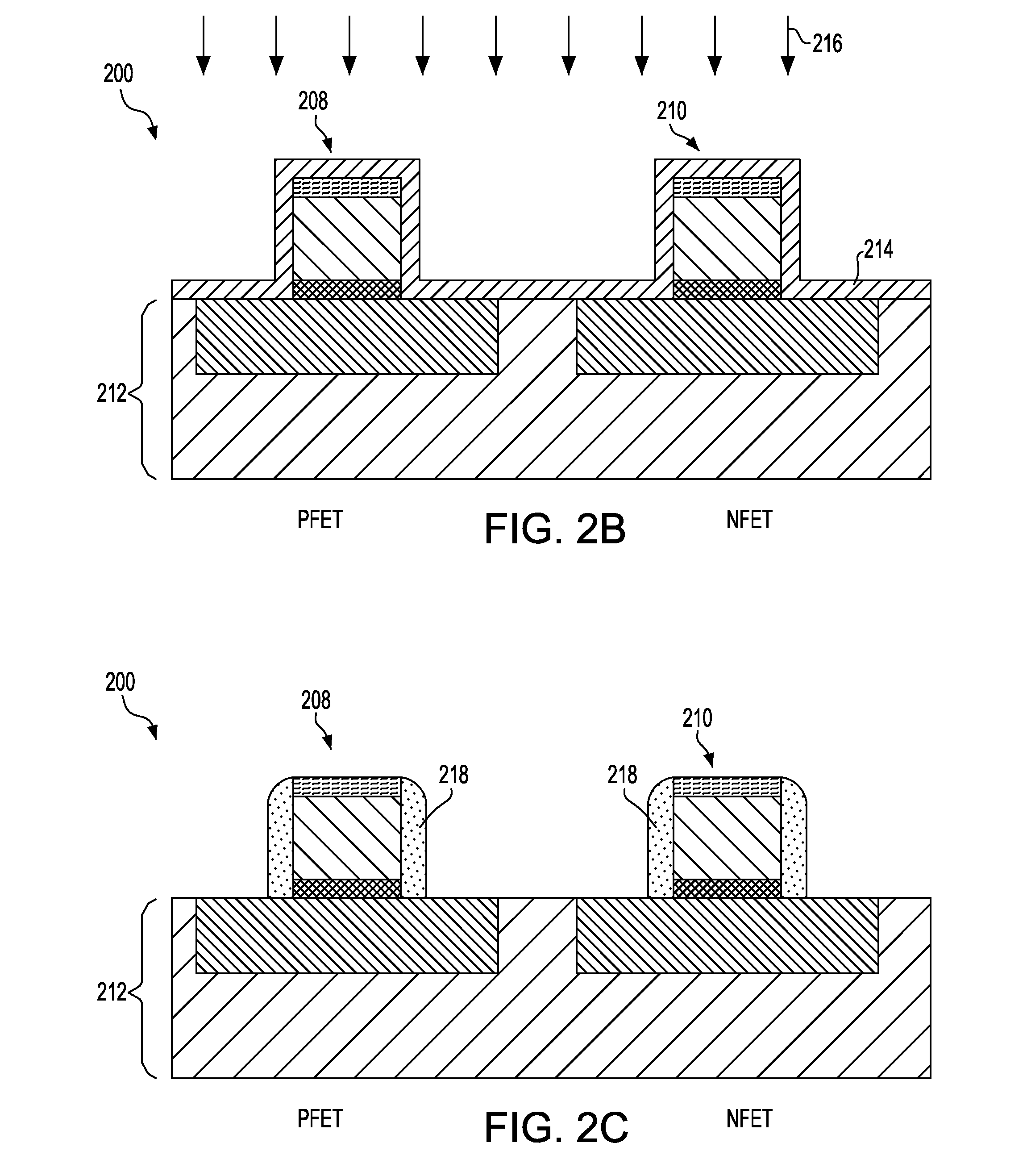

Integrated circuit with replacement gate stacks and method of forming same

A first aspect of the invention provides for a method including: forming an interfacial layer in a first opening in a pFET region and a second opening in an nFET region, each opening being in a dielectric layer in the pFET region and the nFET region; forming a high-k layer over the interfacial layer in each of the first and second openings; forming a wetting layer over the high-k layer in each of the first and second openings; forming a first metal layer in each of the first and second openings, the first metal layer including tungsten; and forming a first gate electrode layer over the first metal layer to substantially fill each of the first and second openings, thereby forming a first replacement gate stack over the pFET region and a second replacement gate stack over the nFET region.

Owner:IBM CORP

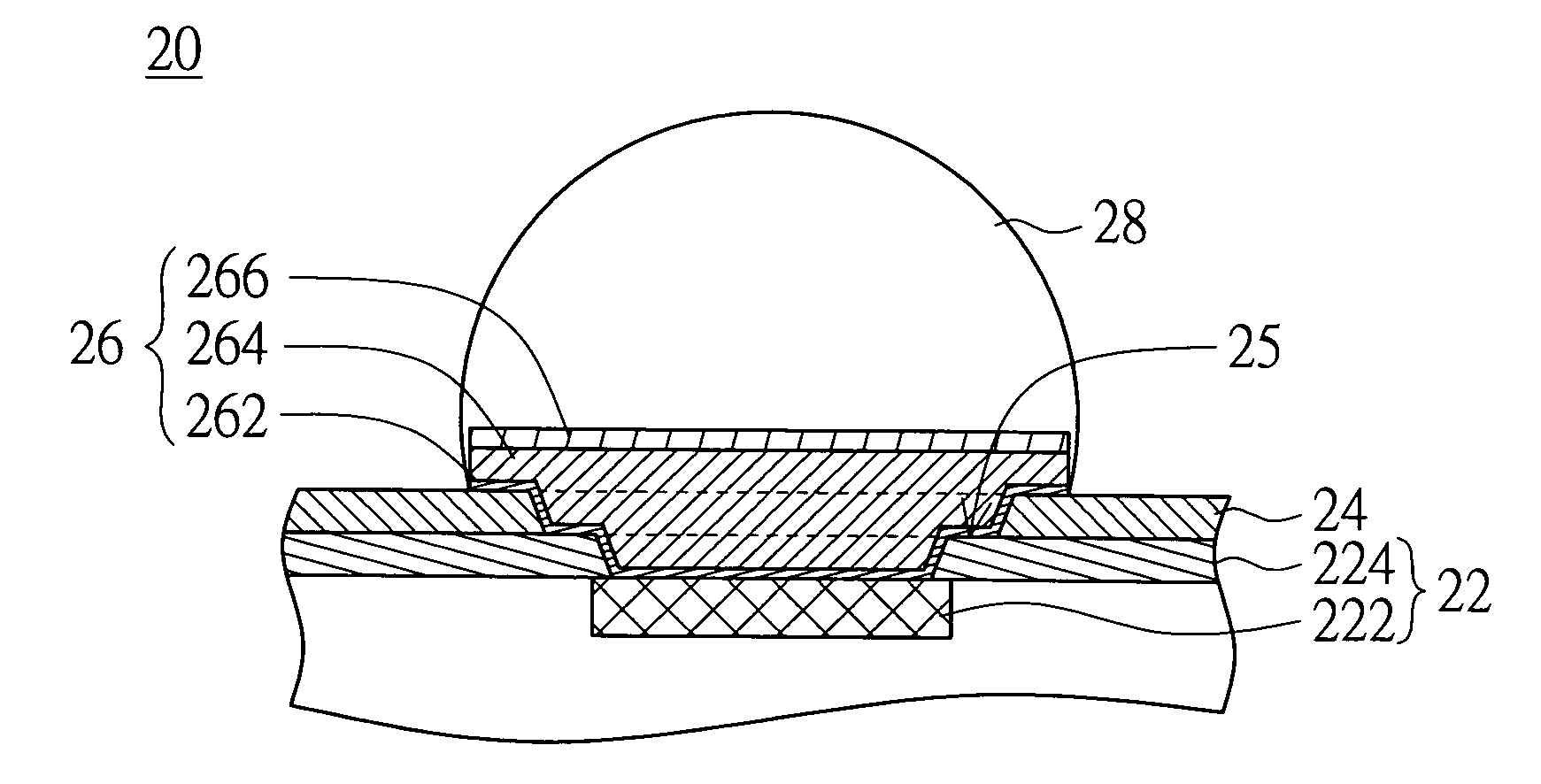

Under bump metallization structure of a semiconductor wafer

ActiveUS6930389B2Slow down formationHigh bonding strengthSemiconductor/solid-state device detailsSolid-state devicesEngineeringUnder bump metallurgy

An under bump metallurgy structure is applicable to be disposed above the wafer and on the bonding pads of the wafer. The wafer comprises a passivation layer and an under bump metallurgy structure. The passivation layer exposes the wafer pads, and the under bump metallurgy structure including an adhesive layer, a first barrier layer, a wetting layer and a second barrier layer are sequentially formed on the bonding pads. Specifically, the material of the second barrier mainly includes lead.

Owner:ADVANCED SEMICON ENG INC

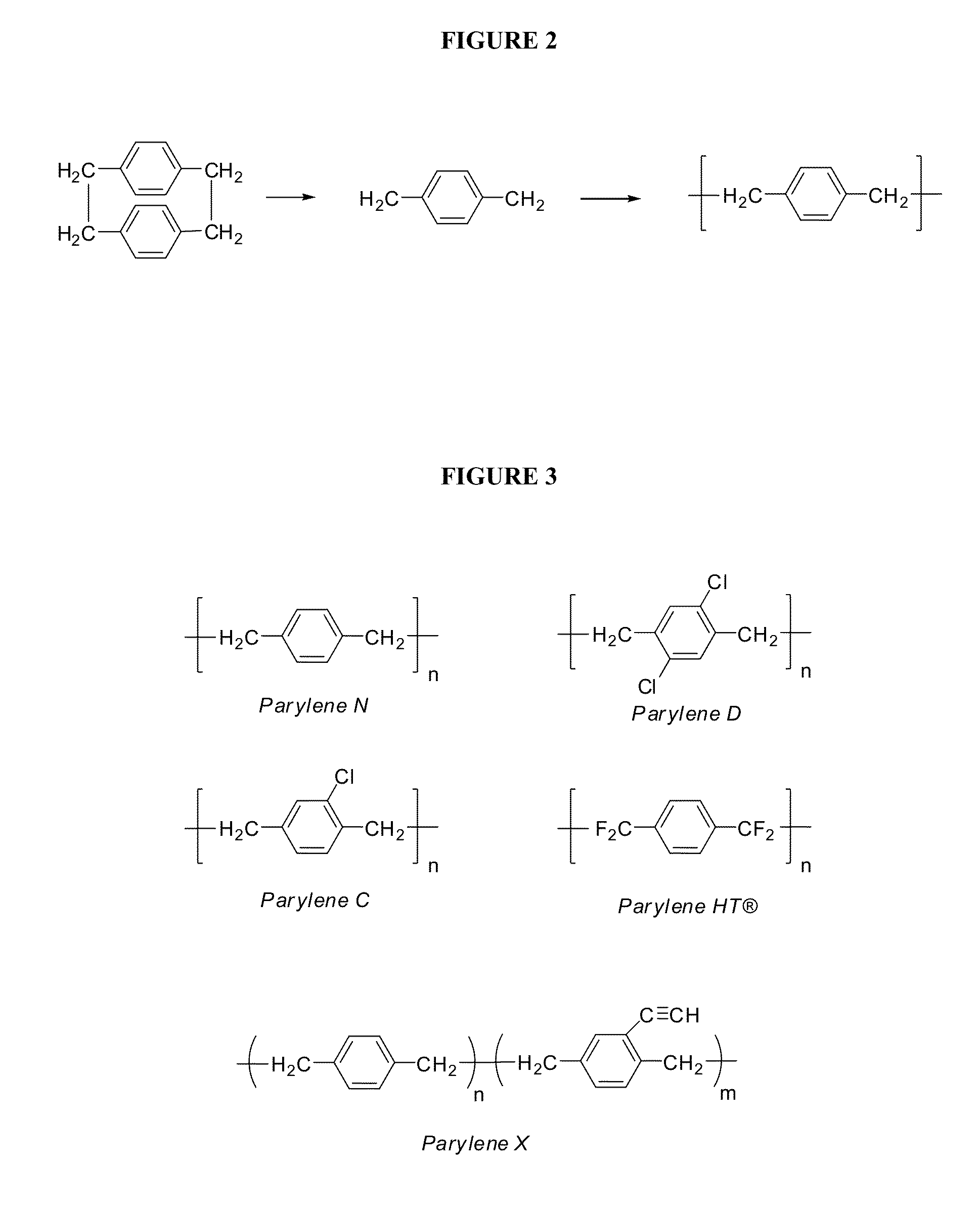

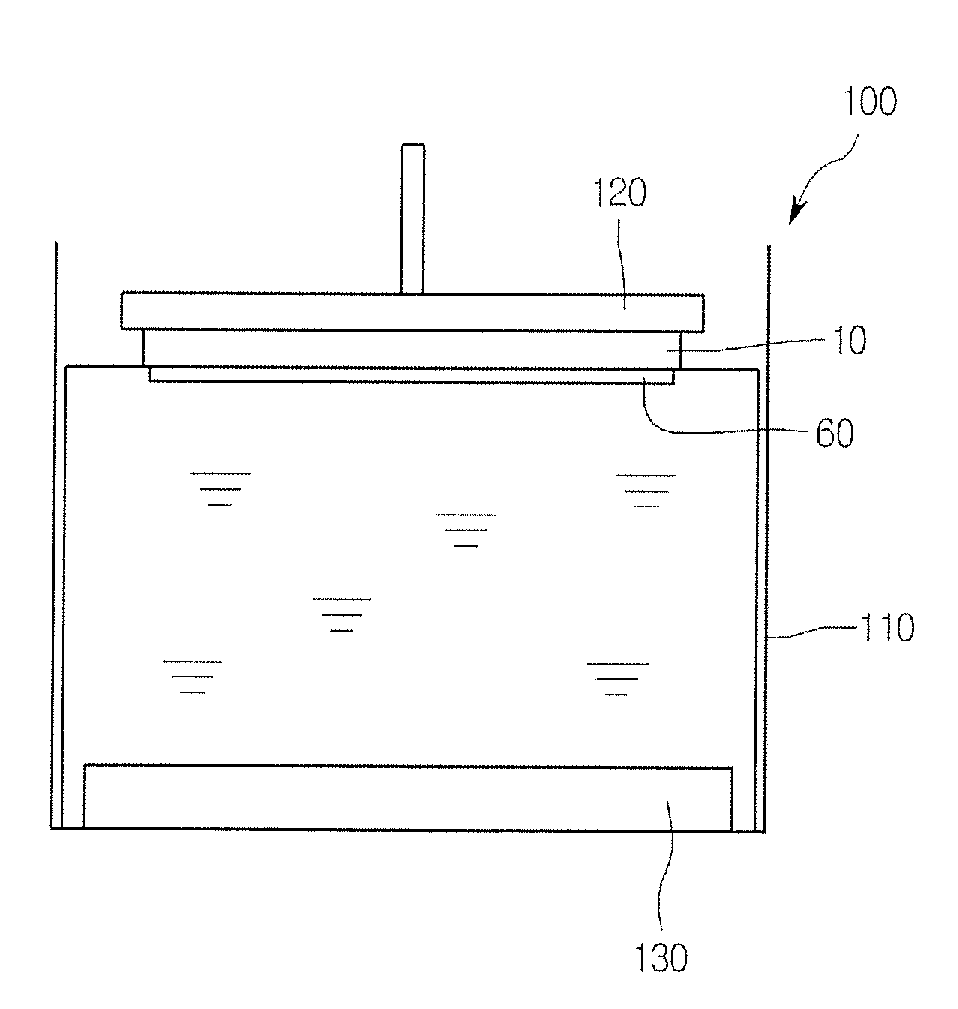

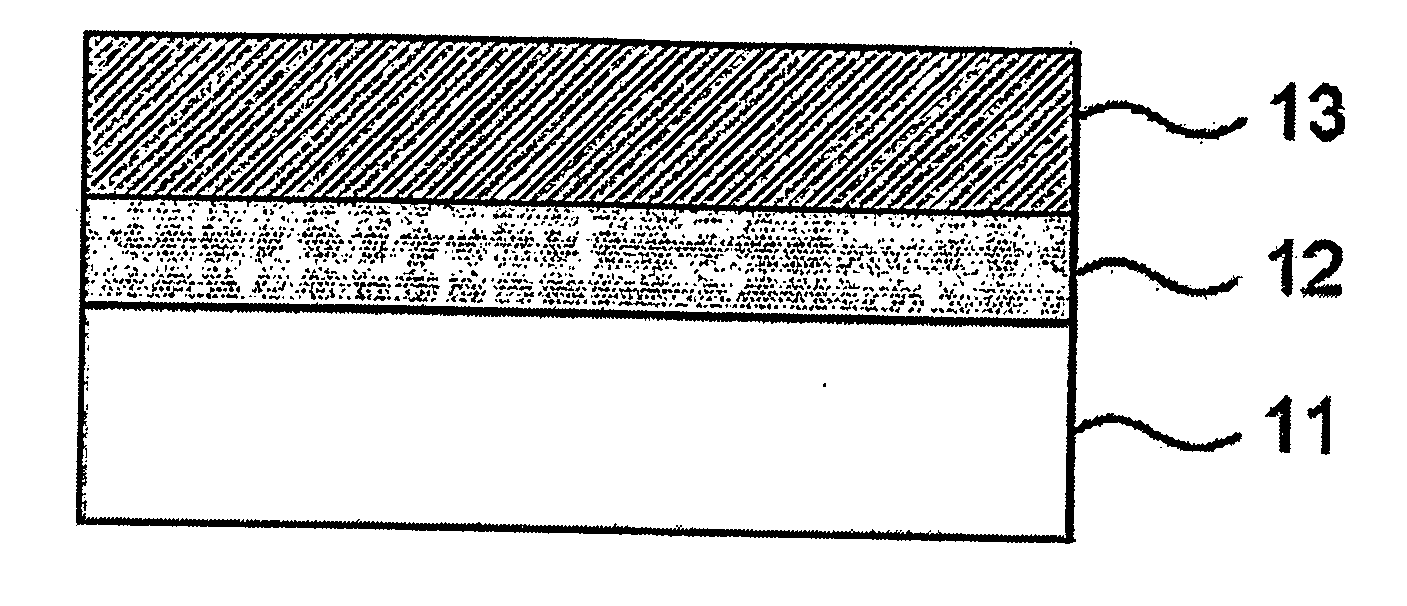

Using chemical vapor deposited films to control domain orientation in block copolymer thin films

InactiveUS20130209757A1High etch contrastIncrease chiDecorative surface effectsLayered productsPolymer scienceNanostructure

The present invention uses vacuum deposited thin films of material to create an interface that non-preferentially interacts with different domains of an underlying block copolymer film. The non-preferential interface prevents formation of a wetting layer and influences the orientation of domains in the block copolymer. The purpose of the deposited polymer is to produce nanostructured features in a block copolymer film that can serve as lithographic patterns.

Owner:BOARD OF RGT THE UNIV OF TEXAS SYST

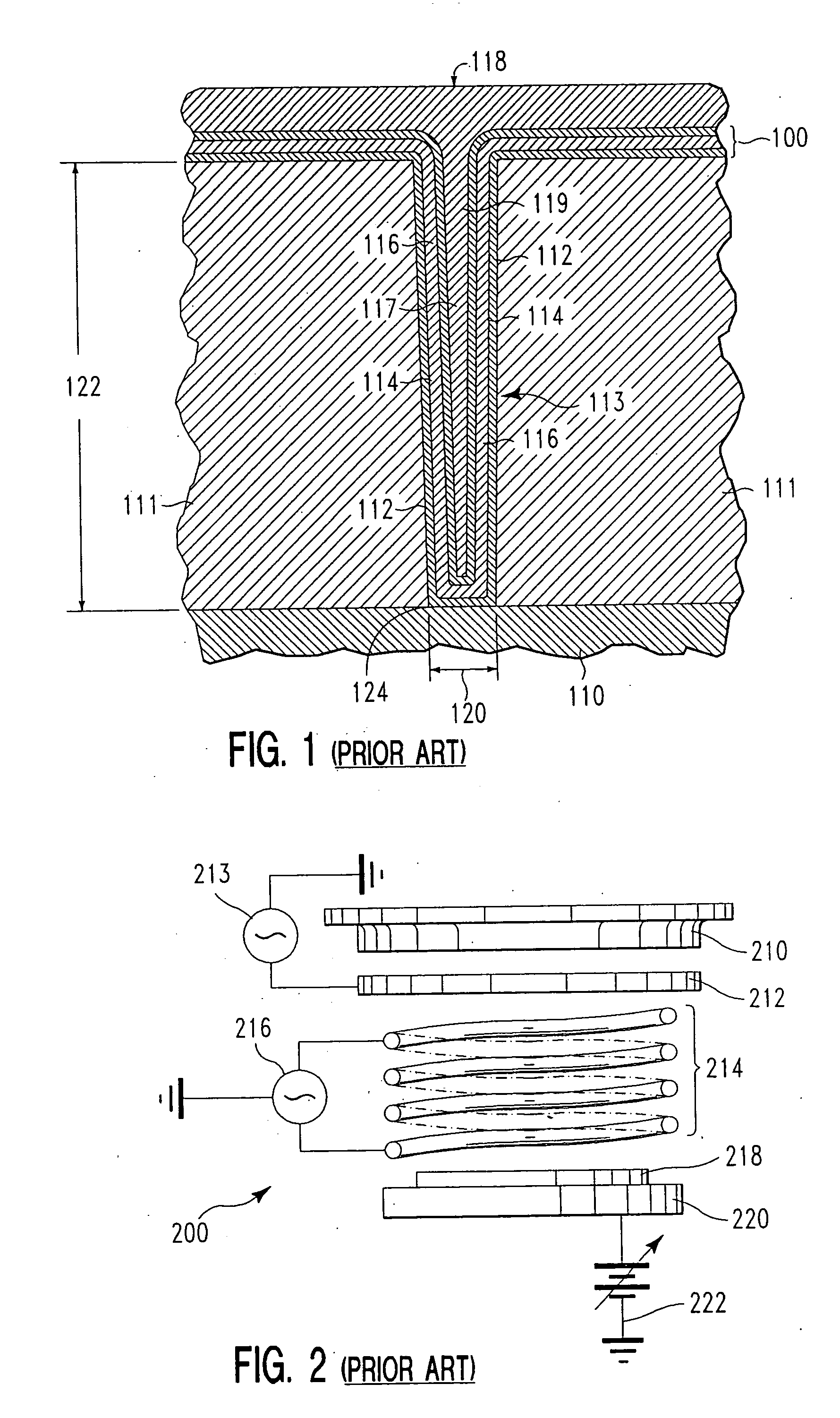

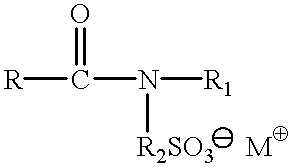

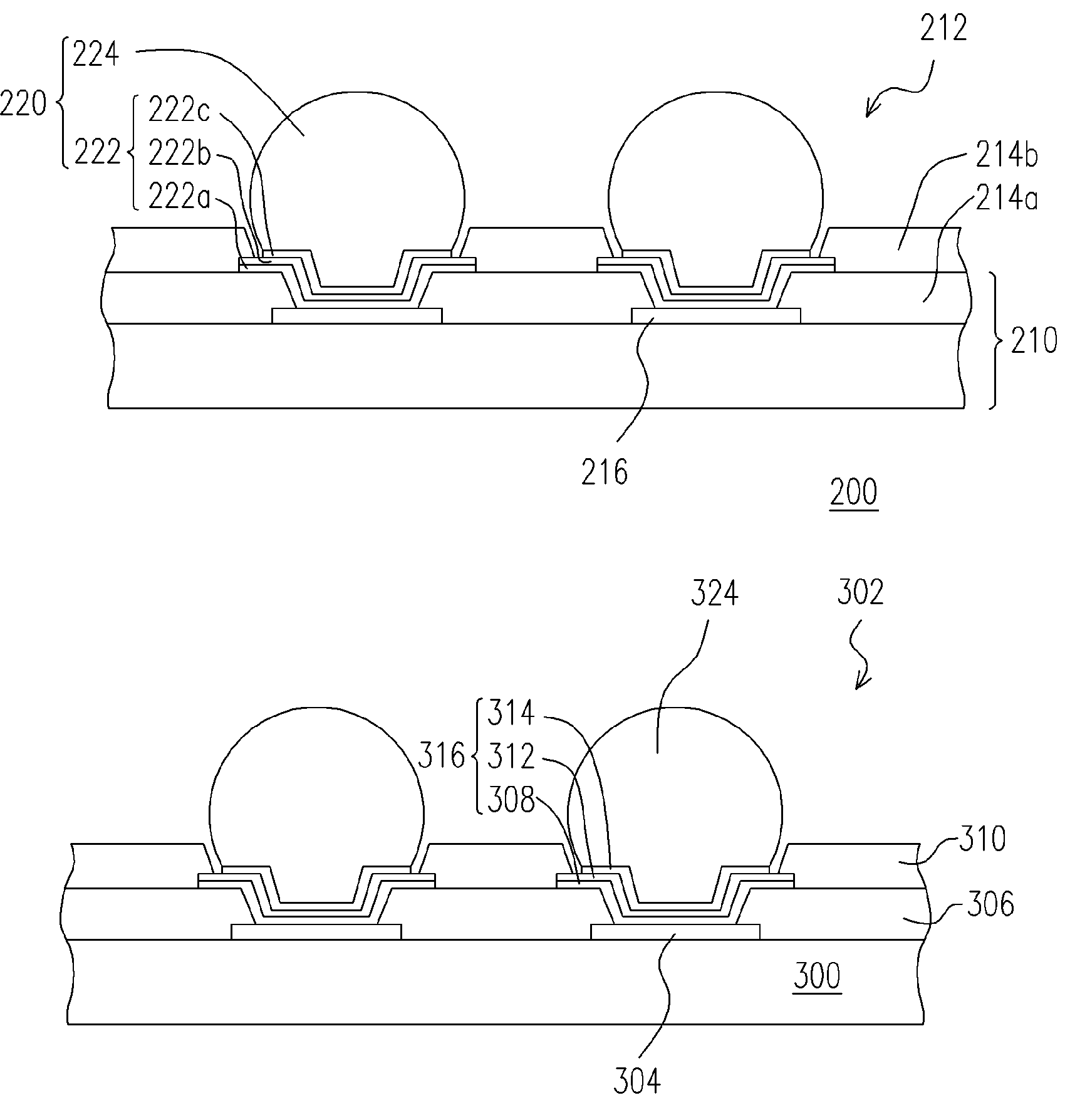

Via Plating Method of System in Package and System Thereof

InactiveUS20080149487A1Efficiently formedImprove featuresCellsSemiconductor/solid-state device manufacturingEngineeringSystem in package

A via plating system and method are provided. A preprocessing procedure is performed such that a pre-wetting solution is absorbed into a via hole, forming a wetting layer thereon. A plating process is then performed to form a plating layer inside the via hole. The preprocessing procedure to form the wetting layer improves the absorbing characteristics inside the via hole, allowing the plating layer to be more effectively formed.

Owner:DONGBU HITEK CO LTD

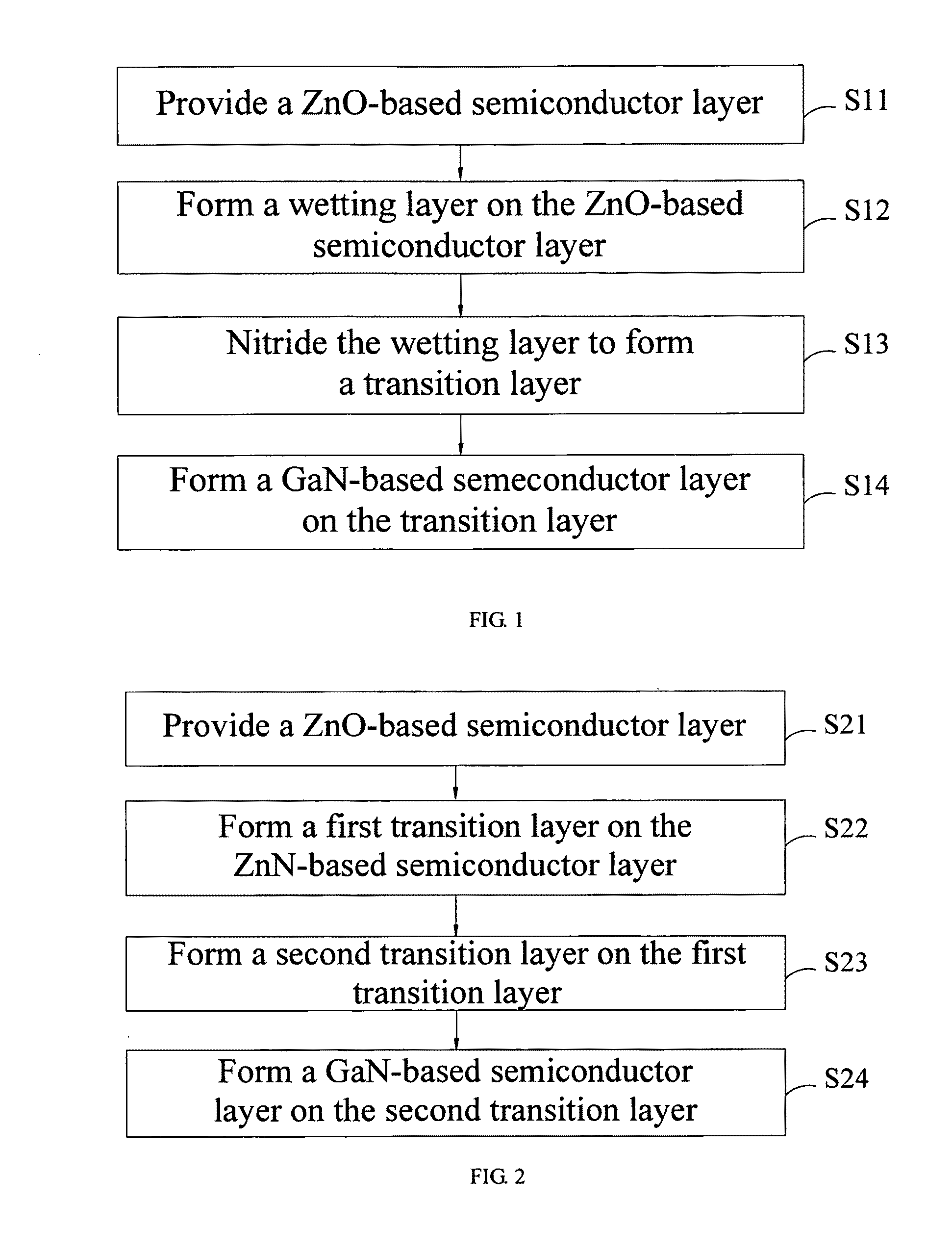

Method for fabricating gaN-based nitride layer

ActiveUS20060154454A1Good physical propertiesImprove efficiencyPolycrystalline material growthSemiconductor/solid-state device manufacturingNitrogenGallium nitride

The present invention relates to a method for fabricating a gallium nitride(GaN) based nitride layer including a step of forming a wetting layer having of forming a wetting layer having a composition of In(x1)Ga(y1)N (0<x1≦1, 0≦y1<1, x1+y1=1) on the silicon carbide buffer layer, and a step of forming a nitride layer containing gallium and nitrogen on the wetting layer, thereby can implement an opto-electronic device of high efficiency and high reliability.

Owner:EPIVALLEY +1

Methods of forming carbon nanotubes architectures and composites with high electrical and thermal conductivities and structures formed thereby

Methods and associated structures of forming microelectronic devices are described. Those methods may include method of forming a layered nanotube structure comprising a wetting layer disposed on a nanotube, a Shottky layer disposed on the wetting layer, a barrier layer disposed on the Shottky layer, and a matrix layer disposed on the barrier layer.

Owner:INTEL CORP

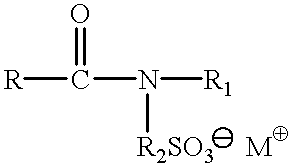

Semiconductor structure having a wetting layer

ActiveUS20130037865A1Semiconductor/solid-state device manufacturingNanotechnologyGate dielectricSemiconductor structure

A semiconductor structure which includes a semiconductor substrate and a metal gate structure formed in a trench or via on the semiconductor substrate. The metal gate structure includes a gate dielectric; a wetting layer selected from the group consisting of cobalt and nickel on the gate dielectric lining the trench or via and having an oxygen content of no more than about 200 ppm (parts per million) oxygen; and an aluminum layer to fill the remainder of the trench or via. There is also disclosed a method of forming a semiconductor structure in which a wetting layer is formed from cobalt amidinate or nickel amidinate deposited by a chemical vapor deposition process.

Owner:GLOBALFOUNDRIES US INC

Semiconductor device

ActiveUS20110140206A1Improve reliabilityImprove performanceSemiconductor/solid-state device manufacturingSemiconductor devicesWork functionSemiconductor

A semiconductor device including a substrate, a gate structure, a spacer and source / drain regions is provided. The gate structure is on the substrate, wherein the gate structure includes, from bottom to top, a high-k layer, a work function metal layer, a wetting layer and a metal layer. The spacer is on a sidewall of the gate structure. The source / drain regions are in the substrate beside the gate structure.

Owner:UNITED MICROELECTRONICS CORP

Bump electrodes having multiple under ball metallurgy (UBM) layers

InactiveUS7271498B2Improve adhesionExtend equipment lifeSemiconductor/solid-state device detailsSolid-state devicesEngineeringActive surface

The present invention provides a wafer structure having a plurality of bonding pad, an adhesion layer, a barrier layer, a wetting layer, a plurality of bump, a first passivation layer and a second passivation layer. The bonding pads are disposed on the active surface of the wafer and exposed by the first passivation layer. The second passivation layer is disposed on the first passivation layer and exposing the bonding pads. An adhesion layer is disposed on the bonding pad and covers a portion of the first passivation layer. The second passivation layer covers the first passivation layer and a portion of the adhesion layer. The barrier layer and the wetting layer are sequentially disposed on the adhesion layer and the bumps are disposed on the wetting layer.

Owner:ADVANCED SEMICON ENG INC

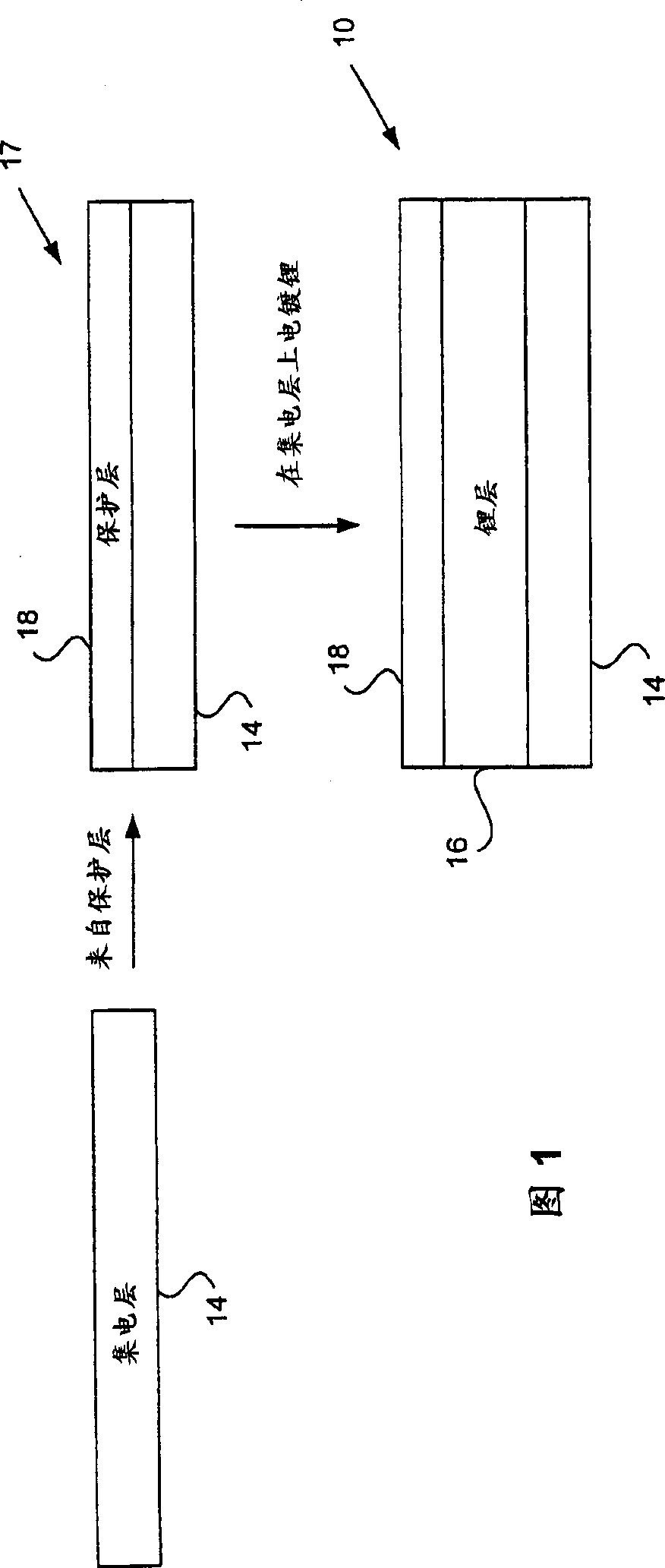

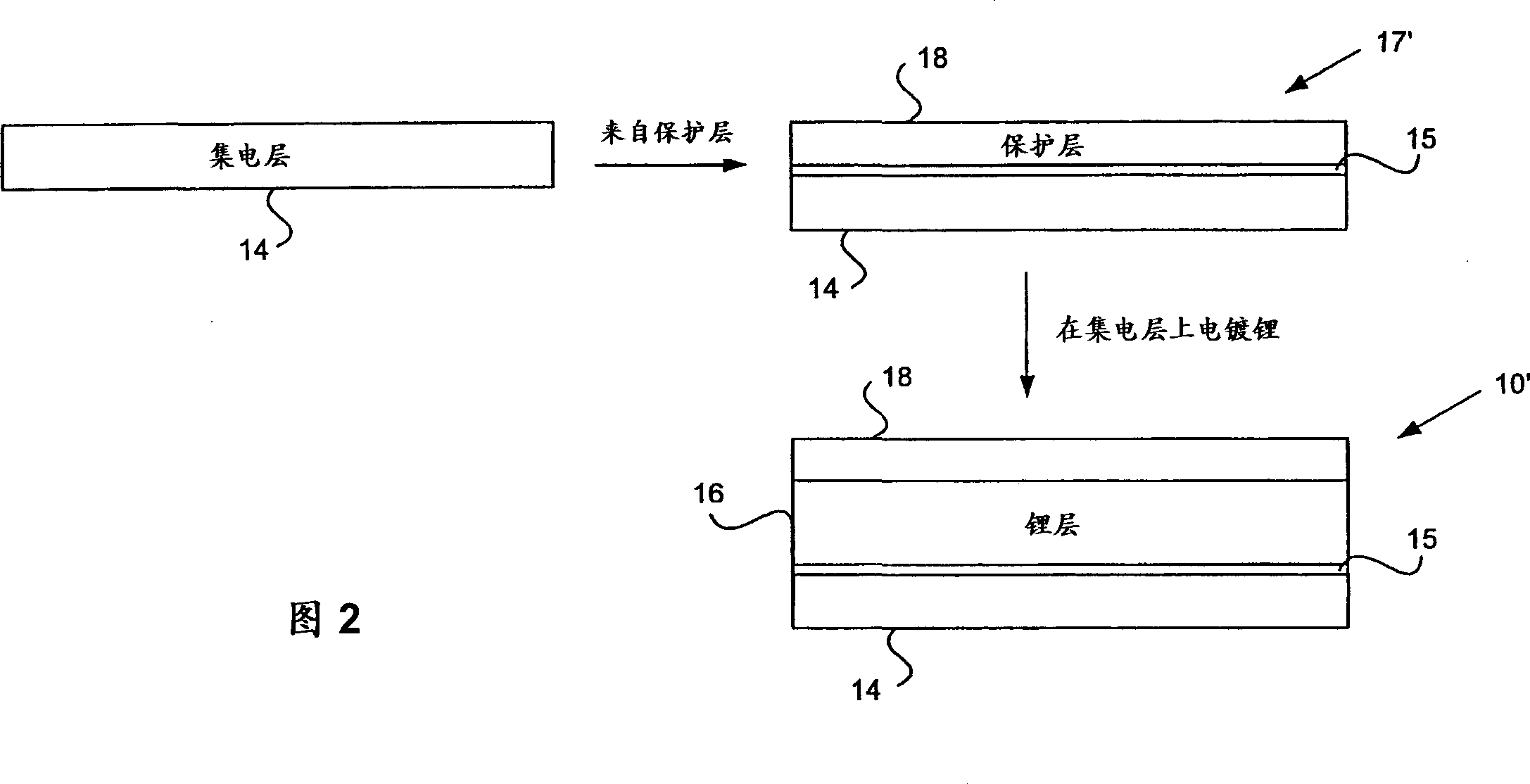

Plating metal negative electrodes under protective coatings

InactiveCN1297588AElectrochemical processing of electrodesElectrode carriers/collectorsLithium metalProtection layer

A method for forming lithium electrodes having protective layers involves plating lithium (16) between a lithium ion conductive protective layer (18) and a current collector (14) of an 'electrode precursor'. The electrode precursor is formed by depositing the protective layer on a very smooth surface of a current collector. The protective layer is a glass such as lithium phosphorus oxynitride and the current collector is a conductive sheet such as a copper sheet. During plating, lithium ions move through the protective layer and a lithium metal layer plates onto the surface of the current collector. The resulting structure is a protected lithium electrode. To facilitate uniform lithium plating, the electrode precursor may include a 'wetting layer' which coats the current collector.

Owner:POLYPLUS BATTERY CO INC

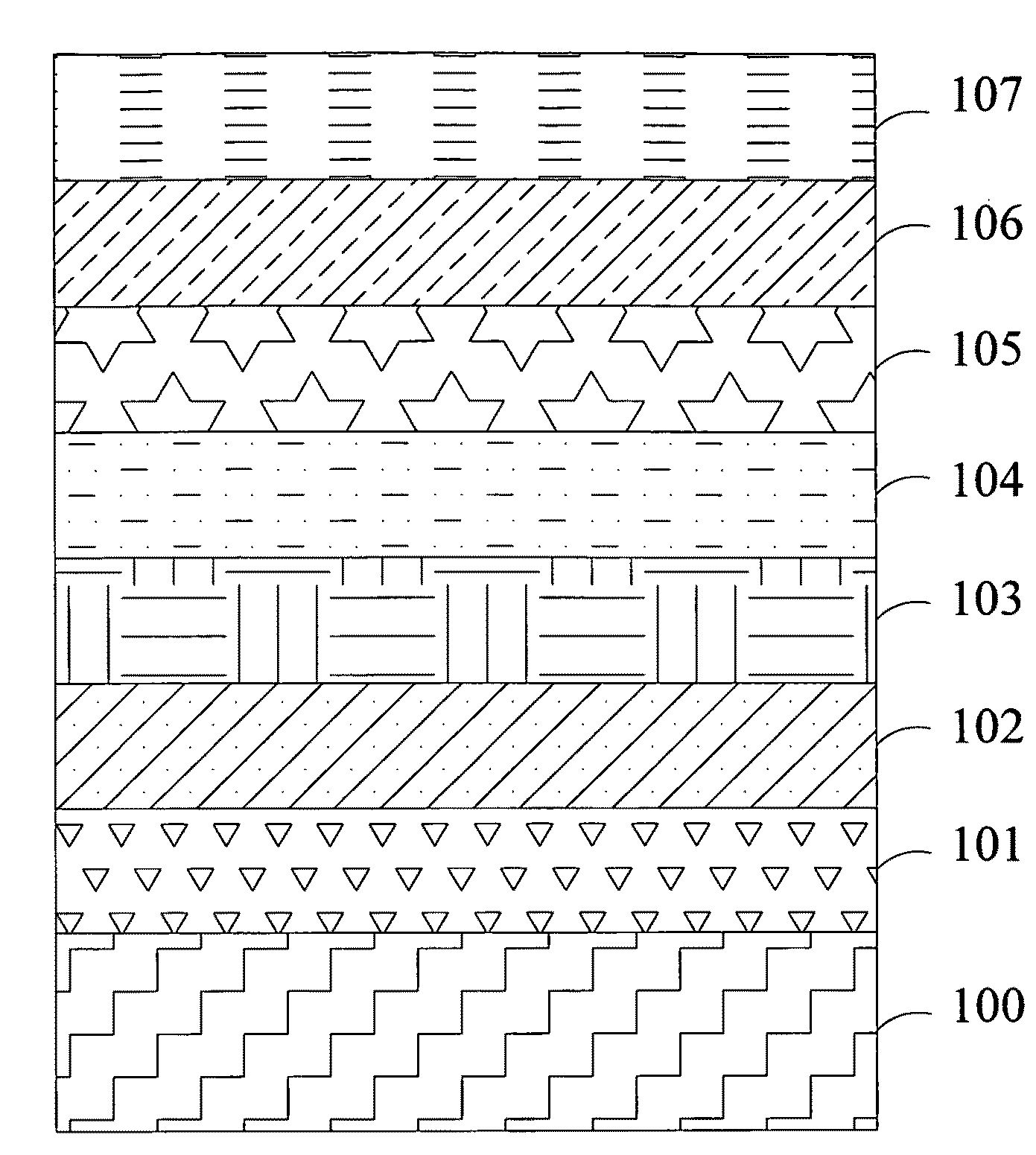

Indium bump device structure and preparation method for same

InactiveCN105826421AImprove structural strengthAvoid sheddingFinal product manufactureSemiconductor devicesIndium bumpUltimate tensile strength

The invention relates to an indium bump device structure and a preparation method for the same and belongs to the technical field of preparation of indium bump devices. The device structure comprises a semiconductor substrate, a welding disk, a first passivation layer, a second passivation layer, a UBM metal layer and an indium bump, wherein the UBM metal layer comprises an adhesion layer, a blocking layer, a buffer layer and a wetting layer; and in the device structure, a part of the first passivation layer is covered by the adhesion layer, and a part of the adhesion layer is covered by the second passivation layer. High structural intensity is provided by the stacking structure, so that the structure composed of the indium bump and the UBM is prevented from being separated along an interface of the adhesion layer and the first passivation layer under effects of thermal stress when the device surfers from thermal shocks. In addition, internal stress changes between the substrate and the UBM during backflow are mitigated by setting of the buffer layer, so that the indium bump is prevented from being separated from the wetting layer under too large internal stress changes. Hence, the device structure provided by the invention has higher stability and a longer service life.

Owner:KUNMING INST OF PHYSICS

Method for forming solder bump

ActiveCN102496580ASmall sizeIncrease the number of function output portsSolid-state devicesSemiconductor/solid-state device manufacturingSolder pastePhotoresist

The invention provides a method for forming a solder bump. The method comprises the following steps of: forming a heat resistant metal layer and a metal wetting layer on a pad and a passivation layer of a chip in sequence; forming a photoresist on the metal wetting layer, wherein the photoresist is provided with an opening to expose the metal wetting layer above the pad of the chip; forming an adhesion layer and a barrier layer on the metal wetting layer in the opening in sequence; forming solder paste on the barrier layer; removing the photoresist; etching the heat resistant metal layer and the metal wetting layer on the passivation layer until the passivation layer is exposed; and ensuring the solder paste to reflow to form a pillar bump. The method has the effect of improving the electrical property and reliability of the solder bump and is suitable for chip scale package with the requirements of fine pad pitch and multiple output functions.

Owner:NANTONG FUJITSU MICROELECTRONICS

Fabrication method of gallium nitride-based compound semiconductor

InactiveUS20110003420A1Improve crystal qualityProtect the surfaceSemiconductor/solid-state device manufacturingSemiconductor devicesGallium nitrideZinc

The present invention discloses a method for fabricating gallium nitride(GaN)-based compound semiconductors. Particularly, this invention relates to a method of forming a transition layer on a zinc oxide (ZnO)-based semiconductor layer by the steps of forming a wetting layer and making the wetting layer nitridation. The method not only provides a function of protecting the ZnO-based semiconductor layer, but also uses the transition layer as a buffer layer for a following epitaxial growth of a GaN-based semiconductor layer, and thus, the invention may improve the crystal quality of the GaN-based semiconductor layer effectively.

Owner:SINO AMERICAN SILICON PROD

![[wafer structure and bumping process thereof] [wafer structure and bumping process thereof]](https://images-eureka.patsnap.com/patent_img/a3553ac0-1a93-4187-89d5-ad0fce4e7d8e/US20050006759A1-20050113-D00000.png)

![[wafer structure and bumping process thereof] [wafer structure and bumping process thereof]](https://images-eureka.patsnap.com/patent_img/a3553ac0-1a93-4187-89d5-ad0fce4e7d8e/US20050006759A1-20050113-D00001.png)

![[wafer structure and bumping process thereof] [wafer structure and bumping process thereof]](https://images-eureka.patsnap.com/patent_img/a3553ac0-1a93-4187-89d5-ad0fce4e7d8e/US20050006759A1-20050113-D00002.png)