Wafer-level columnar bump packaging structure

A technology of column bumps and packaging structure, applied in electrical components, electric solid devices, circuits, etc., can solve the problems of affecting soldering quality, performance and reliability of solder bumps, etc., to increase the number of functional output ports, meet the density The effect of spacing

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

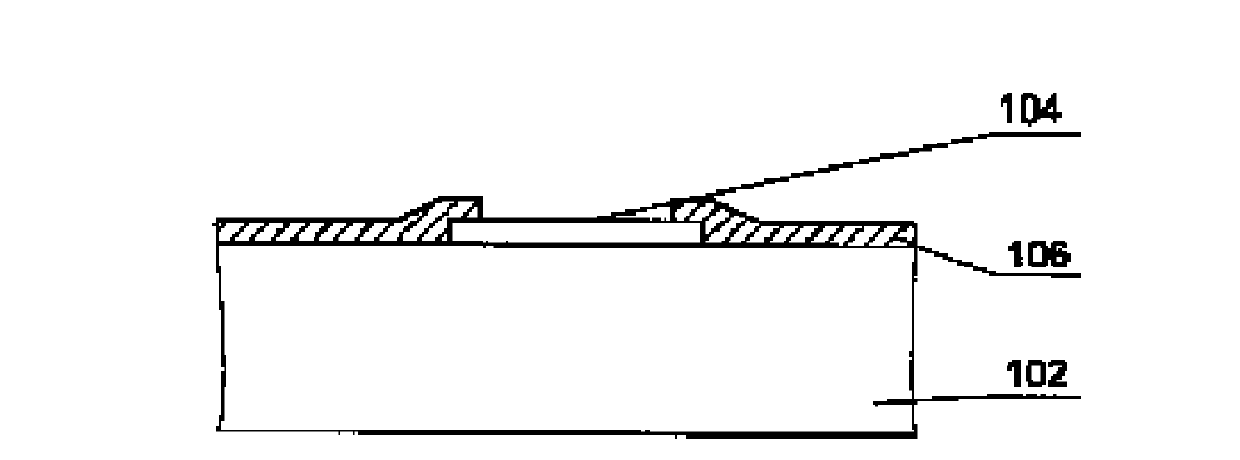

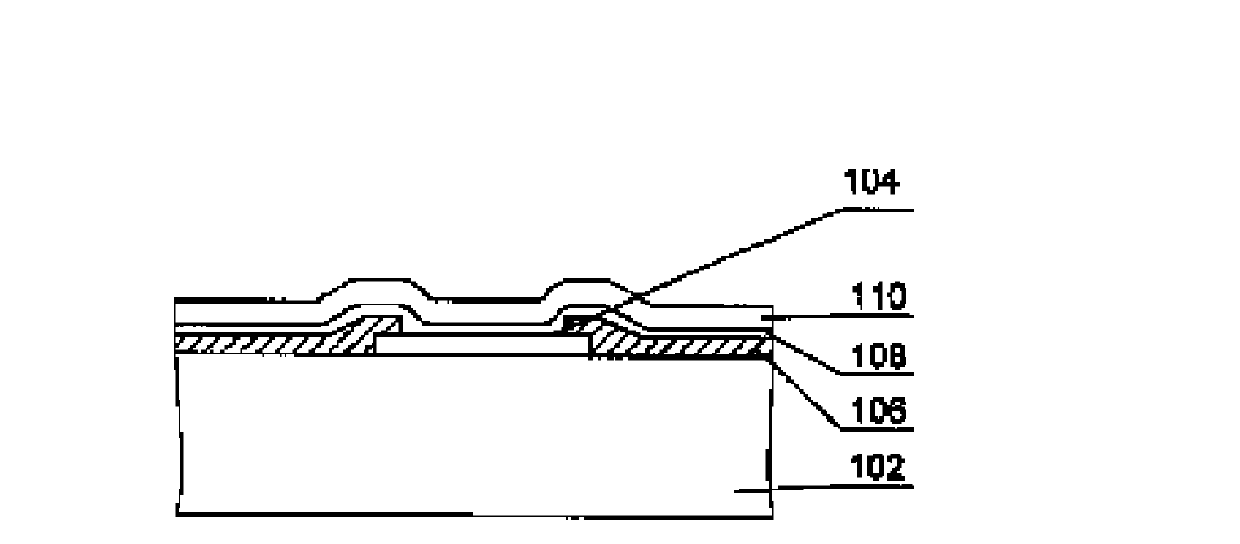

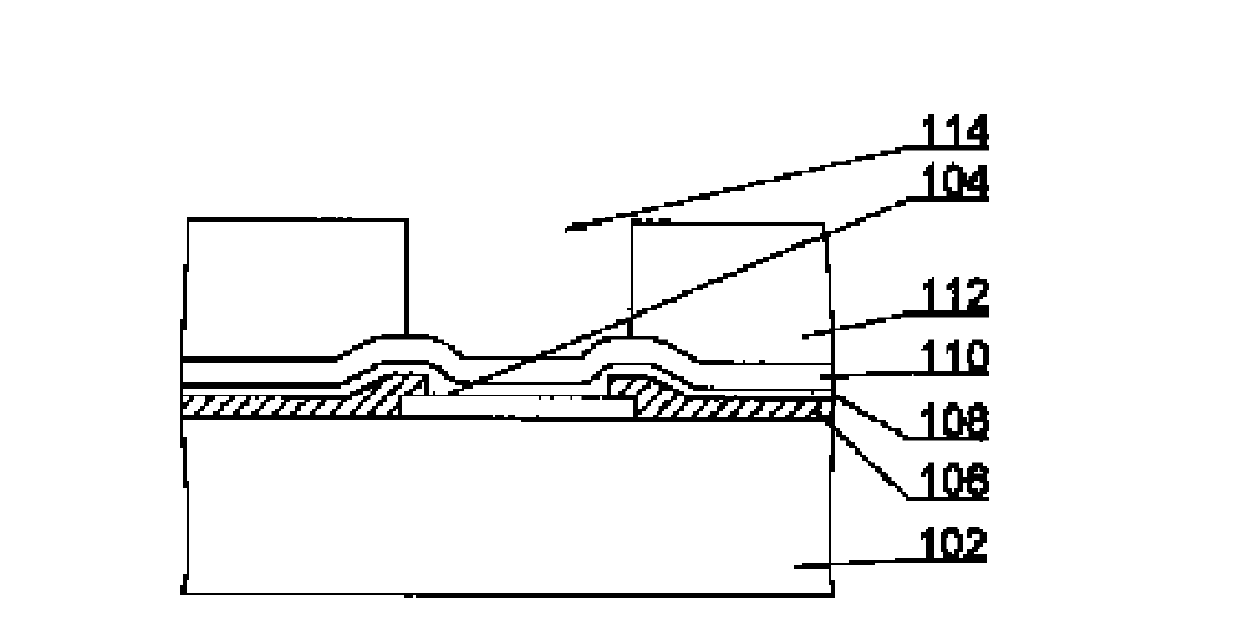

[0024] The specific embodiments of the present invention will be described in detail below in conjunction with the accompanying drawings.

[0025] figure 2 It is a schematic diagram of a wafer-level stud bump packaging structure of the present invention, and the packaging structure includes: a chip 300, a connection layer and a solder bump 308b; the upper surface of the chip 300 is provided with a pad 301 and a passivation layer 302, so The passivation layer 302 covers the upper surface of the chip 300 other than the pad 301; the bottom of the connection layer is placed on the pad 301 of the chip 300, and the top of the connection layer is provided with a solder bump 308b; Including heat-resistant metal layer 303, metal wetting layer 304, adhesion layer 306 and barrier layer 307 in sequence; the material of the heat-resistant metal layer 303 is titanium, chromium, tantalum or their combination; the metal wetting layer 304 The material is copper, aluminum, nickel or a combina...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More