Single-transistor DRAM (dynamic random access memory) unit based on source heterojunction and preparation method thereof

A single transistor, transistor technology, applied in the field of capacitorless dynamic random access memory preparation, can solve the problems of unfavorable DRAM working stability, high transistor working voltage, small signal margin, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

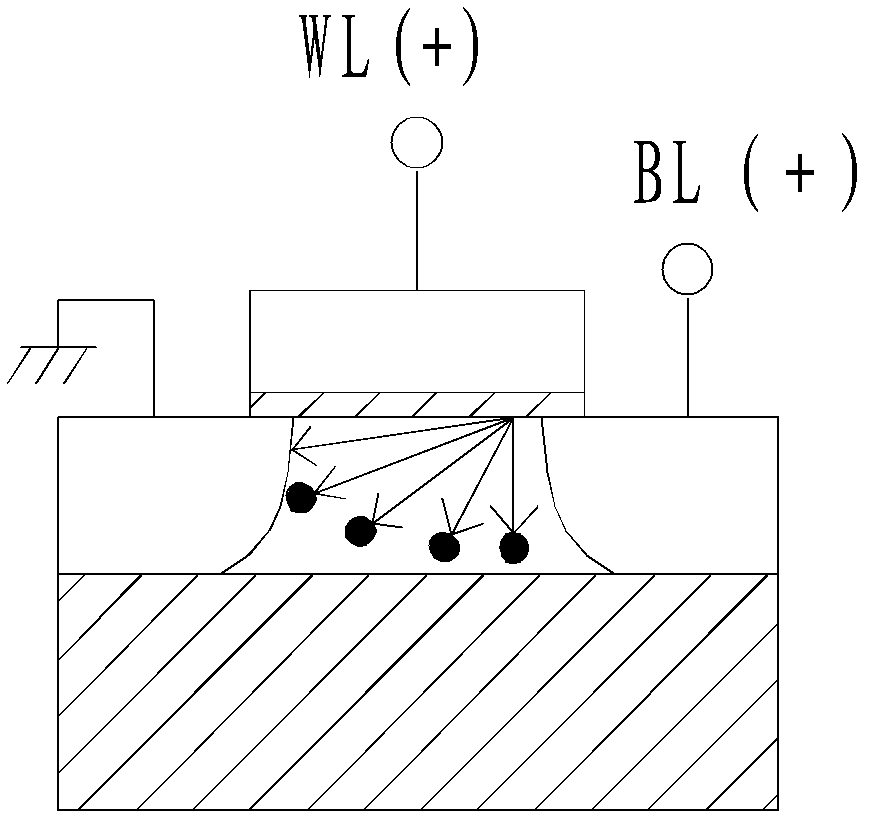

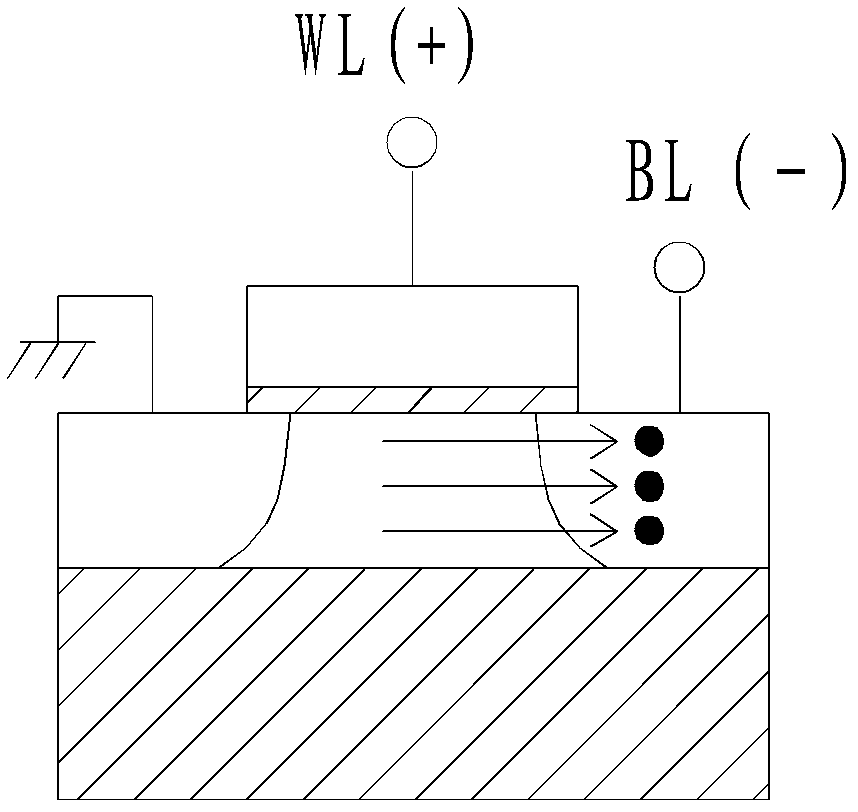

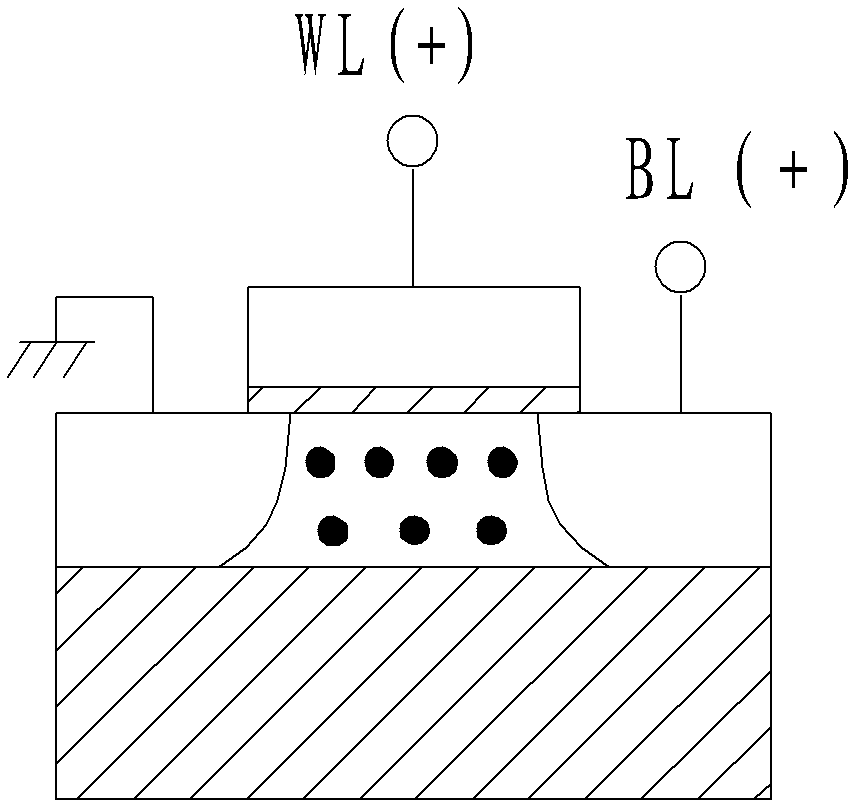

[0024] 1T-DRAM is generally a SOI (silicon-on-insulator) floating body transistor. When charging its body region, the write "1" operation is completed through the accumulation of holes in the body region. Accumulation results in a substrate effect, which reduces the threshold voltage of the transistor. When the body region is discharged, that is, the holes accumulated in the body region are released through the forward bias of the body-drain or body-source PN junction to complete the writing "0" operation. At this time, the substrate effect disappears. The threshold voltage returns to normal. Turn-on current increases. The read operation is to read the source-drain current when the transistor is turned on. Since the threshold voltages of the "1" and "0" states are different, the source-drain currents of the two are also different. When the source-drain current is large, it means the readout is "1", and when the source-drain current is small, it means that the read is "0".

...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More