Packaging substrate and method of fabricating the same

A technology of packaging substrate and manufacturing method, which is applied in semiconductor/solid-state device manufacturing, electrical components, electric solid-state devices, etc., can solve the problems of unfavorable thinness of electronic products, large thickness of packaging substrate, and difficulty in miniaturization, etc., and achieve electrical signal The effect of shortening the transfer path, reducing the overall thickness, and increasing the yield

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

[0071] see Figure 2A to Figure 2I , which is a cross-sectional view of the first embodiment of the packaging substrate and its manufacturing method of the present invention, wherein, Figure 2G 'and Figure 2G "for Figure 2G Different implementations of the top view of , Figure 2H 'and Figure 2I ’ respectively Figure 2H and Figure 2I Another implementation method of .

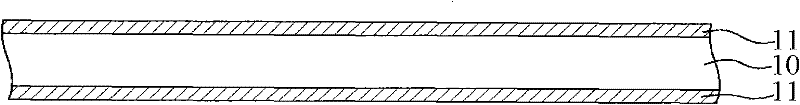

[0072] like Figure 2A As shown, a metal plate 20 is provided having opposing first and second surfaces 20a, 20b.

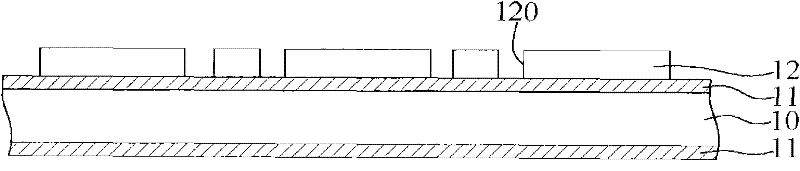

[0073] like Figure 2B As shown, a resist layer 21 is formed on the first surface 20a, and the resist layer 21 has a plurality of resist layer openings 210 exposing the first surface 20a.

[0074] like Figure 2C As shown, the metal plate 20 not covered by the resistive layer 21 is removed to form a concave portion 200 and a plurality of metal protrusions 201 as circuit layers.

[0075] like Figure 2D As shown, the resistance layer 21 is removed, and the circuit layer (ie, the m...

no. 2 example

[0087] see Figure 3A to Figure 3D , which is a cross-sectional view of the second embodiment of the packaging substrate and its manufacturing method of the present invention, wherein, Figure 3D 'for Figure 3D Another implementation method of .

[0088] like Figure 3A shown, which is a continuation from Figure 2D , forming a dielectric layer 22 on the first surface 20 a and the concave portion 200 , and the material of the dielectric layer 22 is epoxy resin (epoxy).

[0089] like Figure 3B As shown, a plurality of openings 220 for contact pads are formed in the dielectric layer 22 to expose each of the contact pads 201 b correspondingly. The method of forming the openings 220 for contact pads can be laser ablation or exposure and development.

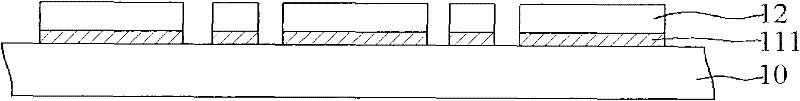

[0090] like Figure 3C As shown, part of the thickness of the metal plate 20 is removed to expose the metal protrusions 201 .

[0091] like Figure 3D As shown, an insulating protection layer 29 covering the metal protrusio...

no. 3 example

[0094] see Figure 4A to Figure 4D , which is a cross-sectional view of the third embodiment of the packaging substrate and its manufacturing method of the present invention, wherein, Figure 4D 'for Figure 4D Another implementation method of .

[0095] The third embodiment is substantially the same as the second embodiment, the main difference being that the material of the dielectric layer 22 in this embodiment is a solder resist material, which is different from the epoxy resin in the second embodiment.

[0096]The present invention also provides another packaging substrate, including: a dielectric layer 22, which has an opposite external surface 22a and a crystal mounting surface 22b; and a circuit layer, embedded in the dielectric layer 22, and the circuit layer has solder The finger pad 201a, the contact pad 201b, and the circuit 201c electrically connecting the solder finger pad 201a and the contact pad 201b, the circuit layer is exposed on the crystal surface 22b, a...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com