Dual dielectric tri-gate field effect transistor

A technology of field effect transistor and double dielectric, applied in the field of tri-gate field effect transistor, can solve the problem of current increase and other problems

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0020] In the following description, numerous specific details are set forth, such as particular structures, components, materials, dimensions, processing steps and techniques, in order to provide a thorough understanding of the present invention. However, it will be understood by those skilled in the art that the present invention may be practiced with a wide variety of specific details. In other instances, well-known structures or process steps have not been described in detail in order to avoid obscuring the invention.

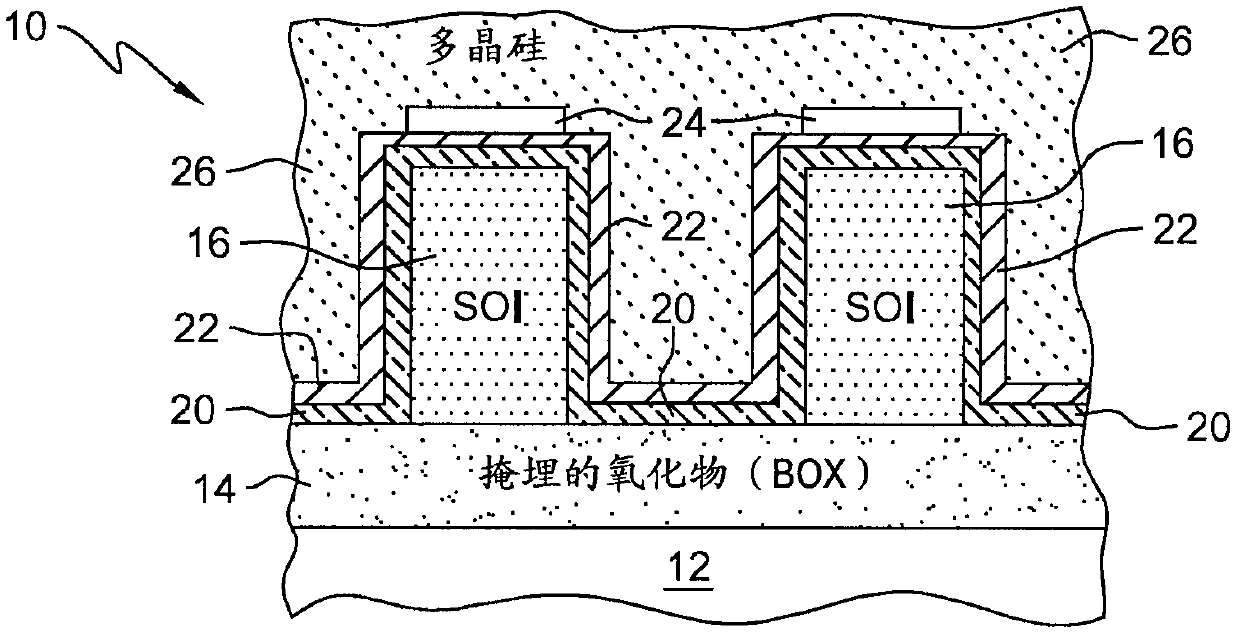

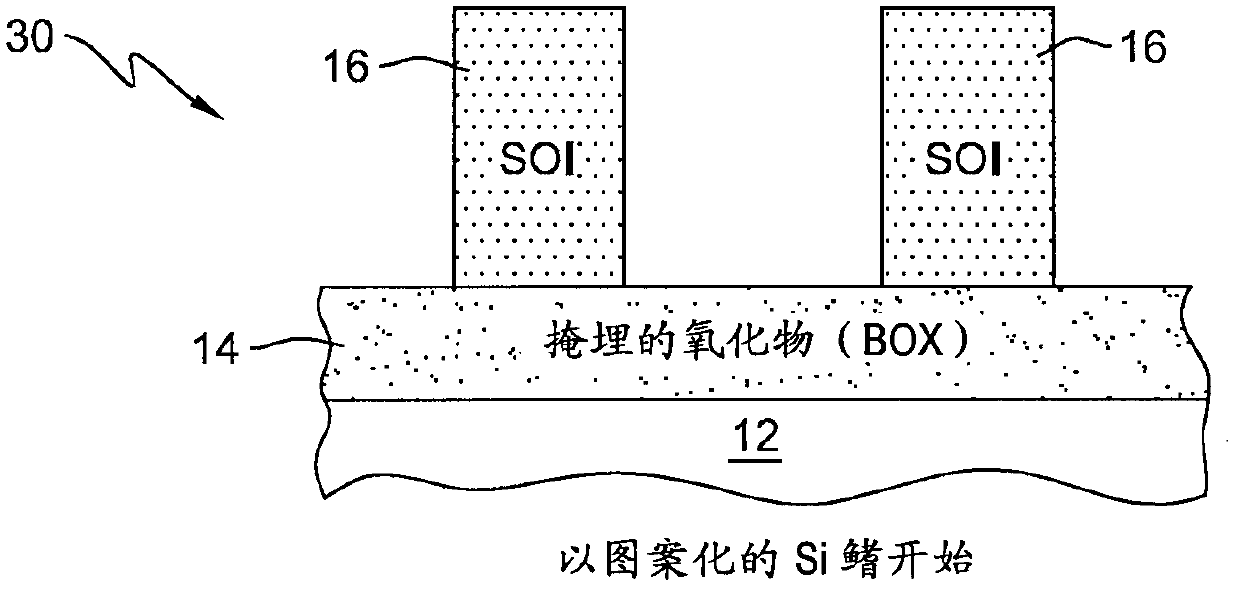

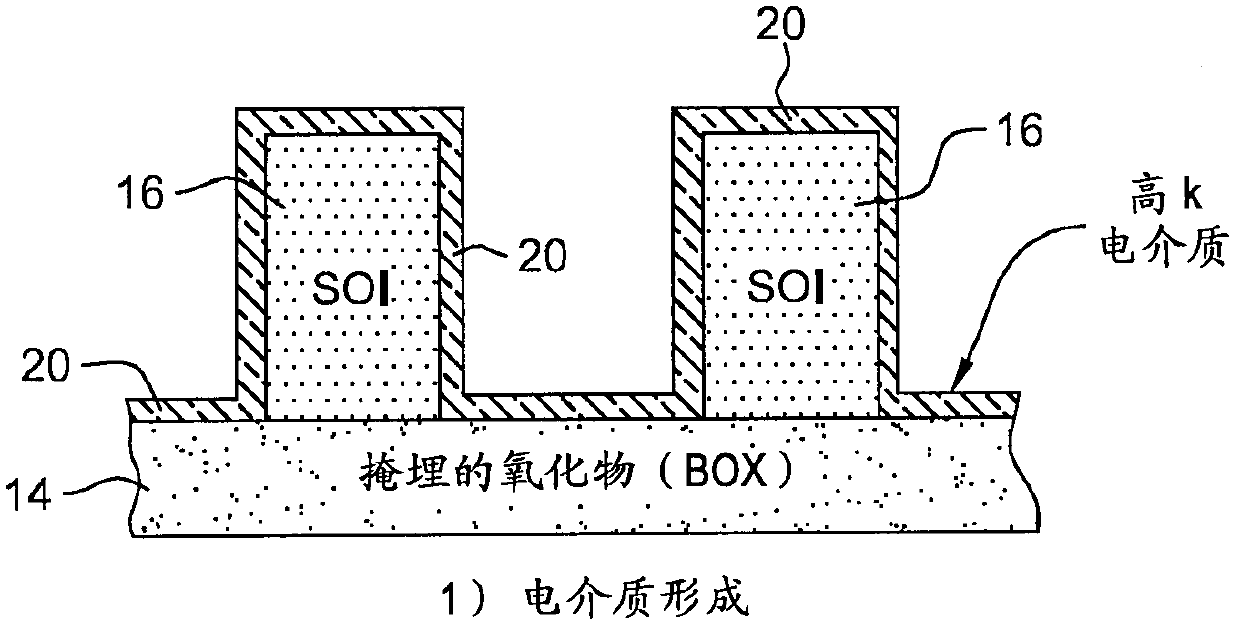

[0021] figure 1 A dual dielectric tri-gate structure according to one embodiment of the invention is shown. Structure 10 includes a base semiconductor substrate 12 , an insulator layer 14 , a plurality of semiconductor fins 16 , a high-k dielectric 20 , a metal layer 22 , a top gate dielectric 24 , and a gate electrode 26 .

[0022] The base semiconductor substrate layer 12 may comprise any semiconductor material, including but not limited to: Si, SiC, Si...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More