Cellular electric fusion chip device based on dispersed type side wall microelectrode array and processing process

A technology of microelectrode array and electrofusion, applied in stress-stimulated microbial growth methods, biochemical equipment and methods, biochemical instruments, etc., to achieve good flow characteristics, realize efficient queuing control and efficient fusion, and ensure reliability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

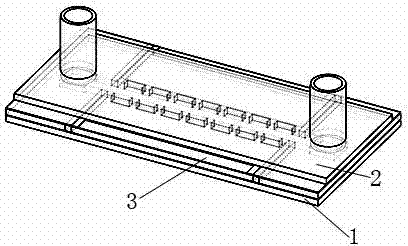

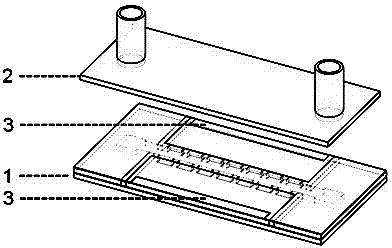

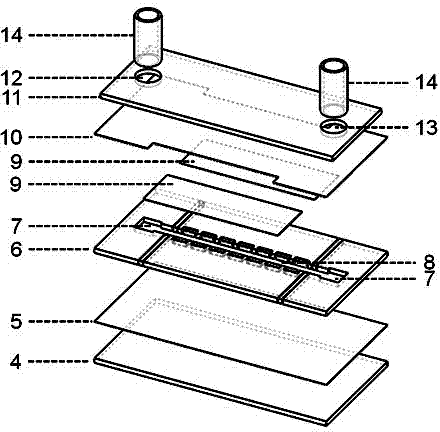

[0044] see Figure 1 to Figure 4 , the cell electrofusion chip device based on the discrete sidewall microelectrode array is composed of the cell electrofusion chip 1 and the flow path control layer 2 based on the discrete sidewall microelectrode array.

[0045] Cell electrofusion chip 1 based on discrete sidewall microelectrode arrays has a silicon base layer 4, a silicon dioxide insulating layer 5, and a top low-resistance silicon layer 6 from bottom to top (including discrete sidewall microelectrode arrays, insulation isolation structure and microchannel), aluminum lead layer 9, silicon dioxide passivation layer 10.

[0046] The silicon base layer 4 is selected to have a diameter of 3 to 4 For SOI wafers, the function of the silicon base layer is to provide a mechanical support layer with a thickness of 300-450 μm.

[0047] The silicon dioxide insulating layer 5 has a thickness of 0.5-2 μm, and its function is to provide good electrical insulation performance.

[0048] ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More