Gate-oxidizing-layer interface-trap density-testing structure and testing method

A technology of testing structure and interface traps, which is applied in the direction of single semiconductor device testing, semiconductor/solid-state device components, semiconductor devices, etc., can solve the problems of high test cost, long measurement time, low test efficiency, etc., to shorten the measurement time, Effects of area saving and test equipment cost saving

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0027] The specific implementation manners of the present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments. The following examples are used to illustrate the present invention, but are not intended to limit the scope of the present invention.

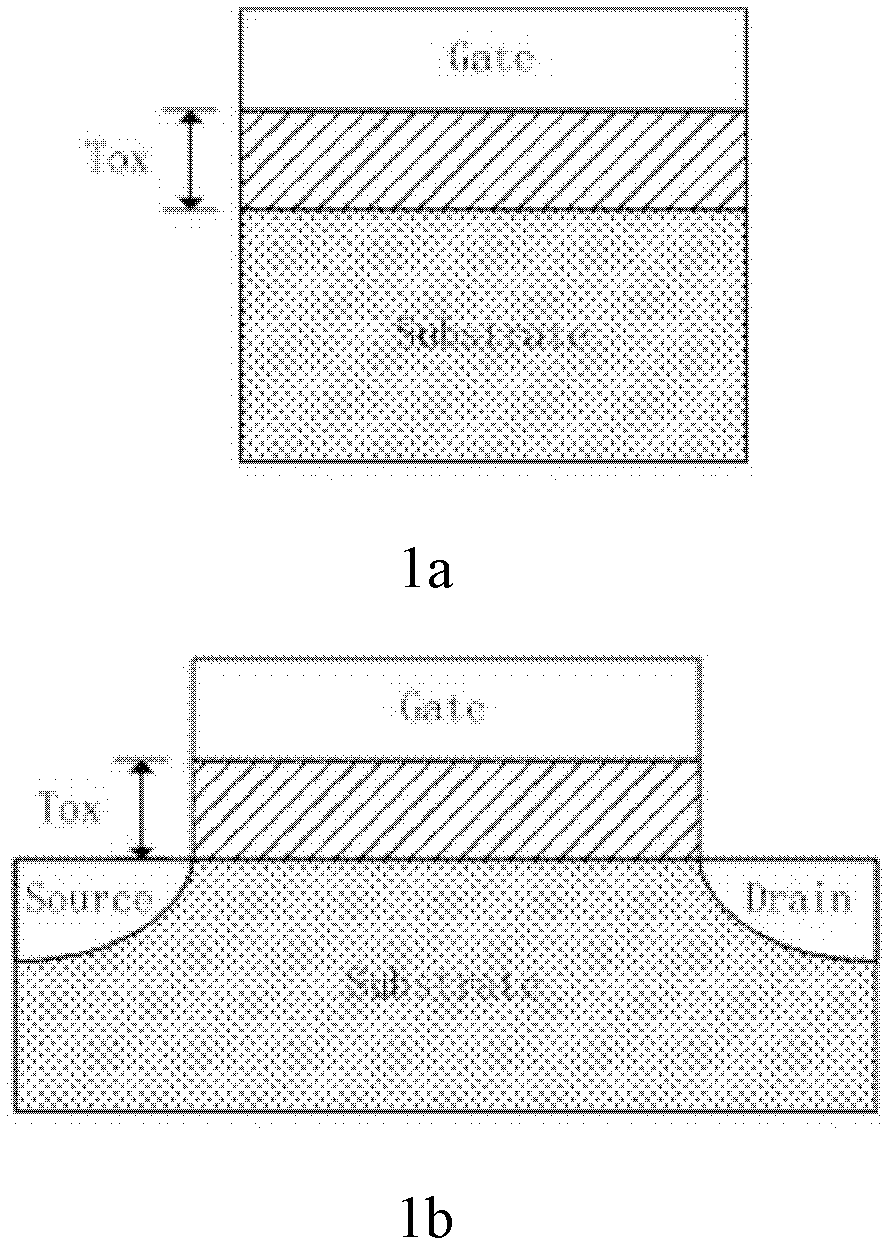

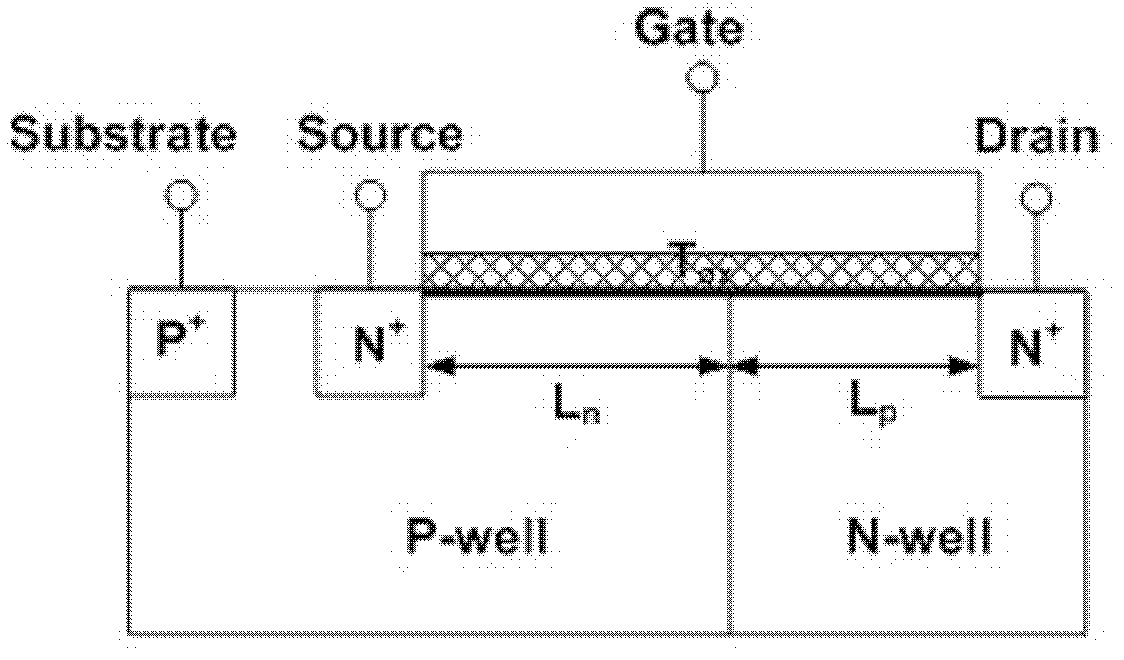

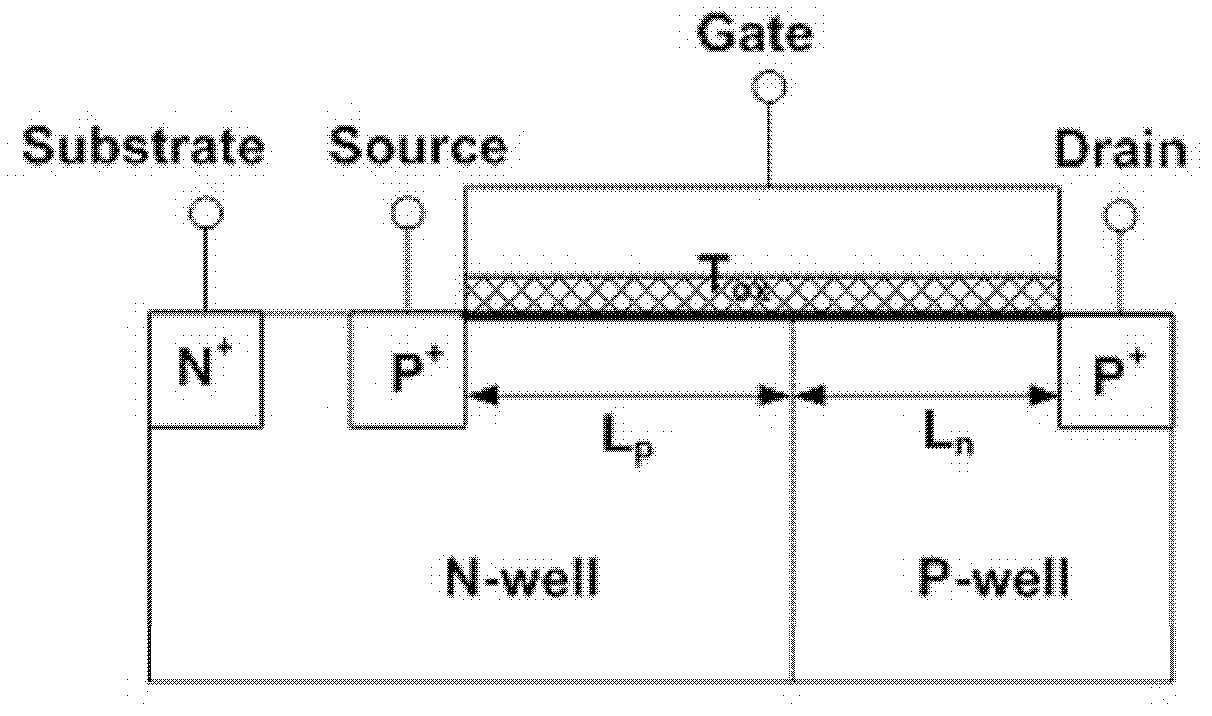

[0028] The invention provides a gate oxide layer interface trap density test structure, including n-type MOSFET and corresponding p-type gate oxide layer capacitance, or p-type MOSFET and corresponding n-type gate oxide layer capacitance; the n-type MOSFET and its corresponding The p-type gate oxide layer capacitance of the p-type MOSFET and its corresponding n-type gate oxide layer capacitor share the gate. Wherein, one side of the test structure is an n-type MOSFET, its n+ doping constitutes the source of the test structure, its p+ doping and p well region constitute the substrate of the test structure, and its gate constitutes the A part of the gate of the test structu...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More