Hermetic package method and structure of transistor base and transistor pin

A technology of hermetic packaging and transistors, which is applied in the direction of electrical components, electrical solid devices, semiconductor devices, etc., can solve the problems of silver-copper solder blocking the suspension hole, unstable production quality, and difficulty in plugging, and reduce cost consumption , The processing technology is simple and reasonable, and the effect of solving the blockage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0010] The present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments.

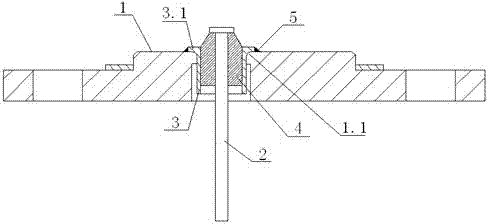

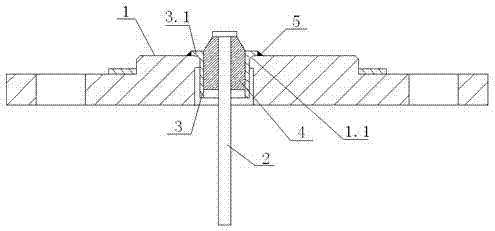

[0011] Embodiments of the present invention: a method for hermetically sealing transistor bases and pins according to the present invention is to make the pins 2 on the pins 2 in advance when the pins 2 of the transistor are fixed on the metal base 1 of the transistor. The glass insulator assembly composed of welding sleeve 3 and glass insulating layer 4, when manufacturing welding sleeve 3, a circle of flanging 3.1 is made on one end port of welding sleeve 3 at the same time, and its welding sleeve 3 can be made of metal materials, but It is preferably made of copper or copper alloy material in the prior art, and the pin 1 made of the glass insulator assembly is inserted into the pin hole of the metal tube base 1, and the flange 3.1 of the welding sleeve 3 is connected to the metal tube The seat 1 is in contact with each other, and then the w...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More