Method for manufacturing semiconductor device

A manufacturing method and semiconductor technology, applied in the fields of semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problems of current leakage, many crystal defects, uncontrollable impurity pattern shape, etc., and achieve the effect of less crystal defects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0035] Embodiment 1 will be described in detail below with reference to the drawings.

[0036] (Manufacturing method of IGBT)

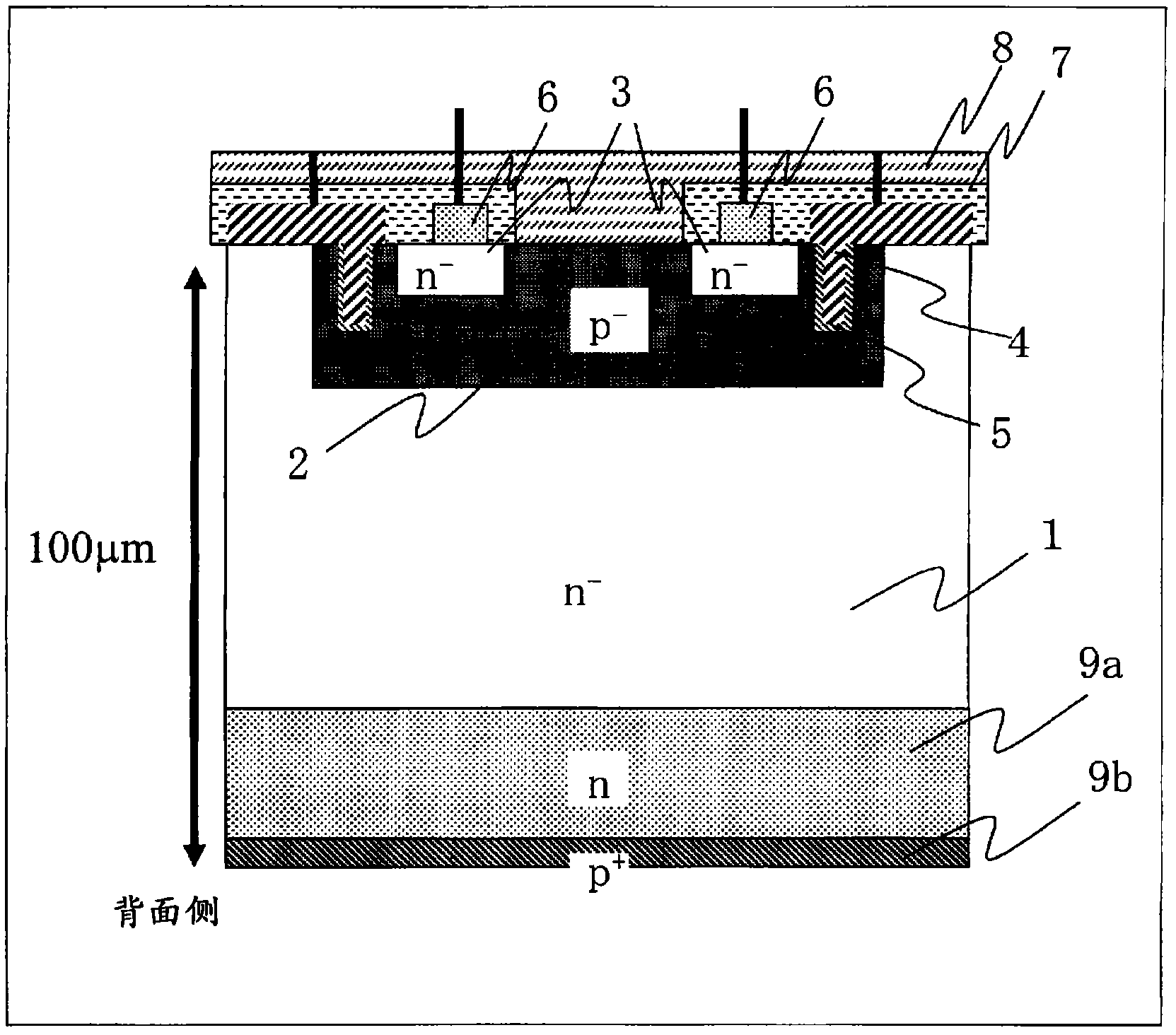

[0037] refer to Figure 1 to Figure 10 A method of manufacturing an IGBT will be described. In particular, the description will focus on the method of forming the field stop layer and the collector layer.

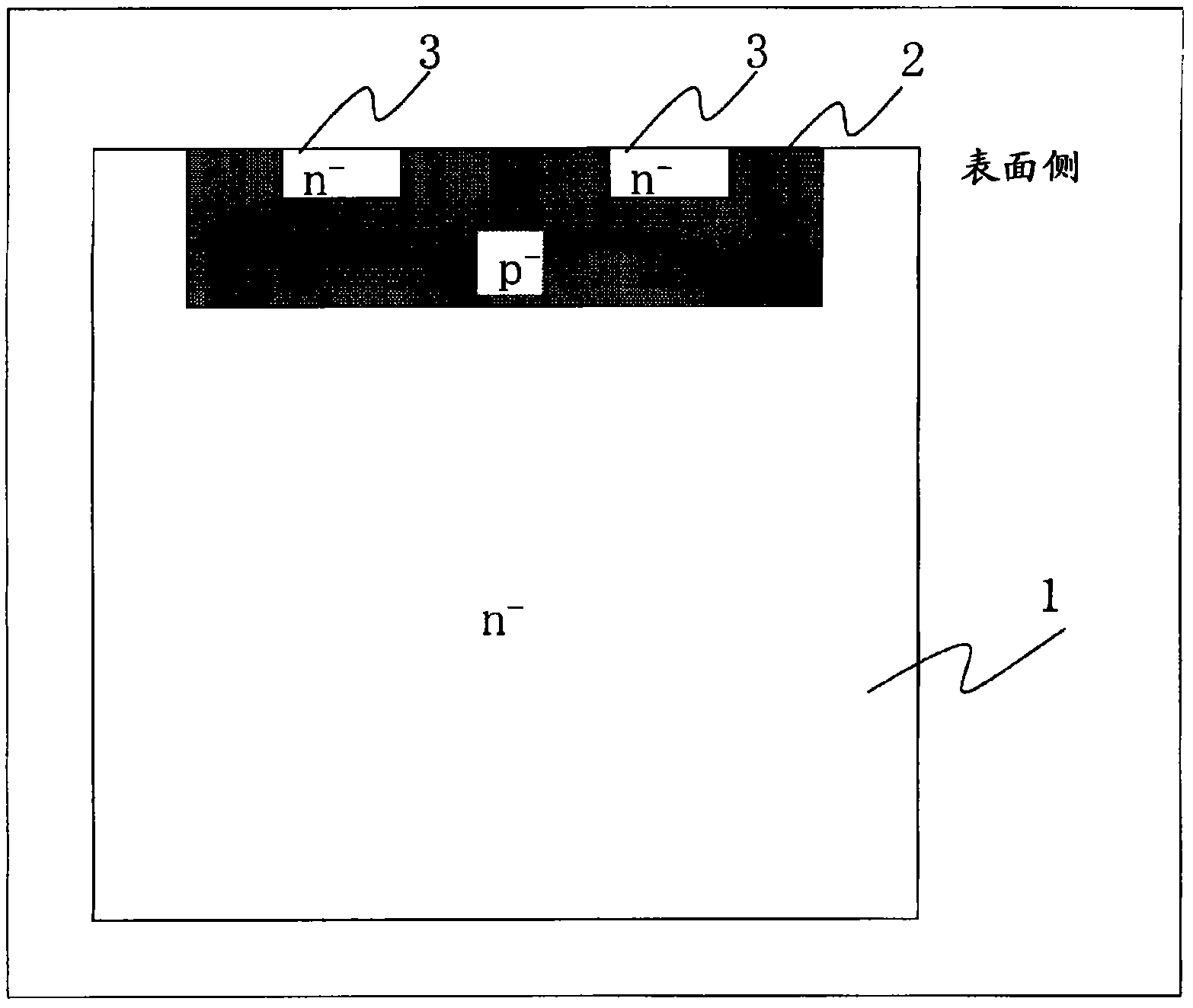

[0038] figure 1 A cross-sectional view of the main body schematically showing the manufacturing process of the IGBT 100 . IGBT 100 is formed using n-type silicon single crystal wafers (CZ, MCZ, FZ). IGBT100 has formed in n - The p-type body layer 2 on the type drift layer 1, and the n-type body layer formed on the surface part of the body layer 2 + Type source region 3. The body layer 2 and the source region 3 can be formed on the surface of the drift layer 1 by ion implantation technology.

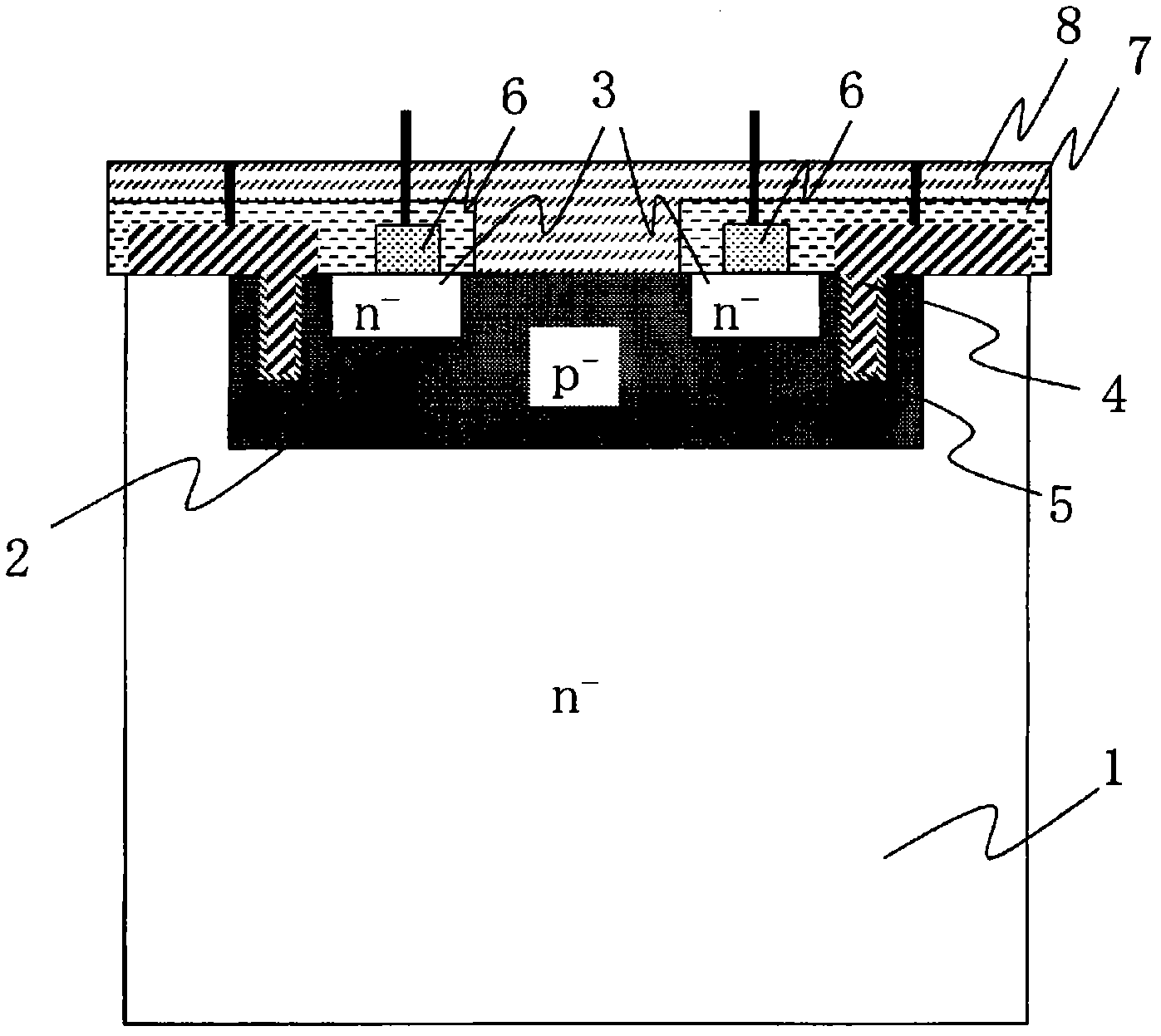

[0039] Next, if figure 2 As shown, trench gate 4 is formed on IGBT100. The trench gate 4 is opposed to the body layer 2 via the gate insulating fil...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| wavelength | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More