Task scheduling method and device based on multi-core system

A technology of task scheduling and scheduling algorithm, applied in multi-programming devices, program startup/switching, resource allocation, etc., can solve problems such as inability to achieve, achieve efficient scheduling, improve microprocessor resources, and improve throughput.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

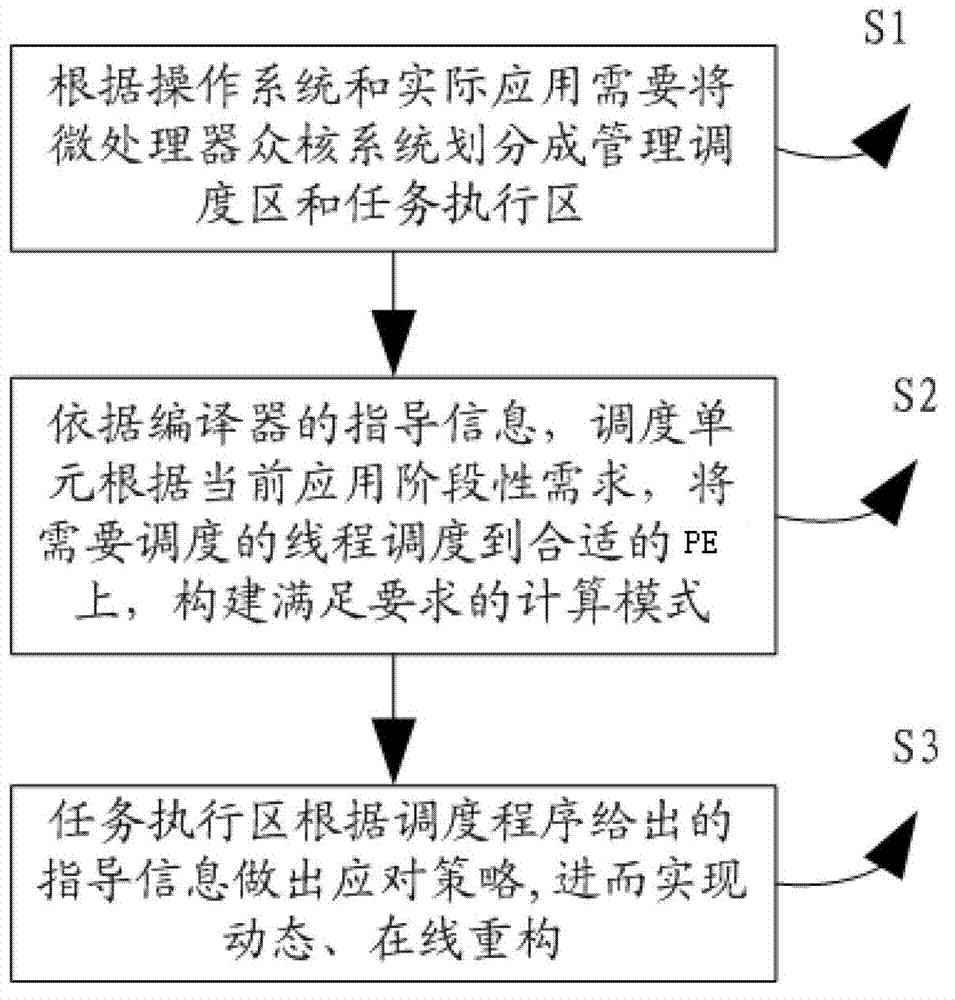

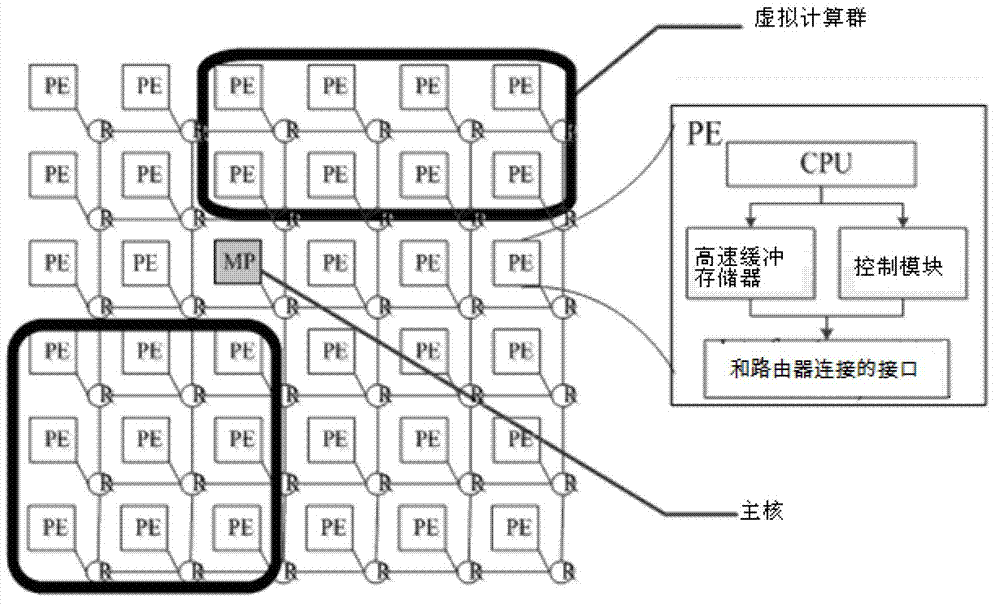

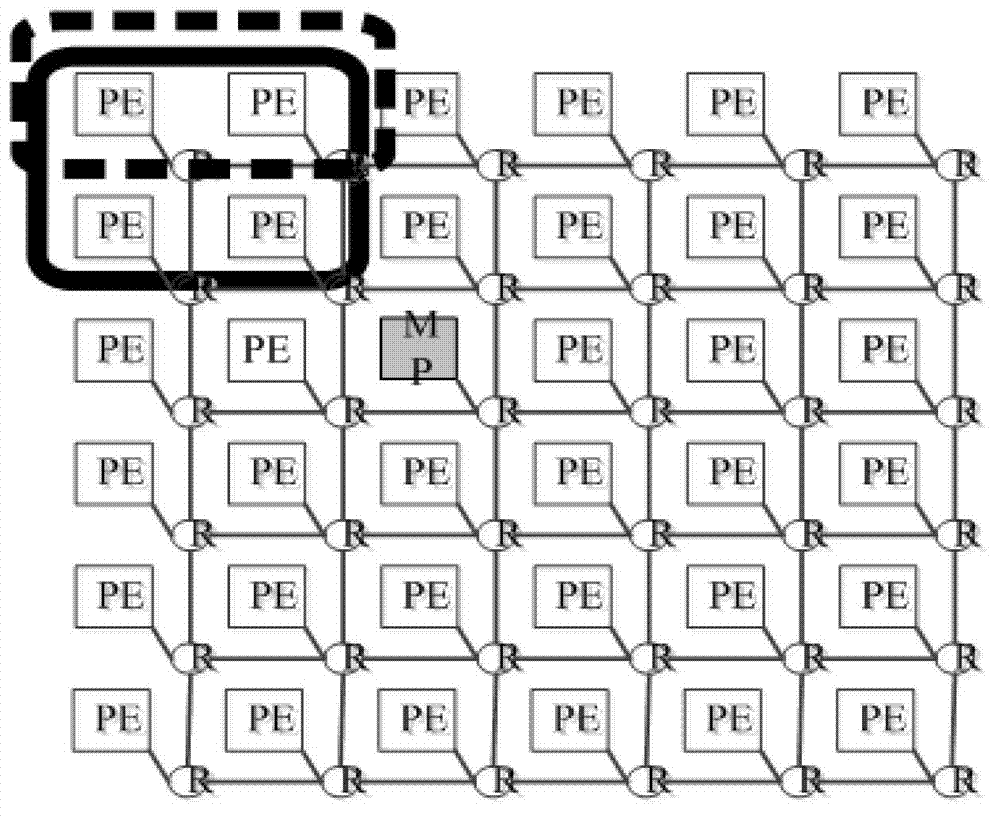

[0041] The embodiment of the present invention provides a task scheduling method and device based on a many-core system. By dividing the microprocessor many-core system into a management scheduling area and a task execution area, the scheduling algorithm and compilation The command command generates compilation information, and the scheduling unit receives the compilation information and schedules the threads that need to be scheduled to the appropriate PE, builds a computing mode that meets the requirements, and forms a suitable virtual computing group VCG by configuring the subnet; the task execution area is under the scheduling of the scheduling unit Make a response strategy, and then realize dynamic and online reconfiguration. This solution can improve the microprocessor resources of the many-core platform, efficiently schedule task sets, optimize system performance, and improve the throughput of the streamlined many-core system.

[0042] In order to make the object, techni...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com