Preparation method of trench grid VDMOS (vertical double-diffused metal oxide semiconductor) device with ultra-thin source region

A source area and device technology, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve problems such as limitations and difficulties, and achieve the effects of saving manufacturing costs, reducing parasitic resistance, and improving the ability to resist UIS failures

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

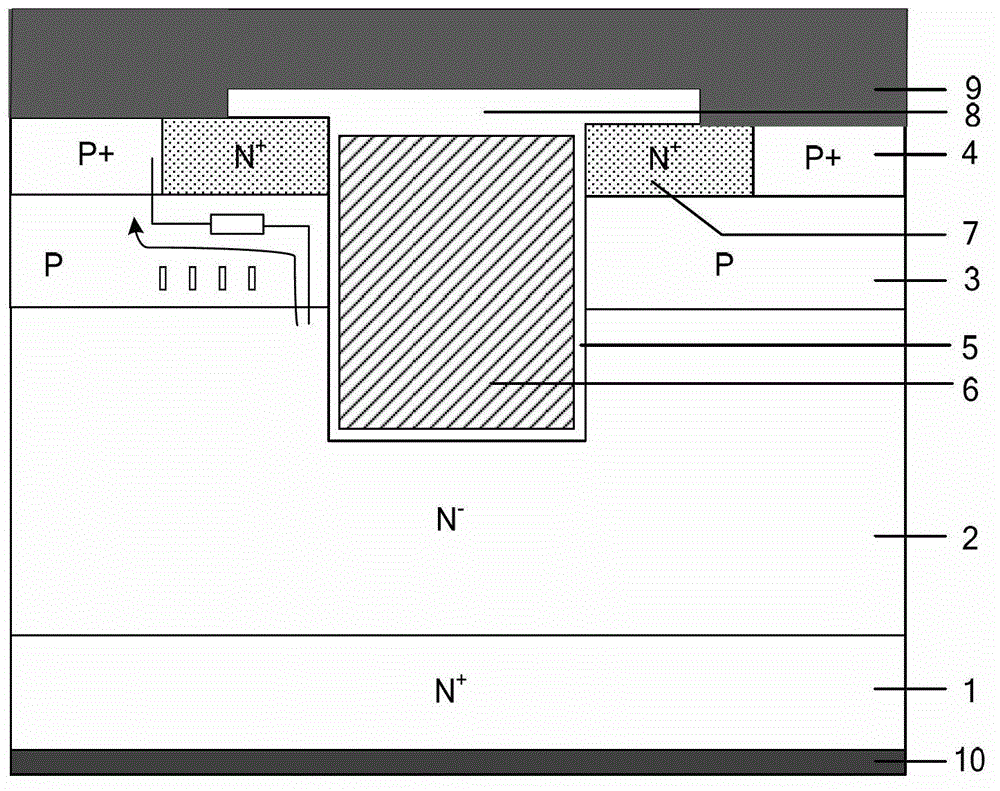

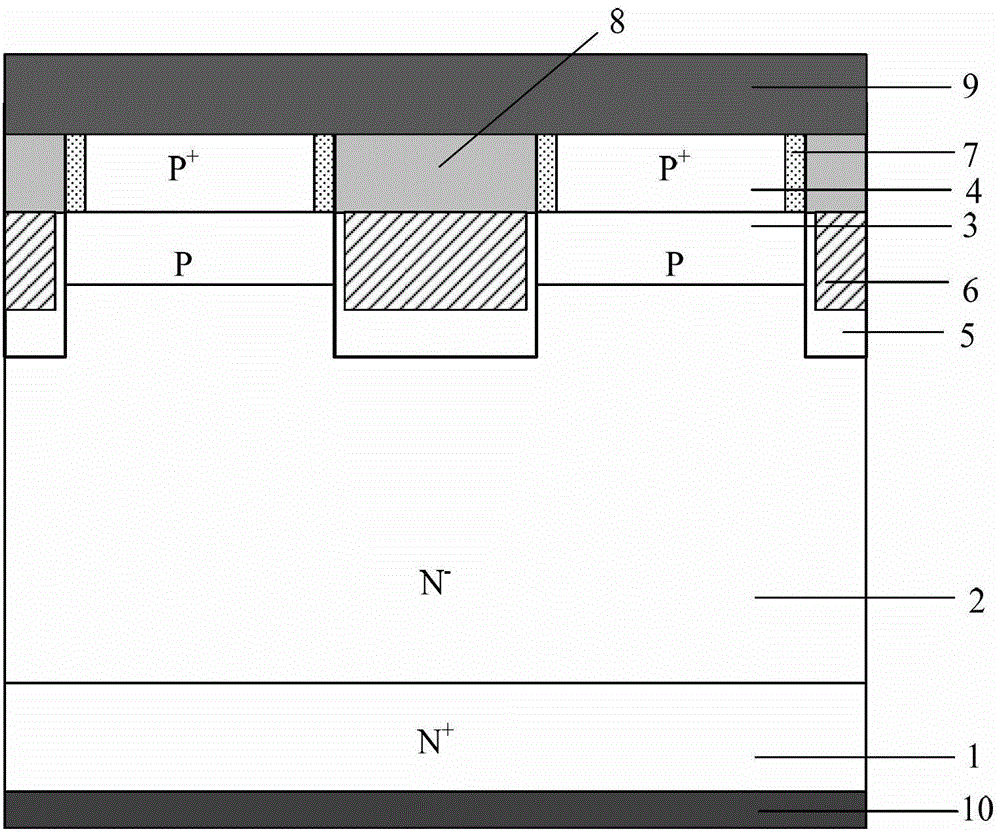

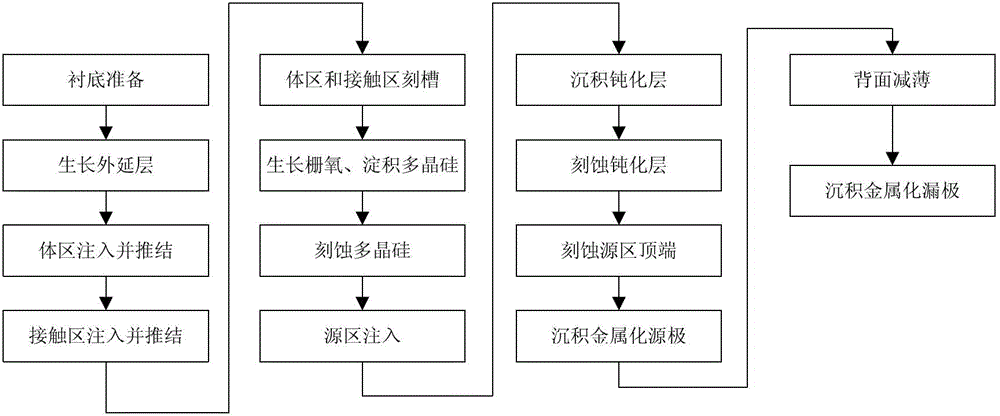

[0038] The process steps of a specific embodiment of a trench gate type VDMOS with an ultra-thin source region are described in detail below:

[0039] 1. Preparation of single crystal silicon, using N-type heavily doped single crystal silicon substrate 1, the doping concentration is 1.6×10 19 cm -3 , and its crystal orientation is .

[0040] 2. To grow the epitaxial layer, use the vapor phase epitaxy VPE method to grow 15μm N on the substrate 1 at a temperature of 1000 ℃ and a vacuum condition - Epitaxial layer 2, phosphorus doping concentration is 3.5 × 10 15 cm -3 .

[0041] 3. Boron ion implantation and push junction, using high-energy boron ion implantation with energy of 120KeV and a dose of 1×10 13 cm -2 , form P-type body region 3, and perform high-temperature push junction, so that the junction depth of P-type body region 3 is about 1.2 μm; use boron ion implantation with an energy of 100KeV and a dose of 2 × 10 15 cm -2 , forming P + Contact area 4, P + The ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More