Digital pulse width modulator circuit

A width modulation, digital pulse technology, applied in the field of electronics, can solve the problems of linearity limitation, delay calibration difficulty, not considering the mismatch of each delay unit, etc., to achieve the effect of low power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

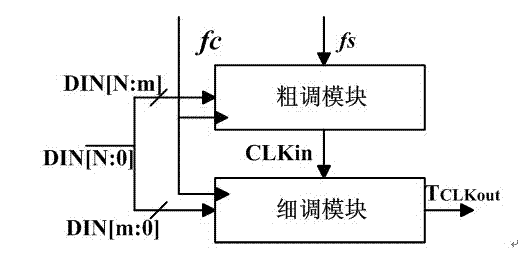

[0037] As a preferred embodiment of the present invention, the present invention discloses a digital pulse width modulator circuit, including a coarse adjustment module and a fine adjustment module, and also includes an RS flip-flop, and the coarse adjustment module includes a 5-bit counter and 5-bit comparators, the fine-tuning module includes a delay chain, "5 select 32" multiplexers and an all-digital logic control module; in the rough-tuning module, the input of the 5-bit counter is a standard clock signal, and the output Connect to the input terminal A of the comparator, and the input terminal B of the comparator is connected to the high 5-bit DIN of the control code DIN, the output signal of the coarse adjustment module is CNT_OUT, and the first digital controllable delay unit in the fine adjustment module The input port IN[0] is connected; in the fine-tuning module, the delay chain is composed of N digital controllable delay units, and in the implementation of 10bit DPWM...

Embodiment 2

[0039] As the best implementation mode of the present invention, technical scheme of the present invention is as follows:

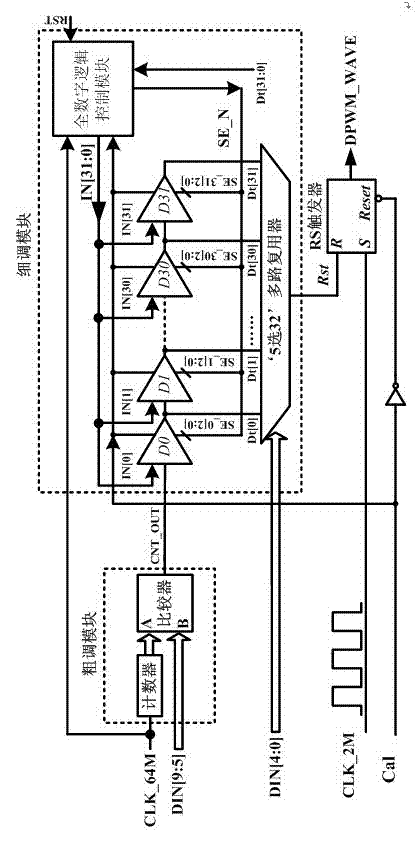

[0040] A digital pulse width modulator (such as figure 2 shown), consists of a coarse-tuning module, a fine-tuning module and an RS flip-flop. The circuit shown in the figure takes 2MHz output frequency and 10bit resolution as an example. The circuit has 4 input ports (2MHz standard clock signal CLK_2M, 64MHz standard clock signal CLK_64M, 10-bit binary DPWM control code DIN[9:0], calibration enable port Cal), one output port (DPWM output DPWM_WAVE), The 2MHz clock signal is obtained by frequency division of the 64MHz clock signal. For the digital pulse width modulator of the invention, it is characterized in that the rough adjustment module is composed of a counter and a comparator; the fine adjustment module is composed of a delay chain (composed of delay units D0~D31), '5 select 32 multiplexes Multiplexer' and full digital logic control module.

...

Embodiment 3

[0064] As a specific application example of the present invention is as follows:

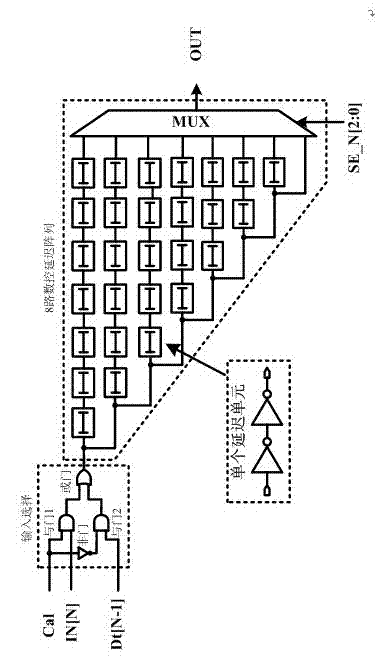

[0065] Such as figure 2As shown, the present invention relates to a binary control digital pulse width modulator circuit including a counter, a comparator, a controllable delay chain, an all-digital logic control module, a '5 to 32' multiplexer and an RS flip-flop. At the initial moment of system operation, the Reset signal is high potential, the Cal signal is high potential, all modules are reset, the delay chain verification starts, and the control code of the digital controllable delay unit is set to '100'. Firstly, by collecting the delay chain port signal Dt[31] and 64MHz pulse, the length of the delay chain transmission delay is judged, and the length of the transmission delay time of the entire delay chain is regulated through the binary code. After adjusting the entire delay chain to reach the target delay time, divide the delay chain into 2 equal parts, 4 equal parts, 8 equal parts an...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More