Method for growing germanium-silicon epitaxial layers

A silicon germanium epitaxy and epitaxial growth technology, which is applied in the direction of electrical components, semiconductor/solid-state device manufacturing, circuits, etc., can solve the problems of SiGe epitaxial layer critical thickness reduction, SiGe epitaxial layer surface roughness, etc., to improve rough surface morphology, Reduce the effect of strain relaxation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

specific Embodiment 1

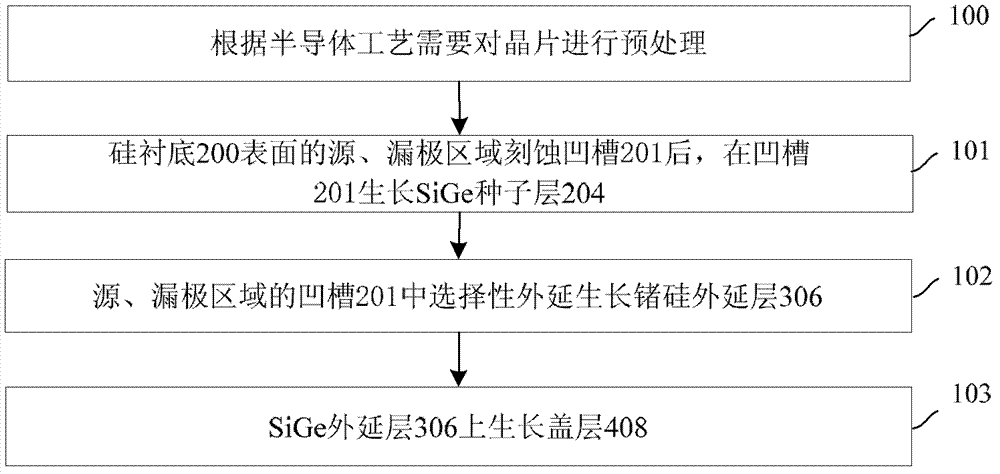

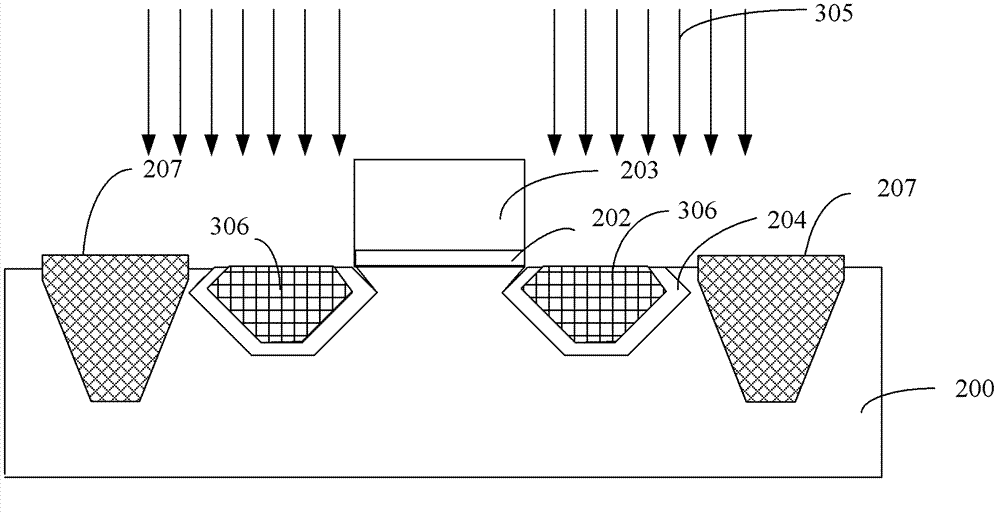

[0040] Combine below Figure 6-8 The process flow of the present invention for epitaxially growing a carbon-containing SiGe epitaxial layer will be described in detail.

[0041] Step 500, performing pretreatment on the wafer according to the requirements of the semiconductor process;

[0042] In this step, the pretreatment of the wafer includes removing the oxide layer and impurities on the surface of the silicon substrate. For a heavily doped silicon substrate, it must be considered whether a backseal is required to reduce the self-sufficiency in the subsequent selective epitaxial growth process. doping phenomenon.

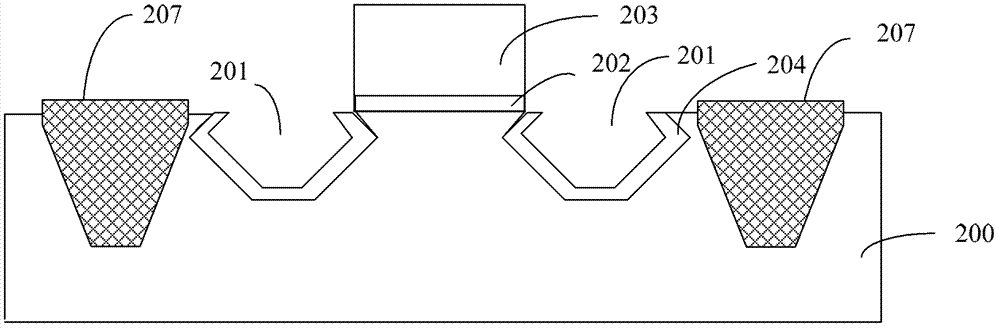

[0043] Step 501, after etching the groove 201 in the source and drain regions on the surface of the silicon substrate 200, grow a SiGe seed layer 204 on the surface of the groove 201 to form a Image 6 The schematic diagram of the cross-sectional structure shown;

[0044] In this step, if Image 6 As shown, the active regions are isolated by STI207, and the s...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More