Patents

Literature

115results about How to "Reduce lattice mismatch" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

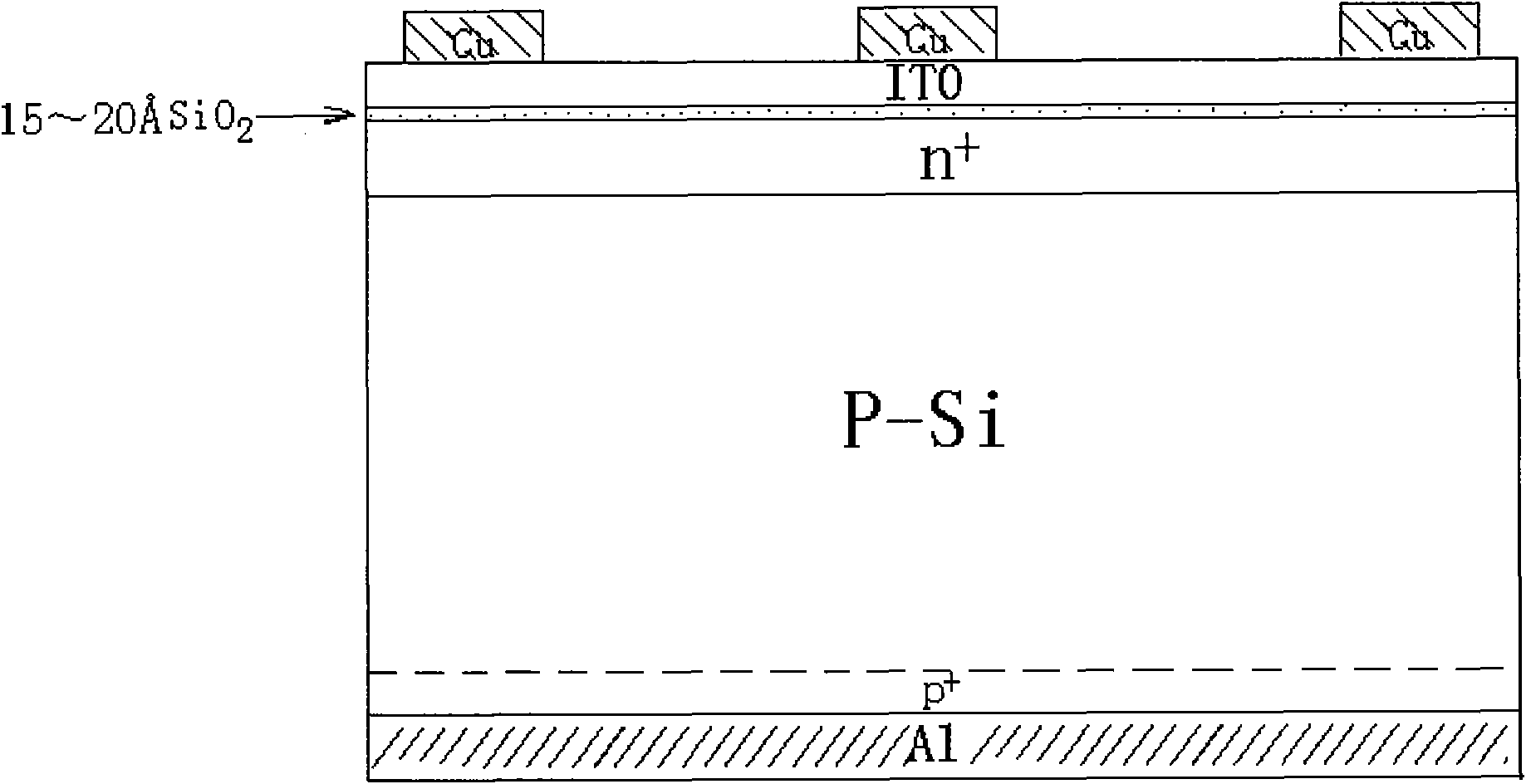

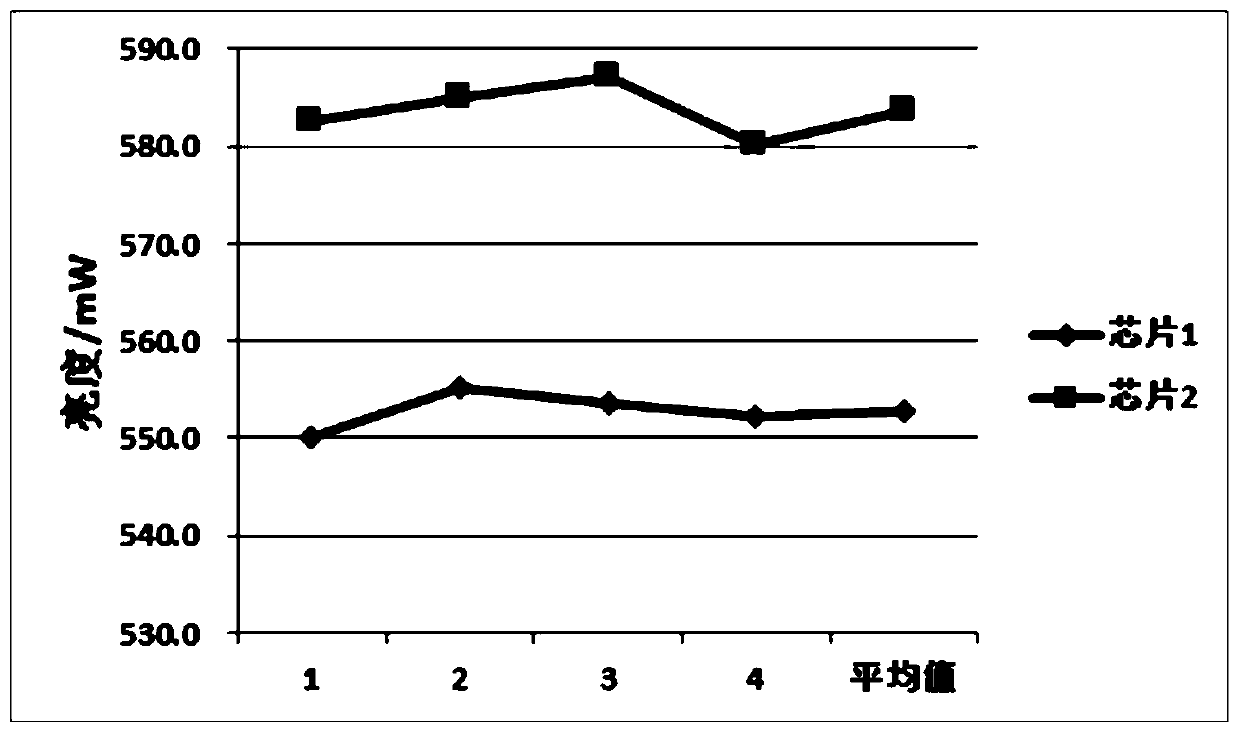

Novel SINP silicone blue-violet battery and preparation method thereof

InactiveCN101587913AImprove quantum efficiencyReduce the impactFinal product manufacturePhotovoltaic energy generationRadio frequency magnetron sputteringSingle crystal

he invention relates to a novel SINP silicone blue-violet battery and a preparation method thereof. The invention uses shallow junctions formed from thermally diffused phosphorus, an ultra-thin SiO2 layer formed by low-temperature thermal oxidization and an ITO dereflection / collection electrode film formed by RF magnetron sputtering to prepares a novel ITO / SiO2 / np blue-violet reinforced SINP silicone photo-battery. Preparation method of the invention is to take a silicon single crystal flake which is P type, and has crystallographic orientation of 100, electric resistivity of 2 2omega.cm and thickness of 220mu m, as a substrate. The substrate is cleaned and is etched by routine chemistry, and then is thermally diffused by POC3 liquid source to form n regions (the invention prepares two pieces of novel SINP photo-batteries, one being routine SINP photo-battery having emitting region square resistance of 10 Omega / square and junction depth of 1 Mu m, and the other one being SINP silicone blue-violet battery having emitting region square resistance of 37 Omega / square and junction depth of 0.4 Mu m). Removing the phosphorosilicate glass (HF:H2O=1:10) at front face; steaming Al at back of the silicon chip; thermally oxidizing the silicon chip at 400 to 500 DEG C and condition of V2:O2=4:1 for 15 to 30min to generate a layer of 15 to 20 ultra-thin SiO2 layer, and at the same time alloying the Al at the back. Then RF magnetron sputtering the ITO dereflection / collection electrode film (ITO film is also deposited on the glass to study electrooptical characteristic thereof) having high transmittance and high conductivity, and sputtering a Cu gate electrode by metal mask direct-current magnetron. Finally, cutting the outer edge part of the battery by a diamond excircle downward cutting / a dicing saw so as to prevent short circuit of the edge of the photo-battery.

Owner:SHANGHAI UNIV

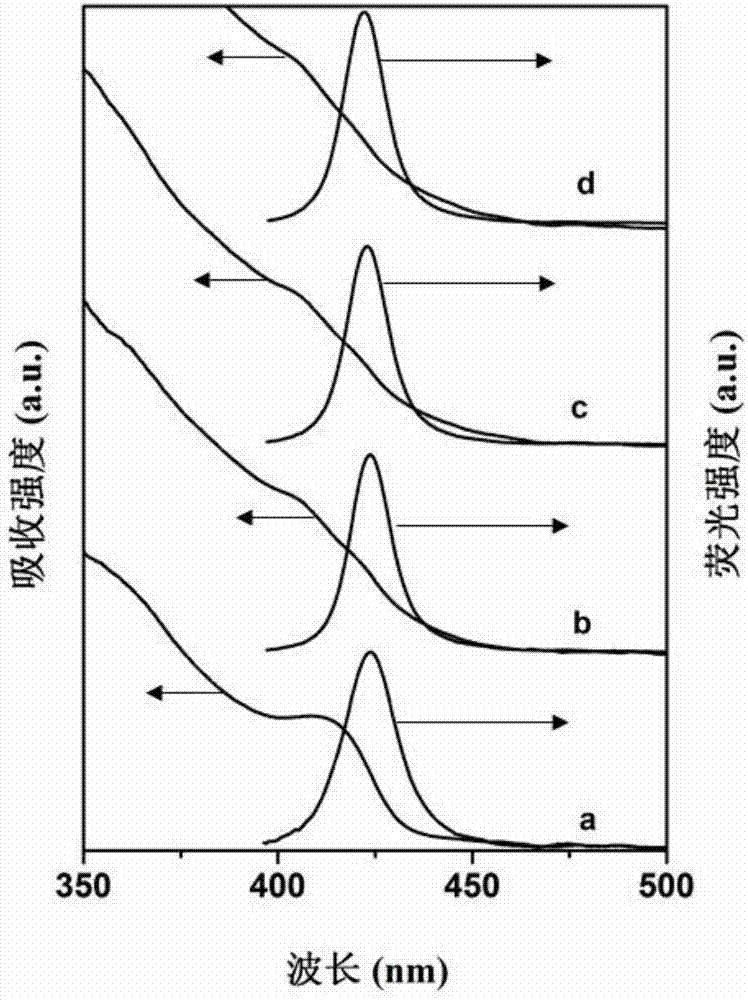

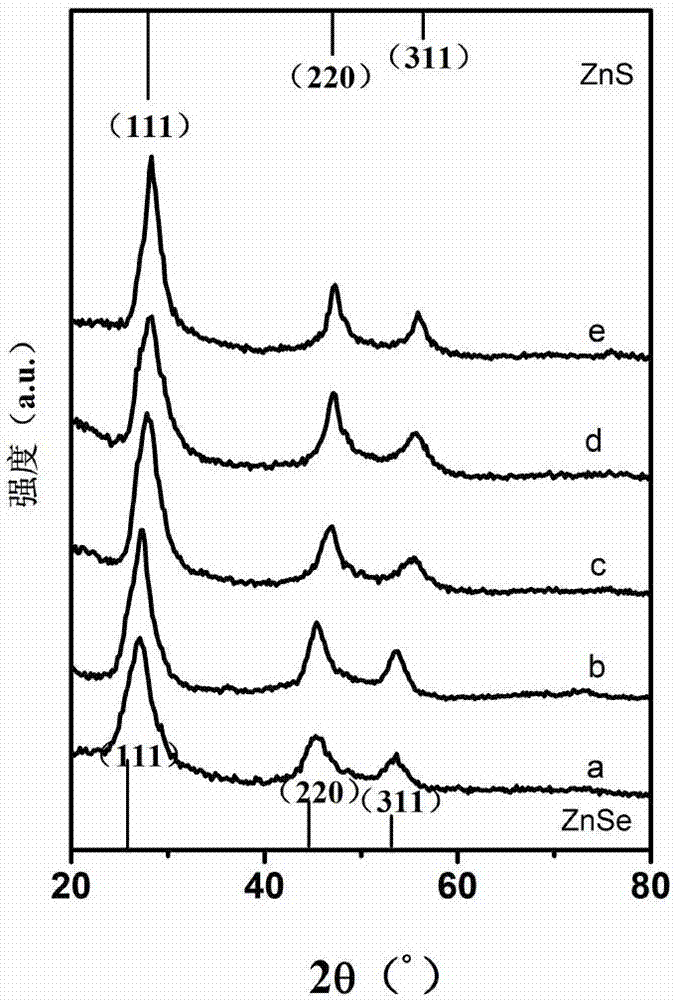

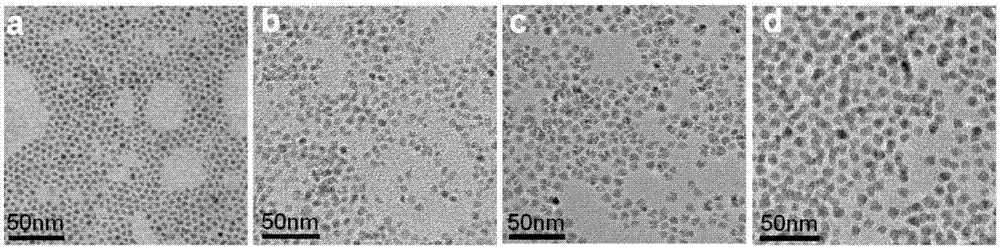

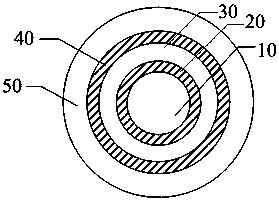

Nuclear-shell alloy quantum dots and preparation method thereof

InactiveCN107573923AReduce lattice mismatchImprove Lattice FitMaterial nanotechnologyNanoopticsQuantum yieldQuantum dot

The invention provides core-shell alloy quantum dots and a preparation method of the core-shell alloy quantum dots. The preparation method comprises the following steps: mixing a nucleation cation source, a nucleation anion source and a hydrocarbon organic solvent, and carrying out heat preservation at the nucleation temperature of 220-280 DEG C, thereby obtaining quantum dot nuclear bodies; mixing the obtained quantum dot nuclear bodies with a crusting cation source, a crusting anion source and a hydrocarbon organic solvent at the crusting temperature of 300 to 318 DEG C to obtain core-shellalloy quantum dots. By adopting the preparation method of the core-shell alloy quantum dots, quantum dot crystal nuclei are synthesized at lower temperature and a shell layer is grown at higher temperature later to obtain the core-shell alloy quantum dots with high quantum yield and good stability.

Owner:HENAN UNIVERSITY

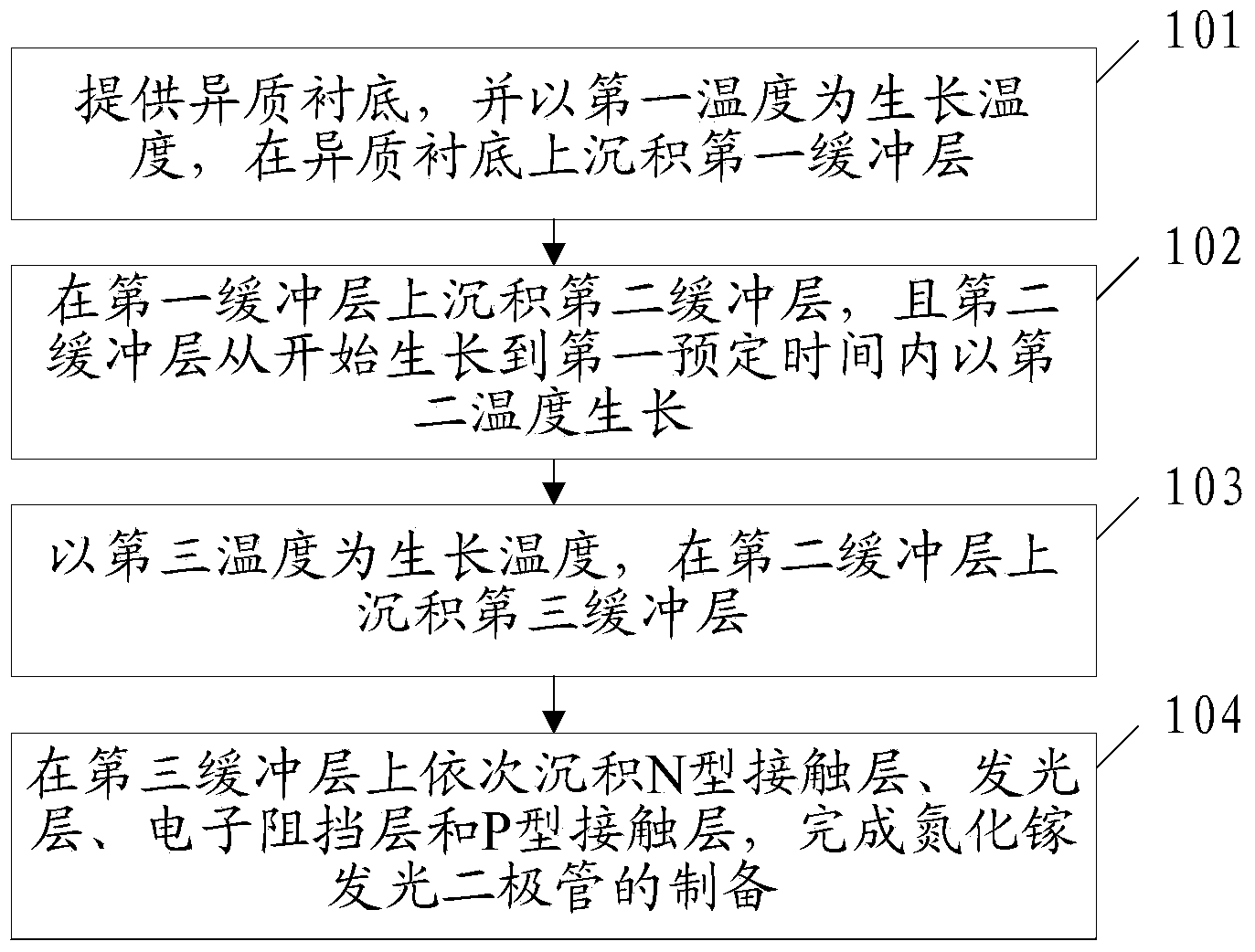

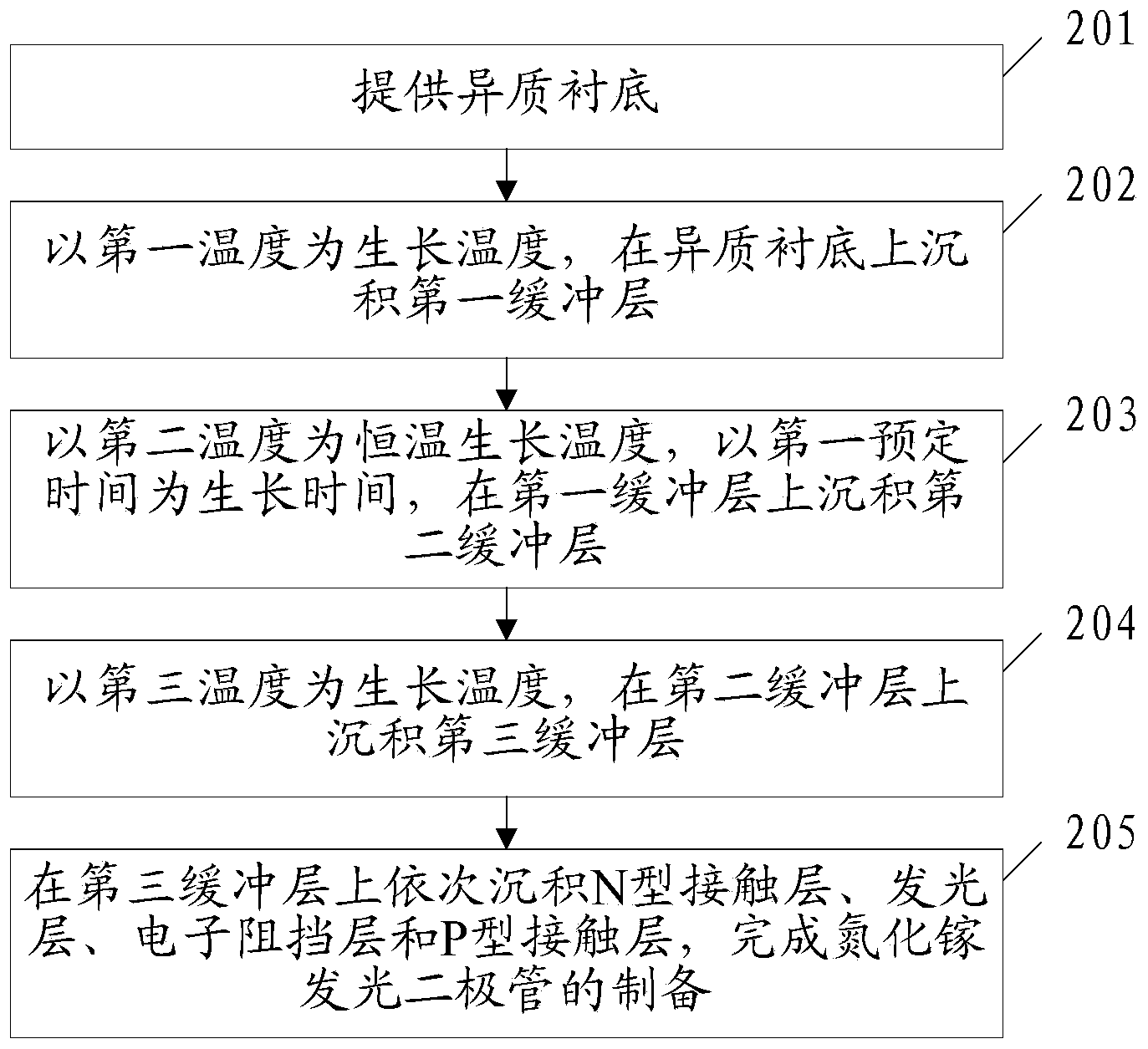

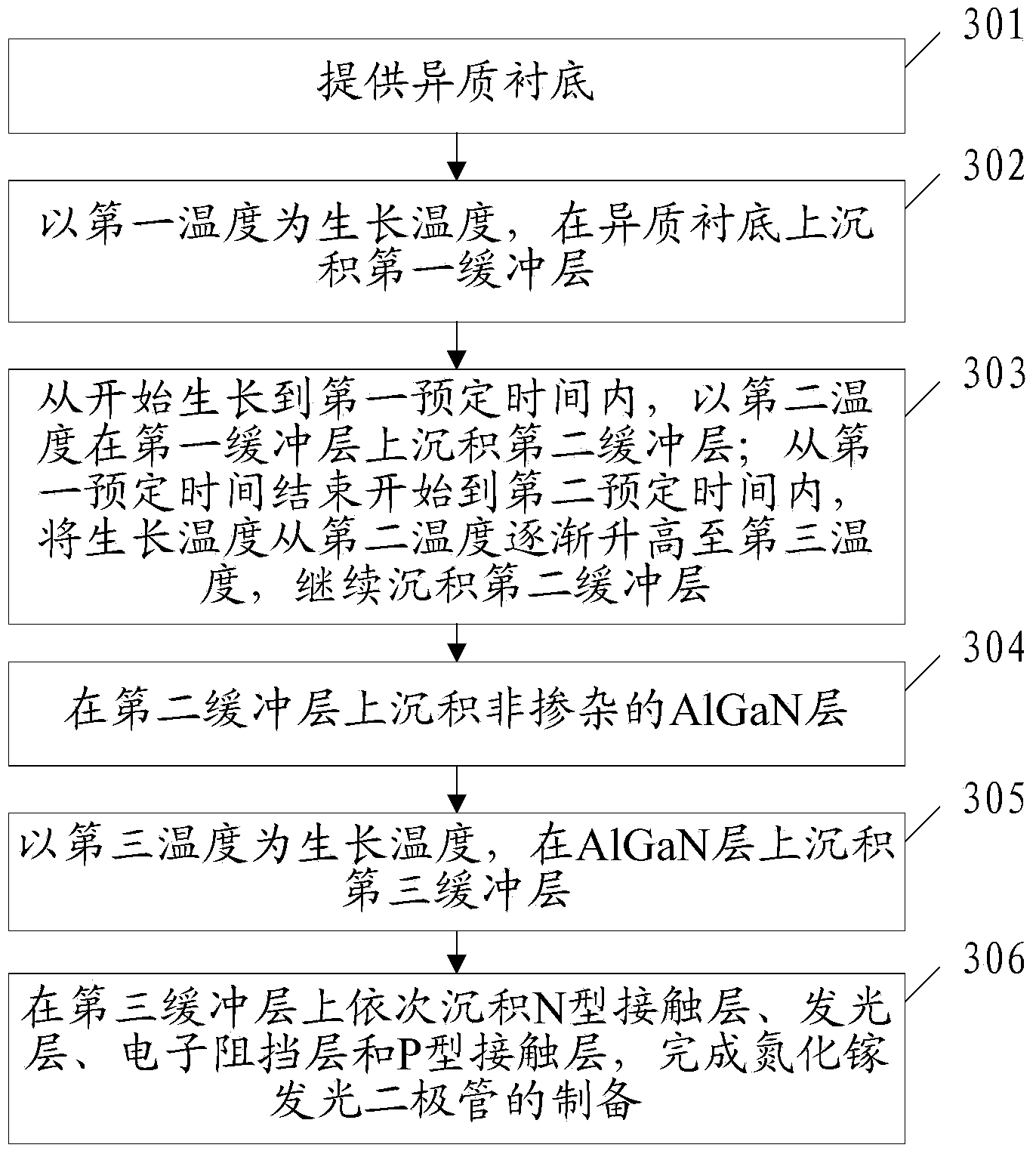

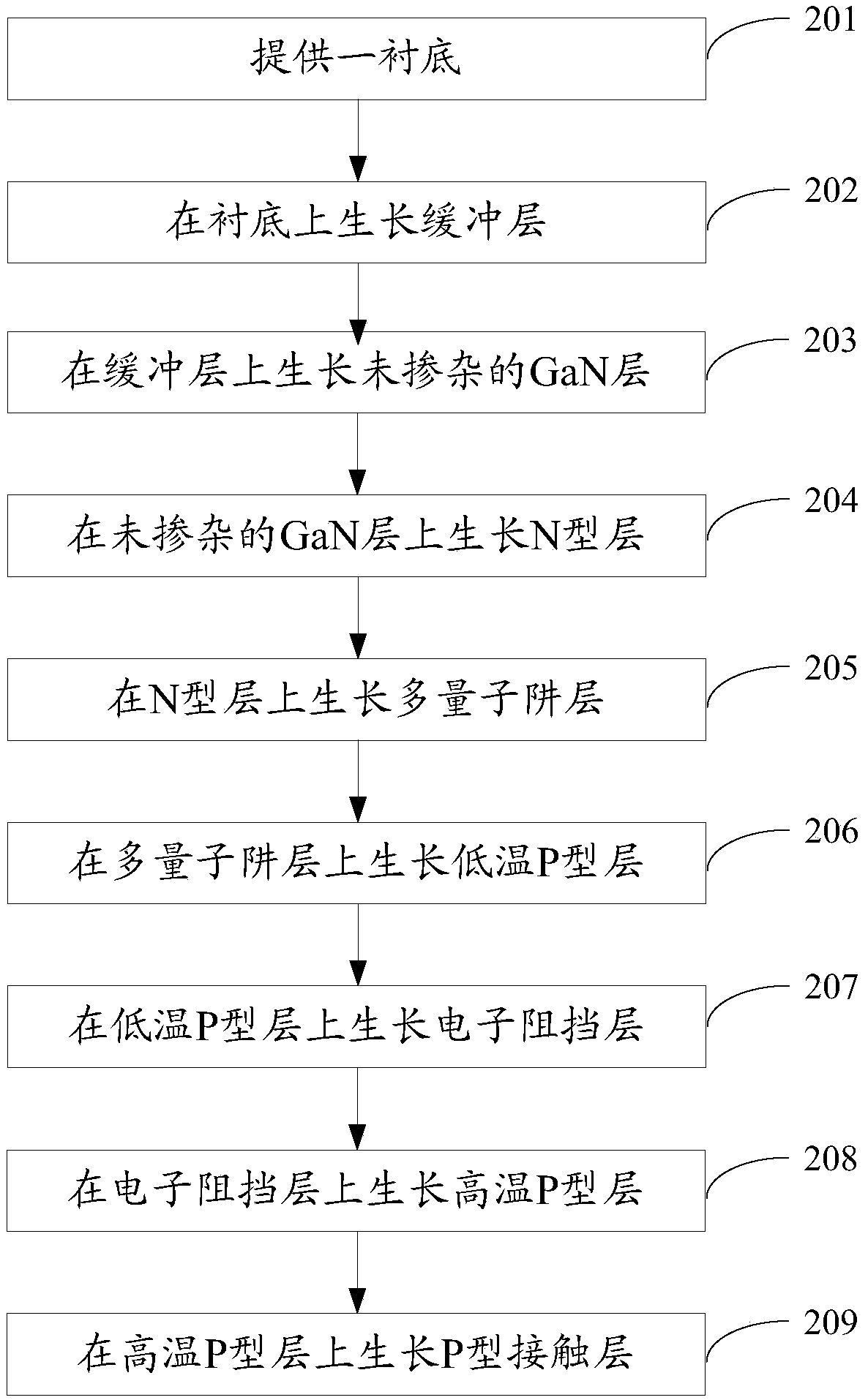

Gallium nitride light emitting diode and preparation method thereof

ActiveCN103531683APlay a role of buffer protectionProlong the growth time in three-dimensional spaceSemiconductor/solid-state device manufacturingSemiconductor devicesContact layerGallium nitride

The invention discloses a gallium nitride light emitting diode and a preparation method thereof and belongs to the field of light emitting diodes. The method comprises the following steps: providing a foreign substrate, and depositing a first buffering layer on the foreign substrate by taking a first temperature as a growing temperature; depositing a second buffering layer on the first buffering layer and enabling the second buffering layer to grow at a second temperature from the time of beginning to grow to a first pre-set time, wherein the first temperature is lower than the second temperature and the differential value range of the first temperature and the second temperature is 410-460 DEG C; depositing a third buffering layer on the second buffering layer by taking a third temperature as the growing temperature, wherein the second temperature is lower than the third temperature; and sequentially depositing an N type contact layer, a light-emitting layer, an electronic barrier layer and a P type contact layer on the third buffering layer to finish the preparation of the gallium nitride light emitting diode. The light emitting diode is prepared by adopting the method. The growing starting temperature of the second buffering layer is between the growing temperature of the first buffering layer and the growing temperature of the third buffering layer and the second buffering layer has the buffering and protection effects on the third buffering layer.

Owner:HC SEMITEK CORP

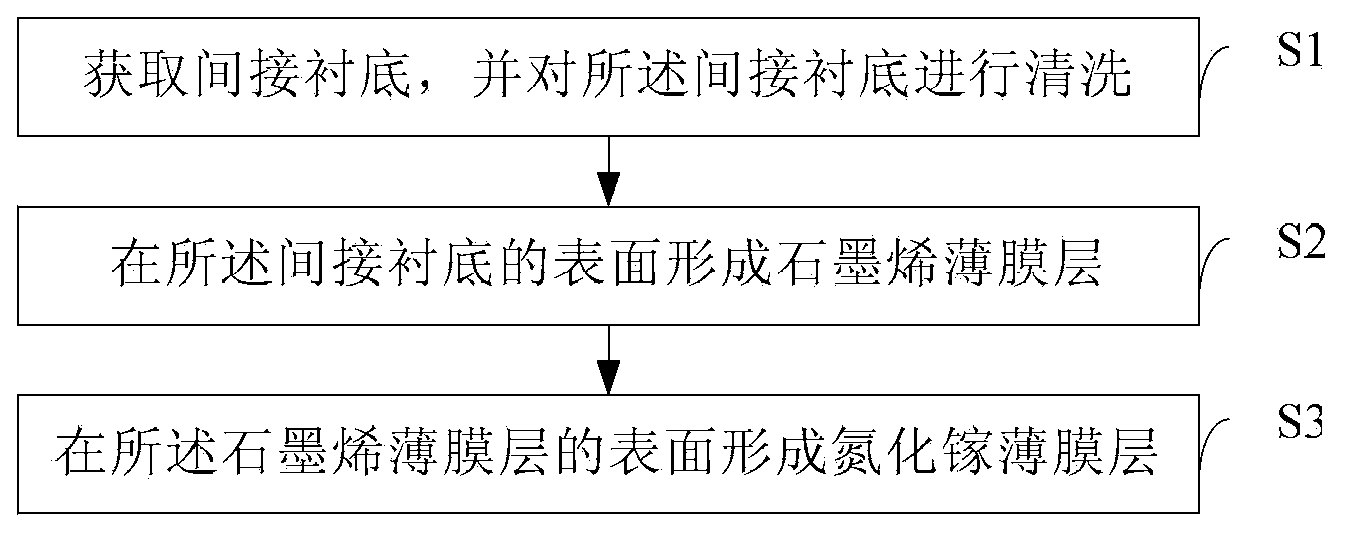

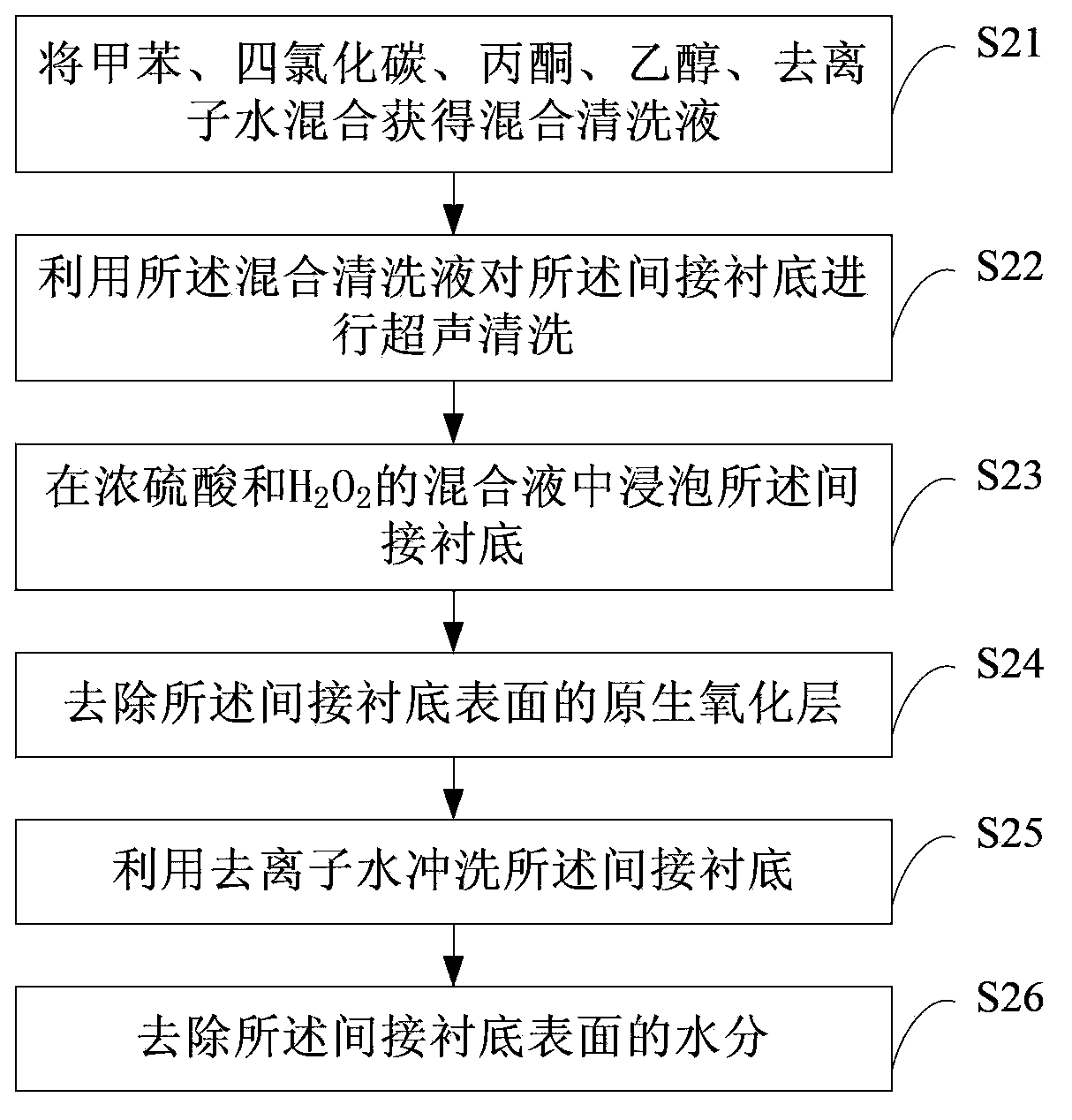

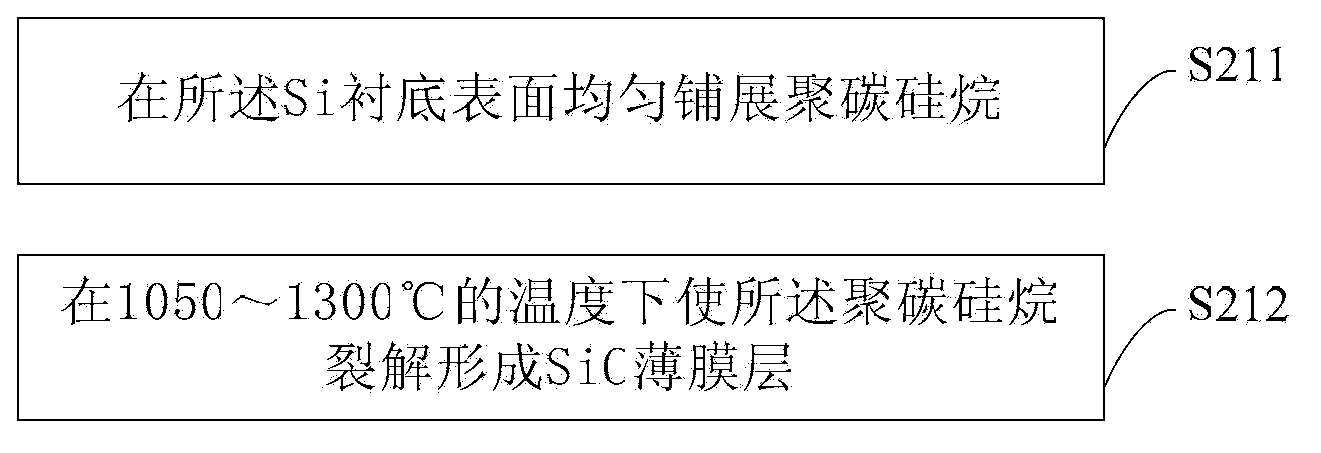

Preparation method of gallium nitride film layer and substrate

InactiveCN103794469AReduce dislocation densityImprove performanceSemiconductor/solid-state device manufacturingGallium nitrideCvd graphene

The invention provides a preparation method of a gallium nitride film layer and a substrate. The preparation method of the gallium nitride film layer comprises the following steps: obtaining and cleaning an indirect substrate; forming a graphene film on the surface of the indirect substrate; and forming a gallium nitride film layer on the surface of the graphene film. The preparation method of the gallium nitride film layer can effectively reduce the dislocation density of the gallium nitride film layer in a process of growth, thereby improving performance of the gallium nitride film layer.

Owner:BEIJING NAURA MICROELECTRONICS EQUIP CO LTD

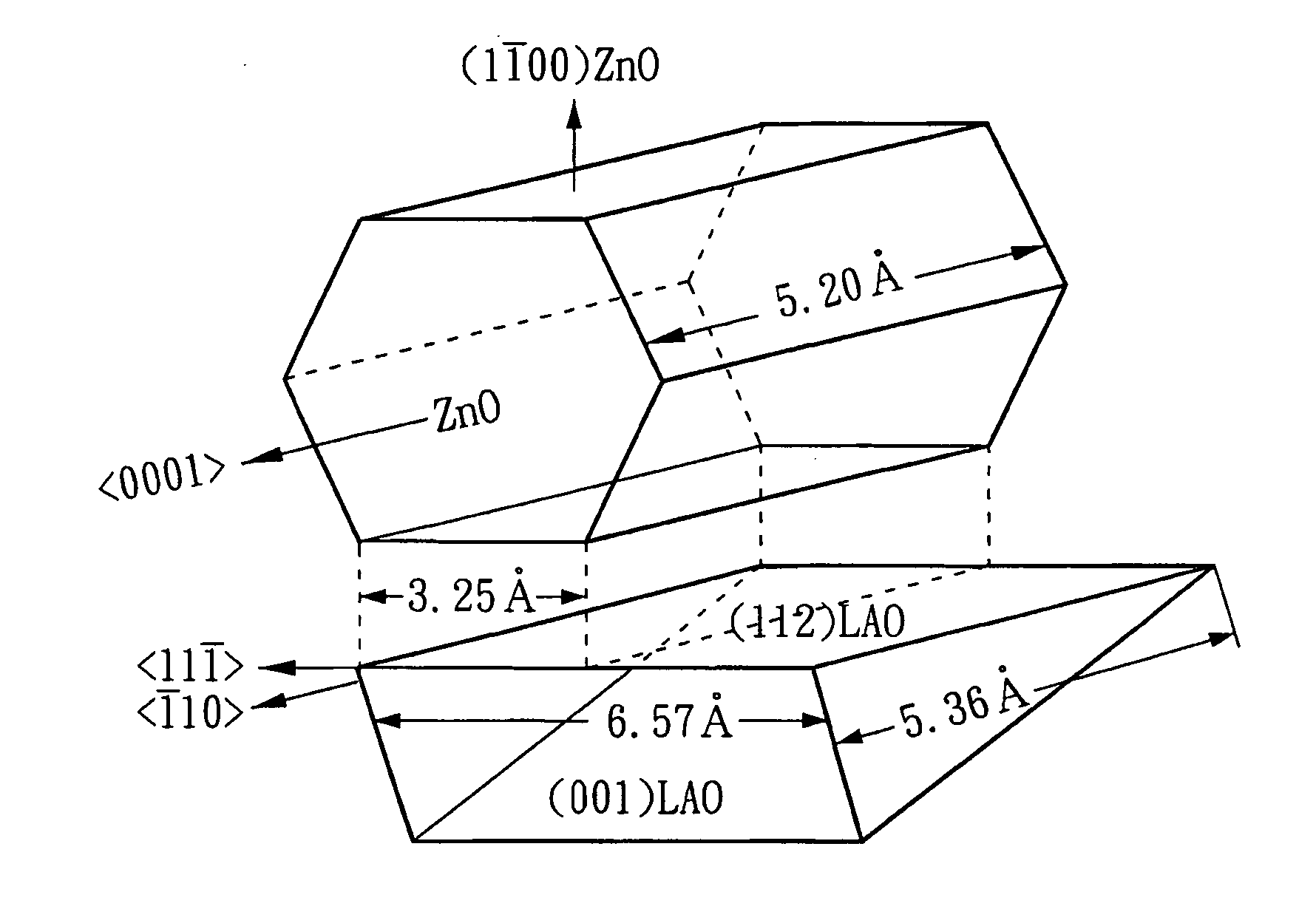

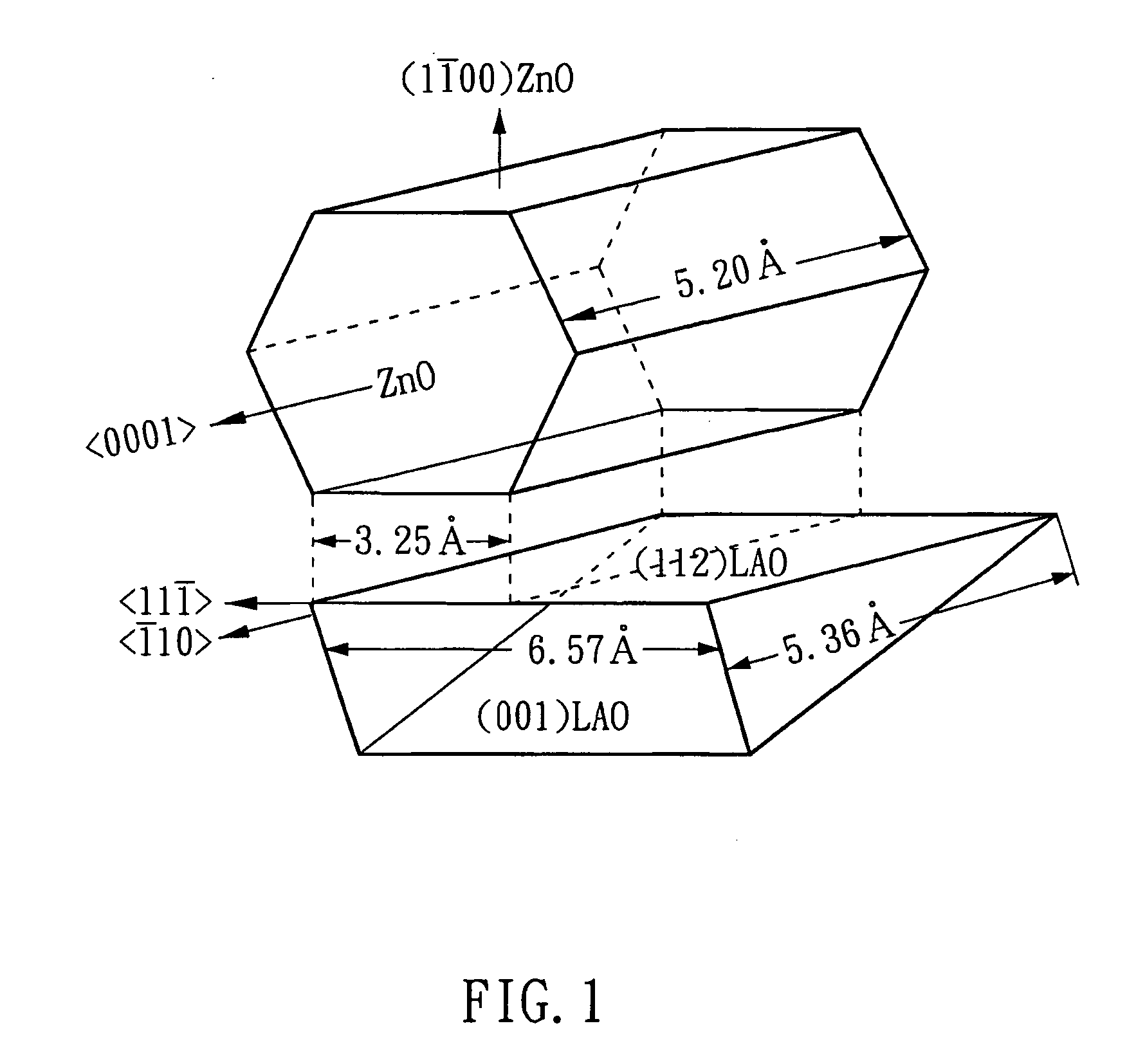

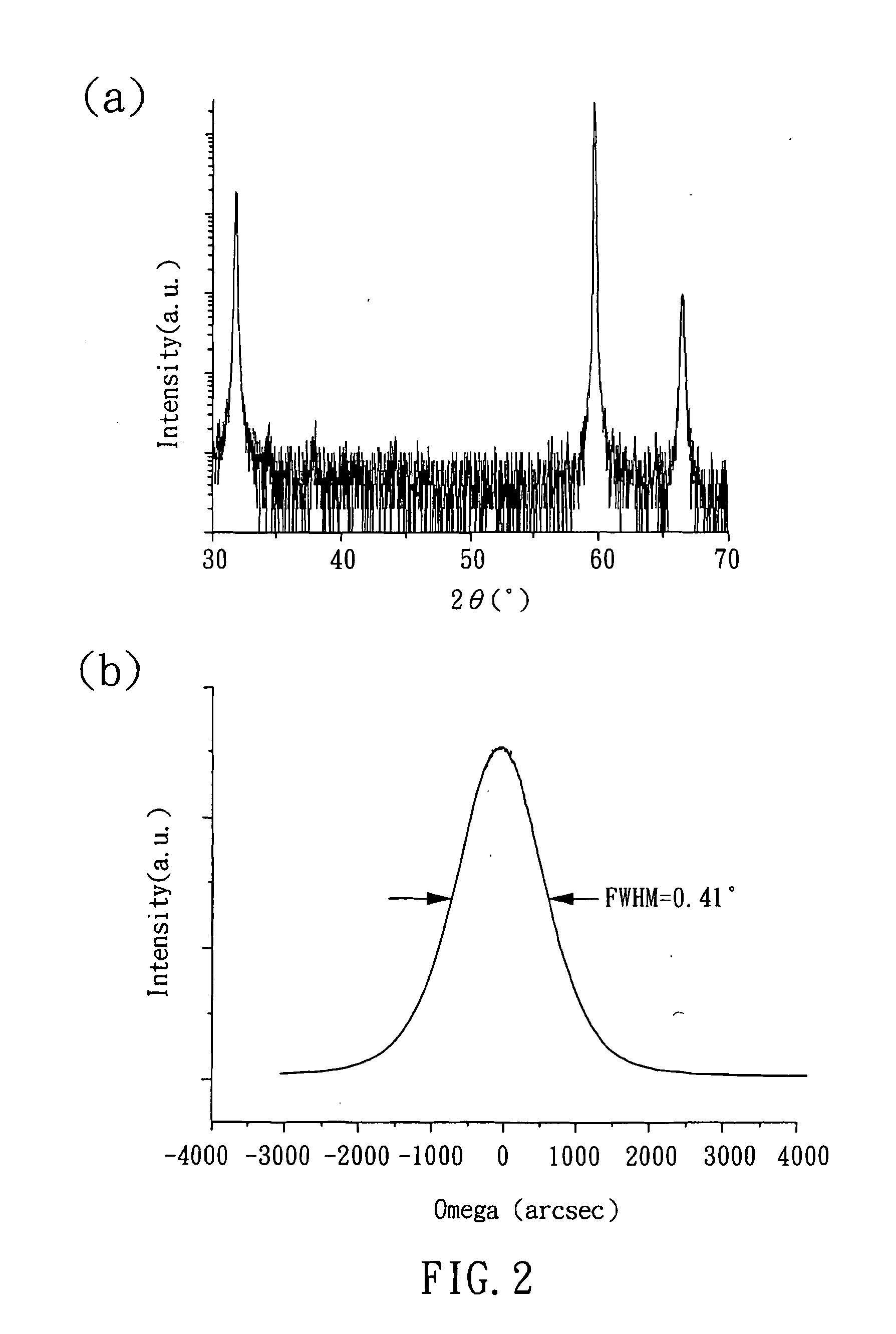

Method for growing non-polar m-plane epitaxial layer of wurtzite semiconductors on single crystal oxide substrates

InactiveUS20110062437A1Improve thermal stabilityLow lattice mismatchPolycrystalline material growthSemiconductor/solid-state device manufacturingGas phaseSingle crystal

The present invention relates to a method for growing a non-polar m-plane epitaxial layer on a single crystal oxide substrate, which comprises the following steps: providing a single crystal oxide with a perovskite structure; using a plane of the single crystal oxide as a substrate; and forming an m-plane epitaxial layer of wurtzite semiconductors on the plane of the single crystal oxide by a vapor deposition process. The present invention also provides an epitaxial layer having an m-plane obtained according to the aforementioned method.

Owner:NAT CHIAO TUNG UNIV

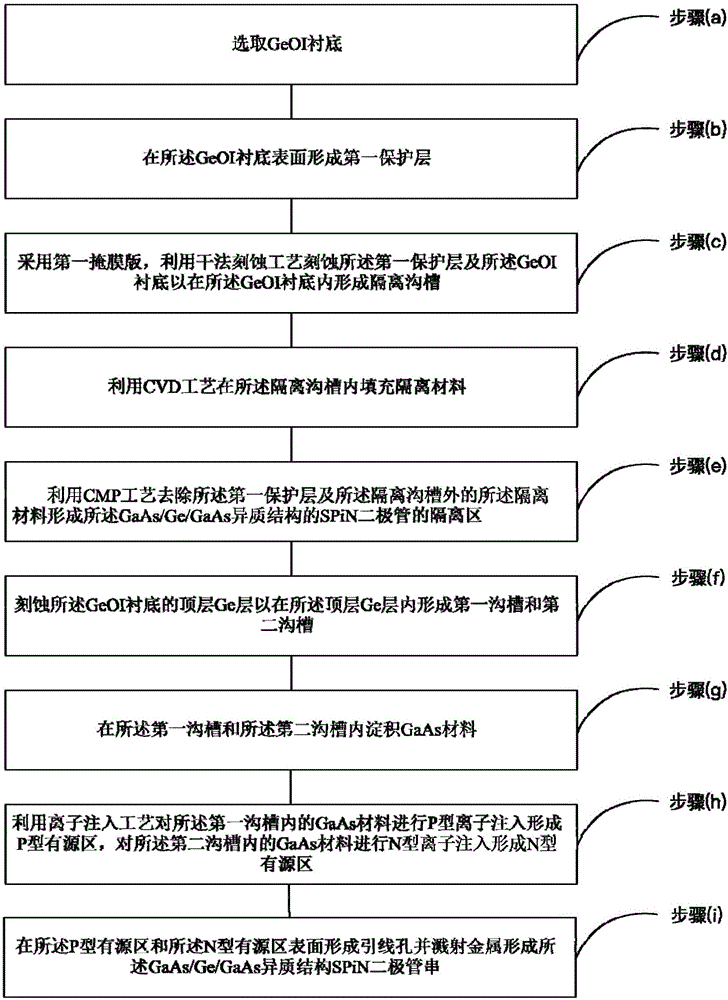

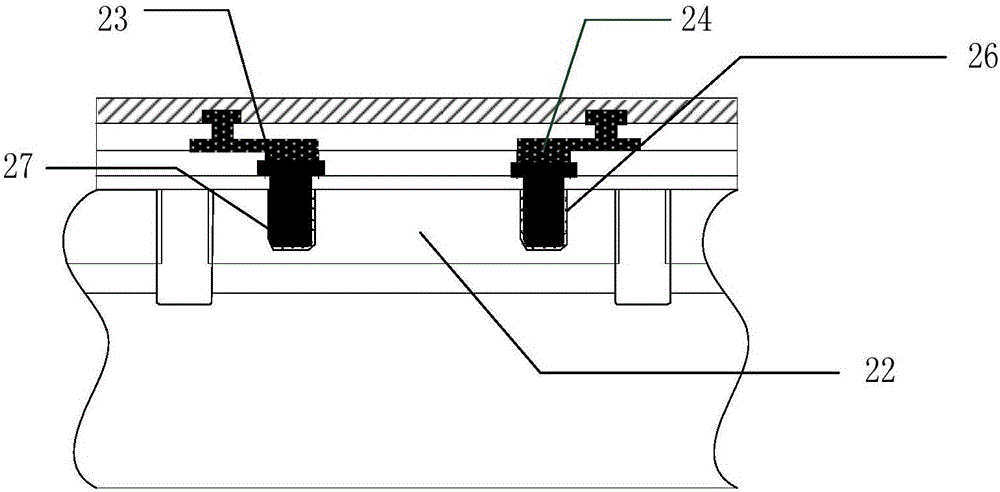

Preparation method for GaAs/Ge/GaAs heterostructure SPiN diode string used for sleeve antenna

InactiveCN106847904AImprove injection efficiencyIncrease currentRadiating elements structural formsSemiconductor/solid-state device manufacturingSputteringPlasma antenna

The invention relates to a preparation method for a GaAs / Ge / GaAs heterostructure SPiN diode string used for a sleeve antenna. The preparation method comprises the steps of (a), selecting a GeOI substrate; (b), etching a top layer Ge layer of the GeOI substrate to form a first trench and a second trench in the top layer Ge layer; (c), depositing a GaAs material in the first trench and the second trench; (d), performing P type ion implantation on the GaAs material in the first trench by adopting an ion implantation process to form a P type active region, and performing N type ion implantation on the GaAs material in the second trench to form an N type active region; and (e), forming lead holes in the surfaces of the P type active region and the N type active region and performing metal sputtering to form the GaAs / Ge / GaAs heterostructure SPiN diode. According to the embodiments, the high-performance Ge-based SPiN diode string, which is applicable to formation of a solid-state plasma antenna, can be prepared and provided through a deep trench isolation technology and the ion implantation process.

Owner:XIAN CREATION KEJI CO LTD

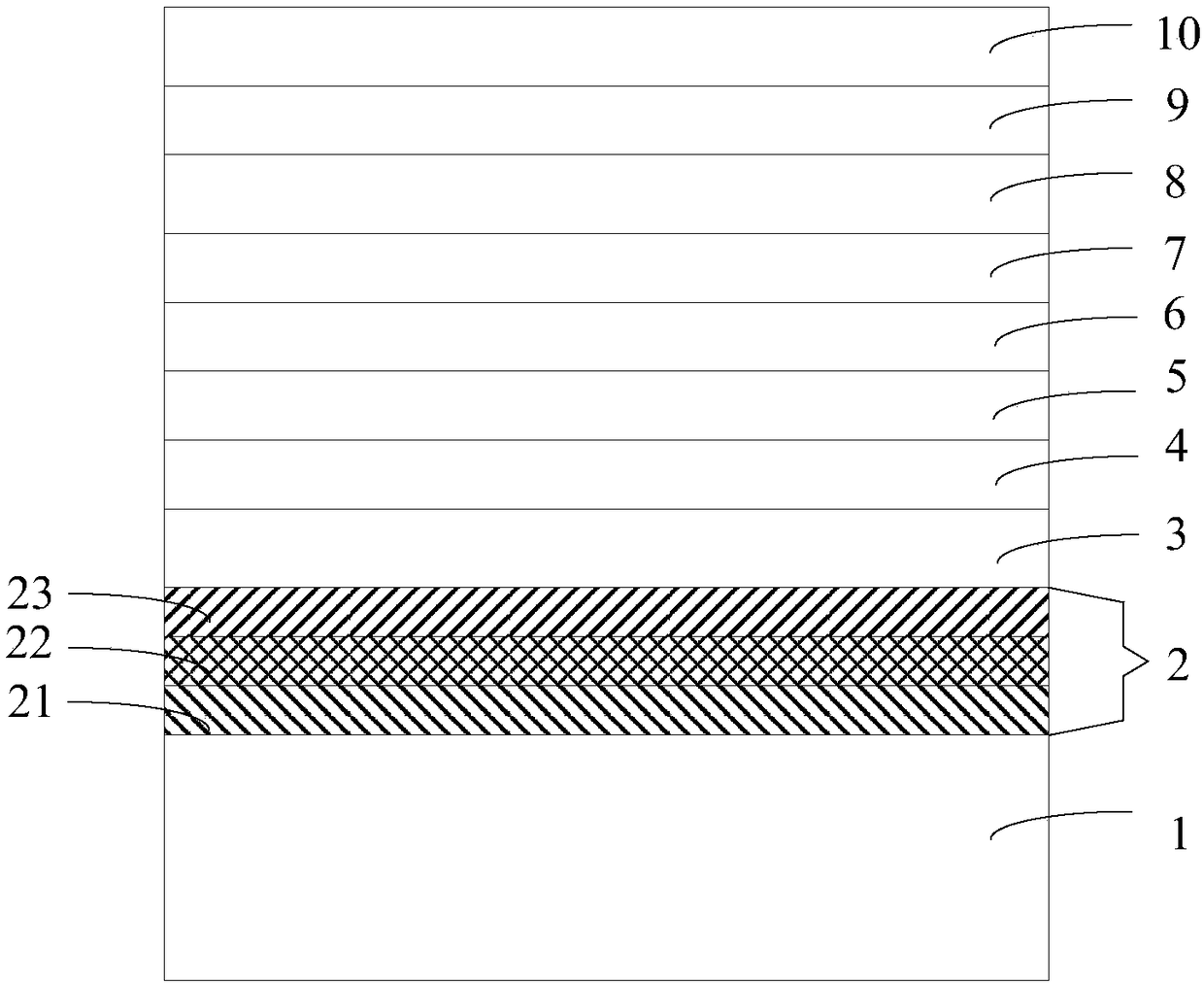

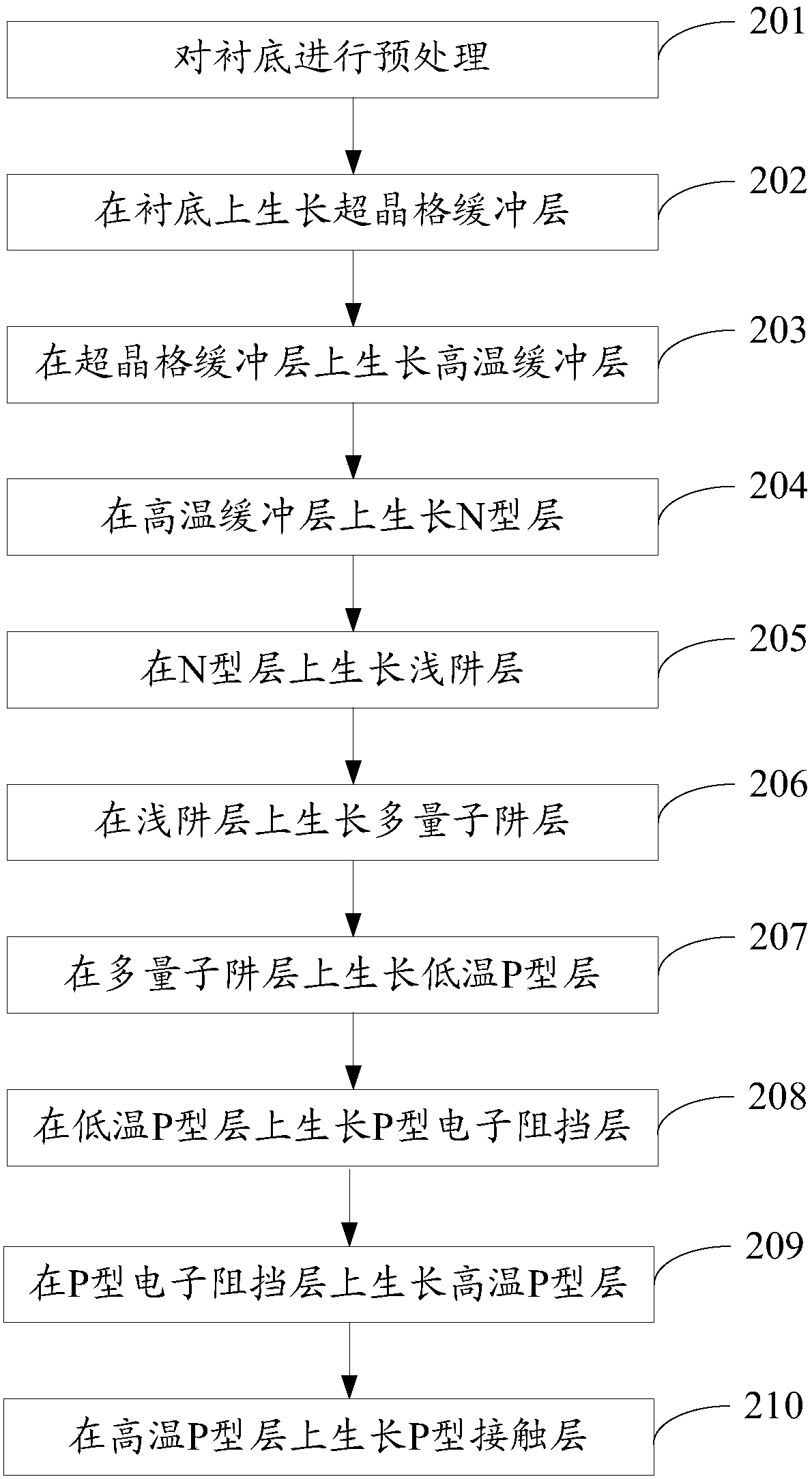

Gallium-nitride-based light emitting diode epitaxial wafer and manufacturing method thereof

ActiveCN108110098AIncrease the lattice constantReduced stress polarization effectsSemiconductor devicesQuantum wellLattice mismatch

The invention discloses a gallium-nitride-based light emitting diode epitaxial wafer and a manufacturing method thereof, belonging to the technical field of semiconductors. The gallium-nitride-based light emitting diode epitaxial wafer comprises a superlattice buffer layer, wherein the superlattice buffer layer is of a superlattice structure comprising N periods, and the superlattice structure ofeach period comprises a first sublayer, a second sublayer and a third sublayer which are laminated on a substrate. Through doping Al into the first sub-layer, the lattice mismatch between the substrate and a GaN layer can be alleviated, the defect density can be reduced, and the crystal quality of the entire epitaxial layer can be improved, thereby improving the anti-static capability of an LED. Through doping Mg into the second sublayer, a transition between the first sublayer and the second sublayer can be achieved. Through doping In into the third sublayer, the lattice constant of the thirdsublayer can be increased, thereby accelerating a stress release speed of an N-type layer, reducing the stress polarization effect of a multi-quantum well layer, and increasing the luminous efficiency of the LED.

Owner:HC SEMITEK ZHEJIANG CO LTD

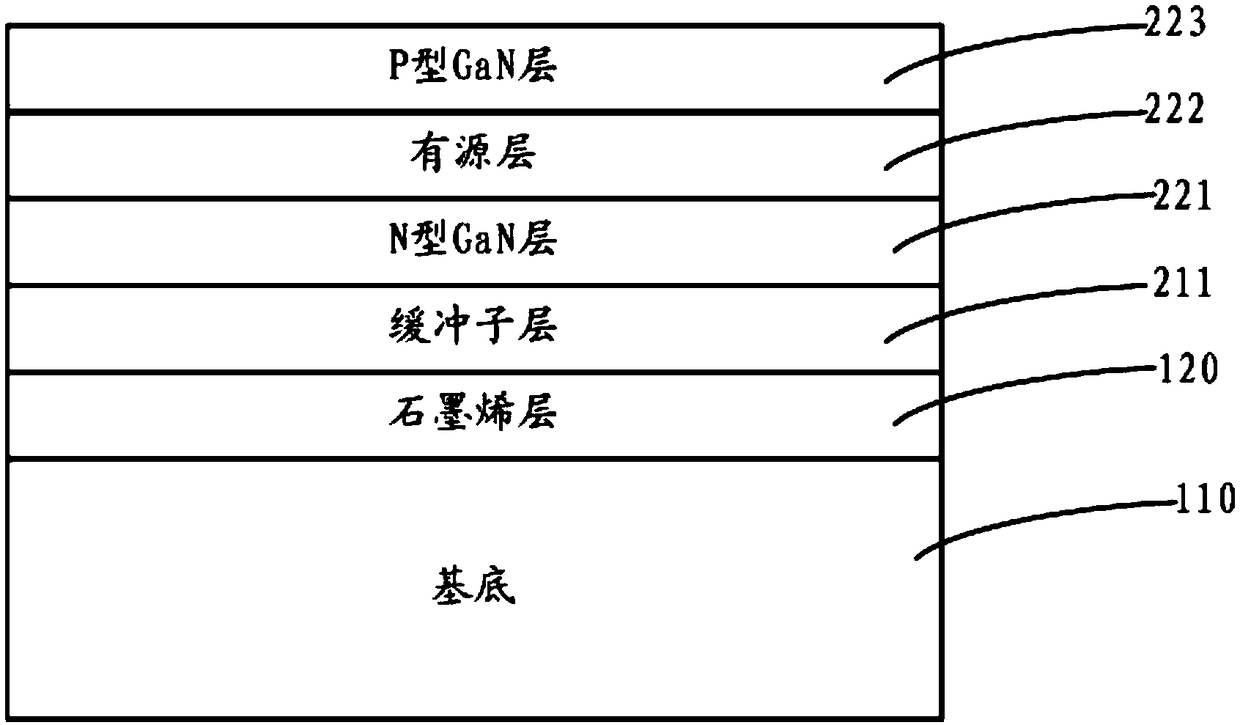

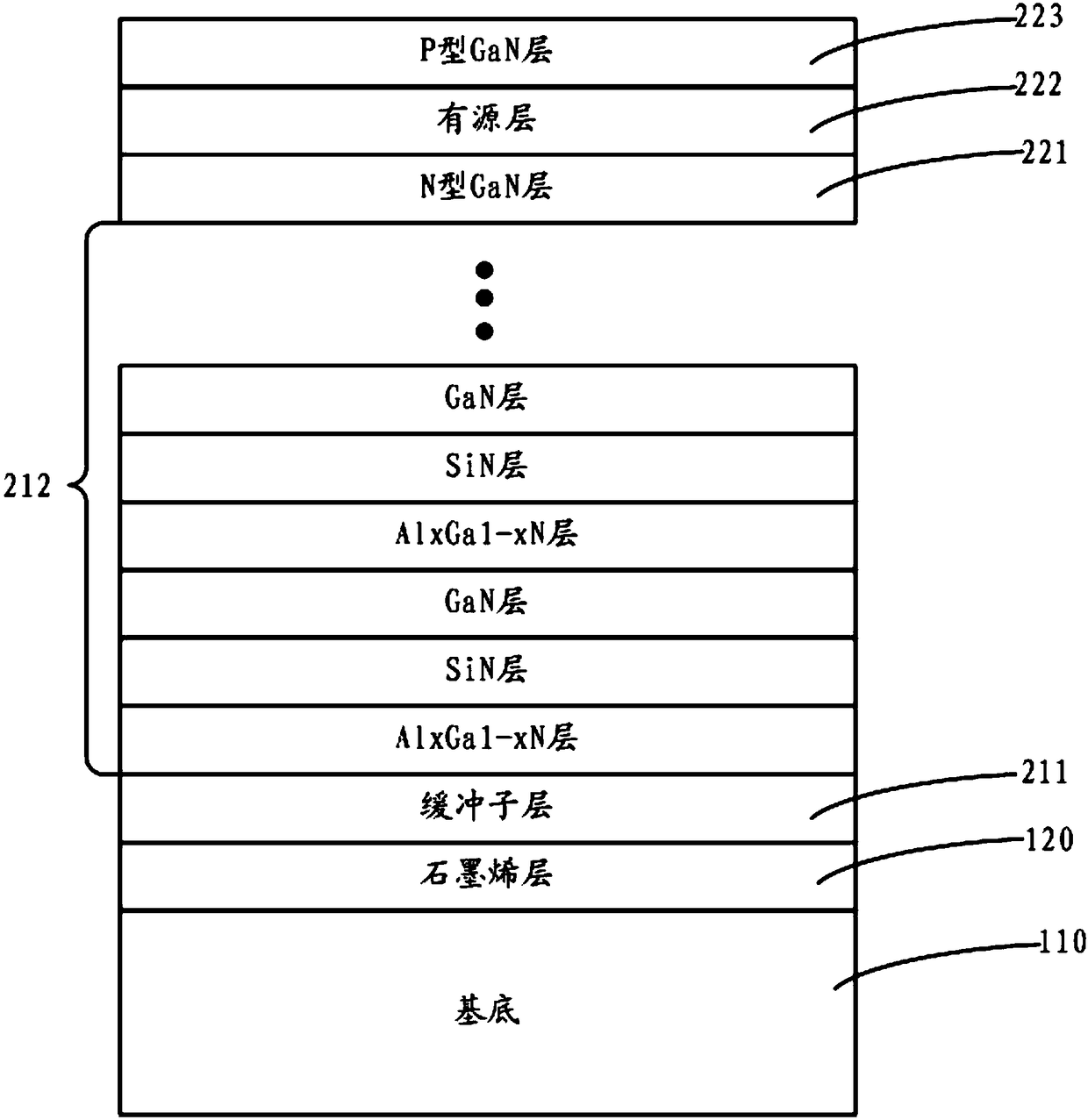

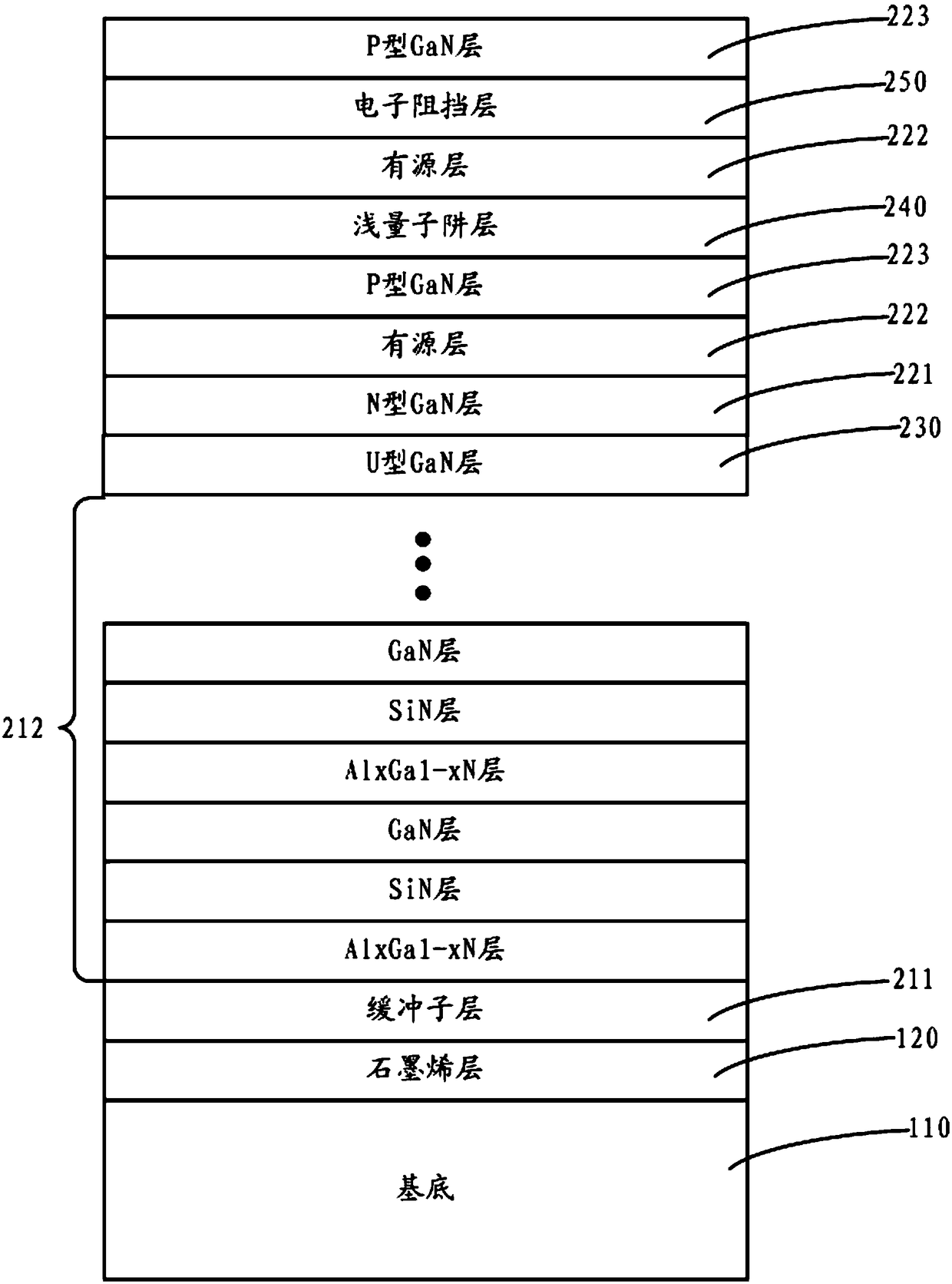

LED epitaxial structure based on graphene substrate, growing method and LED

ActiveCN108767079AImprove crystal qualityReduce lattice mismatchSemiconductor devicesLattice mismatchOptoelectronics

The invention discloses an LED epitaxial structure based on a graphene substrate, a growing method and an LED. The graphene substrate comprises a substrate and a graphene layer positioned on the surface of one side of the substrate. The LED epitaxial structure comprises a buffer layer grown on the graphene substrate and an N-type GaN layer, an active layer and a P-type GaN layer which are grown onthe buffer layer in an overlapped manner in sequence, wherein the buffer layer comprises buffer sub-layers grown on the surface of the side, away from the substrate, of the graphene layer; the buffersub-layers are AlN buffer sub-layers, GaN buffer sub-layers, InGaN buffer sub-layers or AlGaInN buffer sub-layers. Through the technical scheme provided by the invention, the buffer layer of the LEDepitaxial structure is grown on the graphene substrate, the lattice mismatch between the LED epitaxial structure and the graphene substrate is reduced, the stress between the graphene substrate and the LED epitaxial structure is reduced, and then the LED epitaxial structure with high crystalline quality can be prepared, so that a polarization electric field is reduced effectively, the bending of an energy band is reduced, and the composite efficiency of electrons and holes is improved.

Owner:YANGZHOU CHANGELIGHT

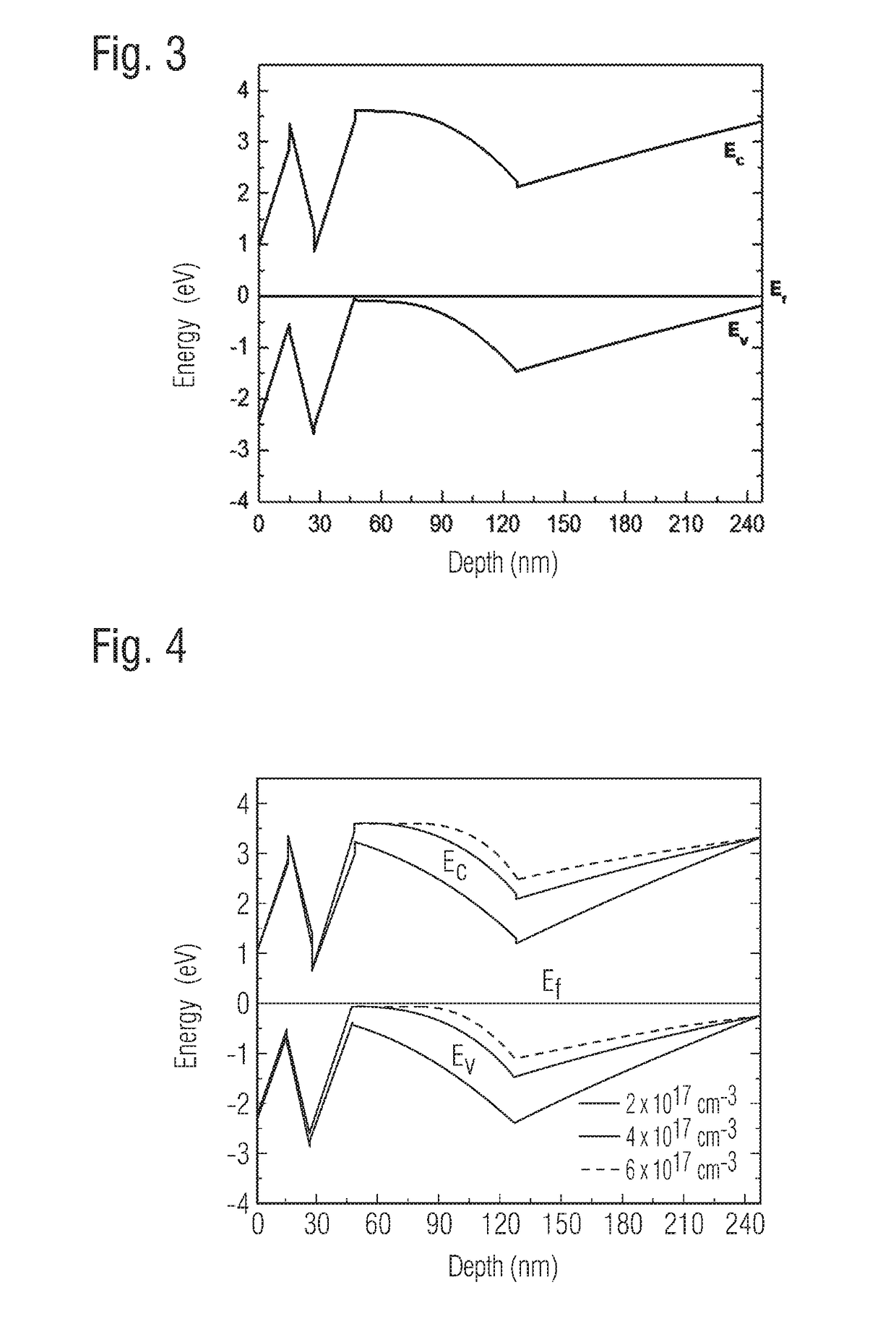

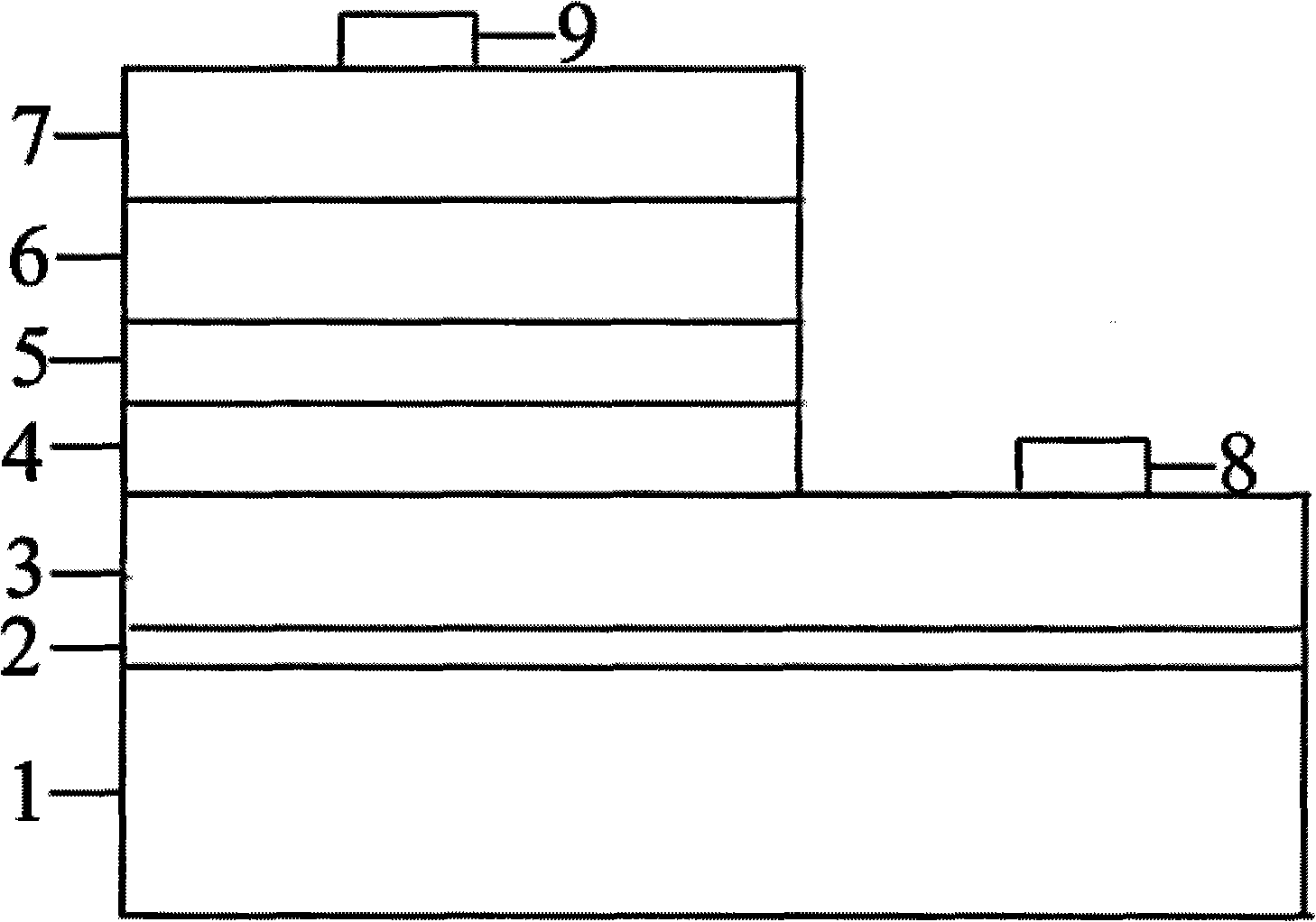

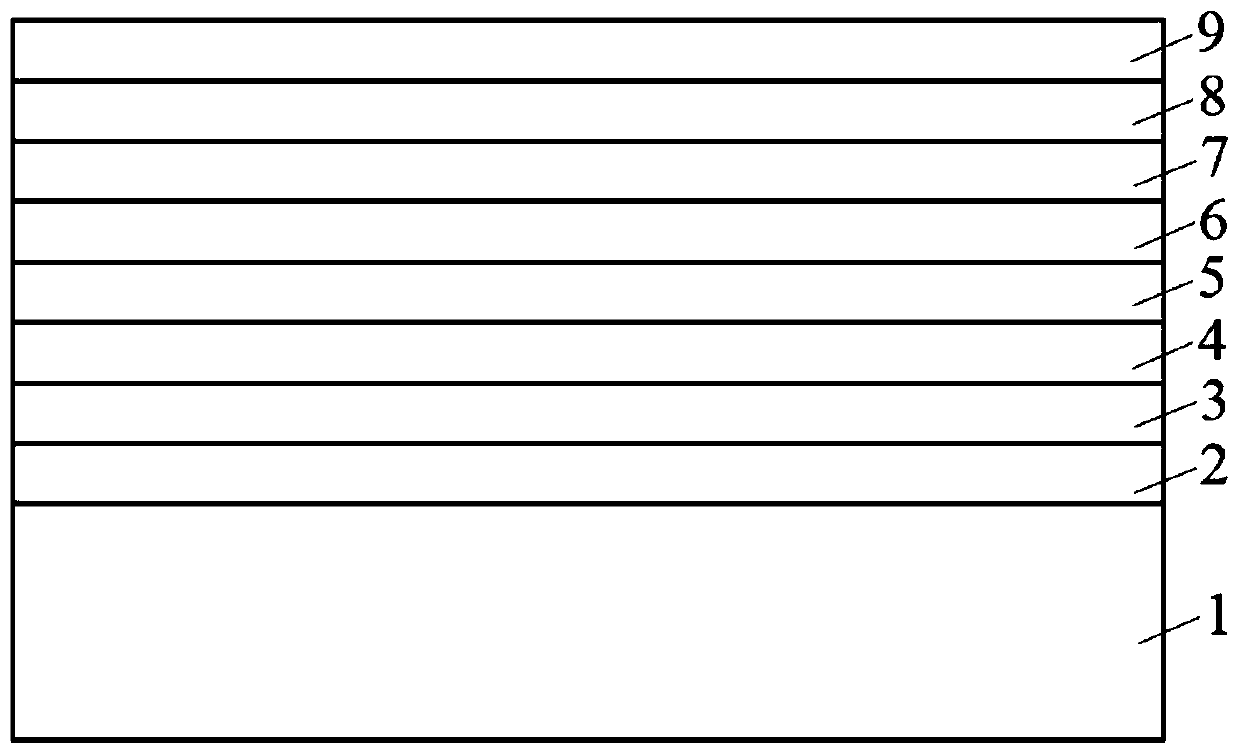

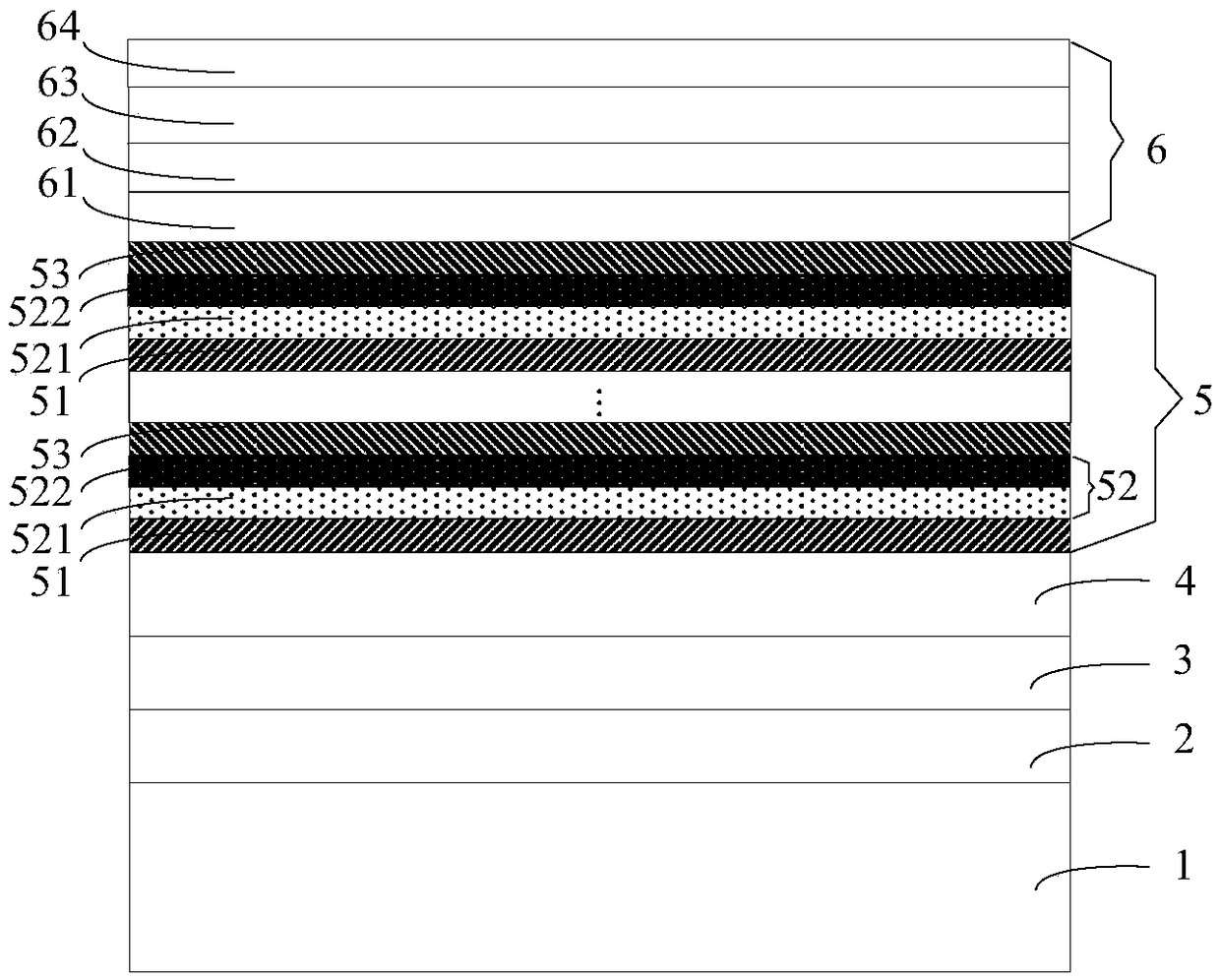

Laser diode based on gallium nitride single-crystal substrate and preparation method of laser diode

ActiveCN110729631AImproved current spreadPlay the effect of saving electronsOptical wave guidanceLaser detailsQuantum efficiencyQuantum well

The invention discloses a laser diode based on a gallium nitride single crystal substrate and a preparation method of the laser diode. The laser diode comprises the GaN single-crystal substrate, an n-type GaN layer, an n-type limiting layer, a lower waveguide layer, a composite quantum well active region, an electron blocking layer, an upper waveguide layer, a p-type limiting layer and a p-type GaN layer which are sequentially stacked from bottom to top. According to the invention, the high-quantum efficiency stress regulation and control active region structure, the novel optical waveguide layer structure and the novel limiting layer structure of the gallium nitride-based laser diode are designed and optimized; the laser diode is prepared on the low-dislocation-density GaN single-crystalsubstrate; the technical difficulty of epitaxial preparation of a GaN-based laser is eliminated; and a GaN-based laser with high reliability and high quantum efficiency can be obtained.

Owner:DONGGUAN UNIV OF TECH

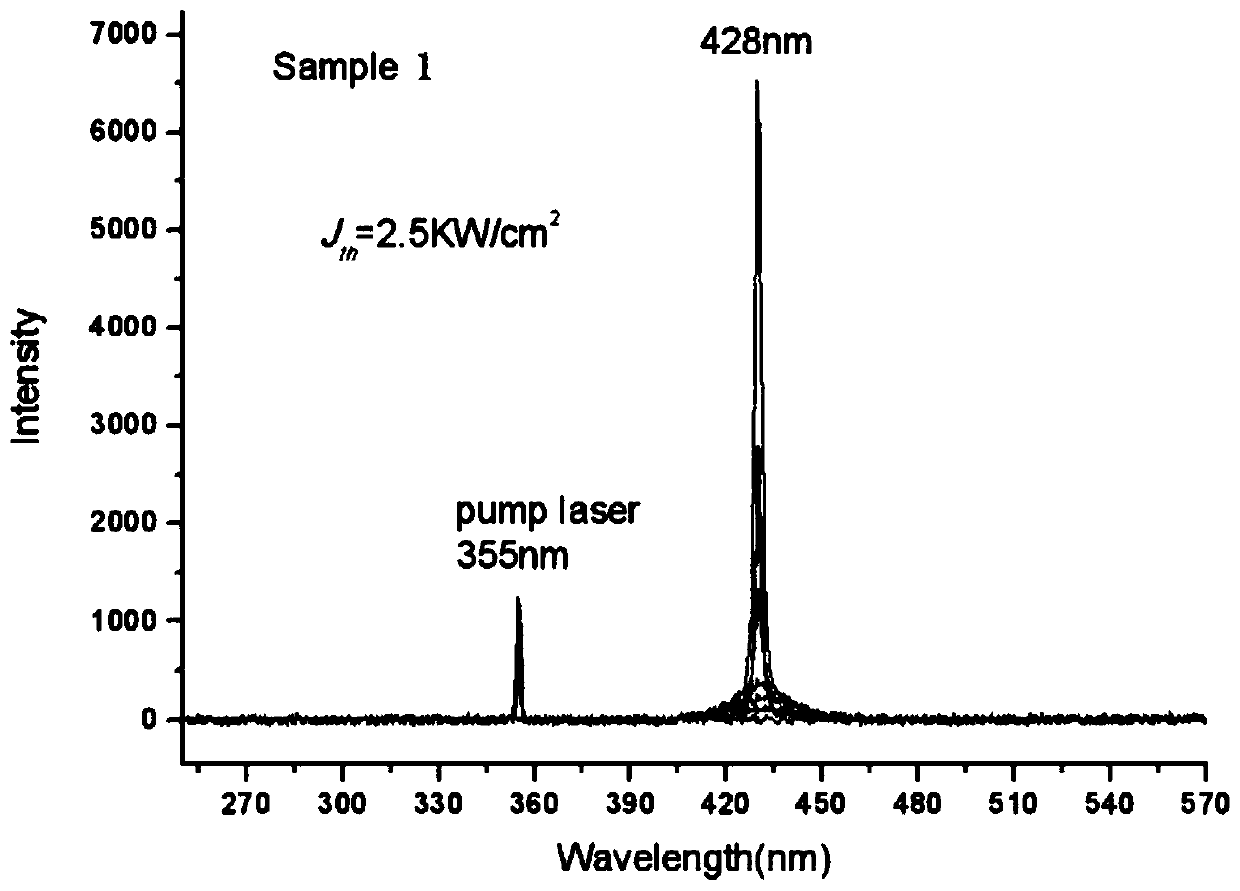

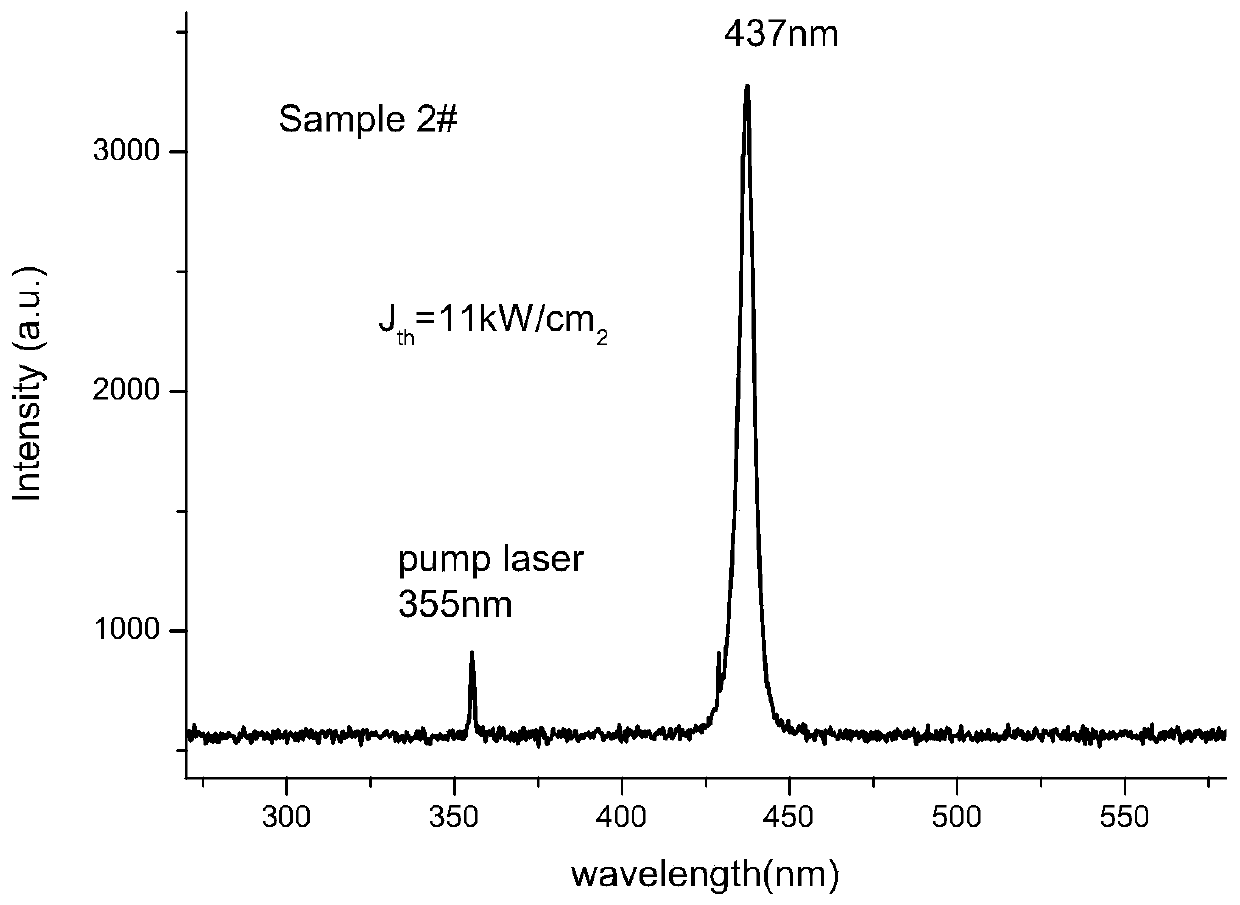

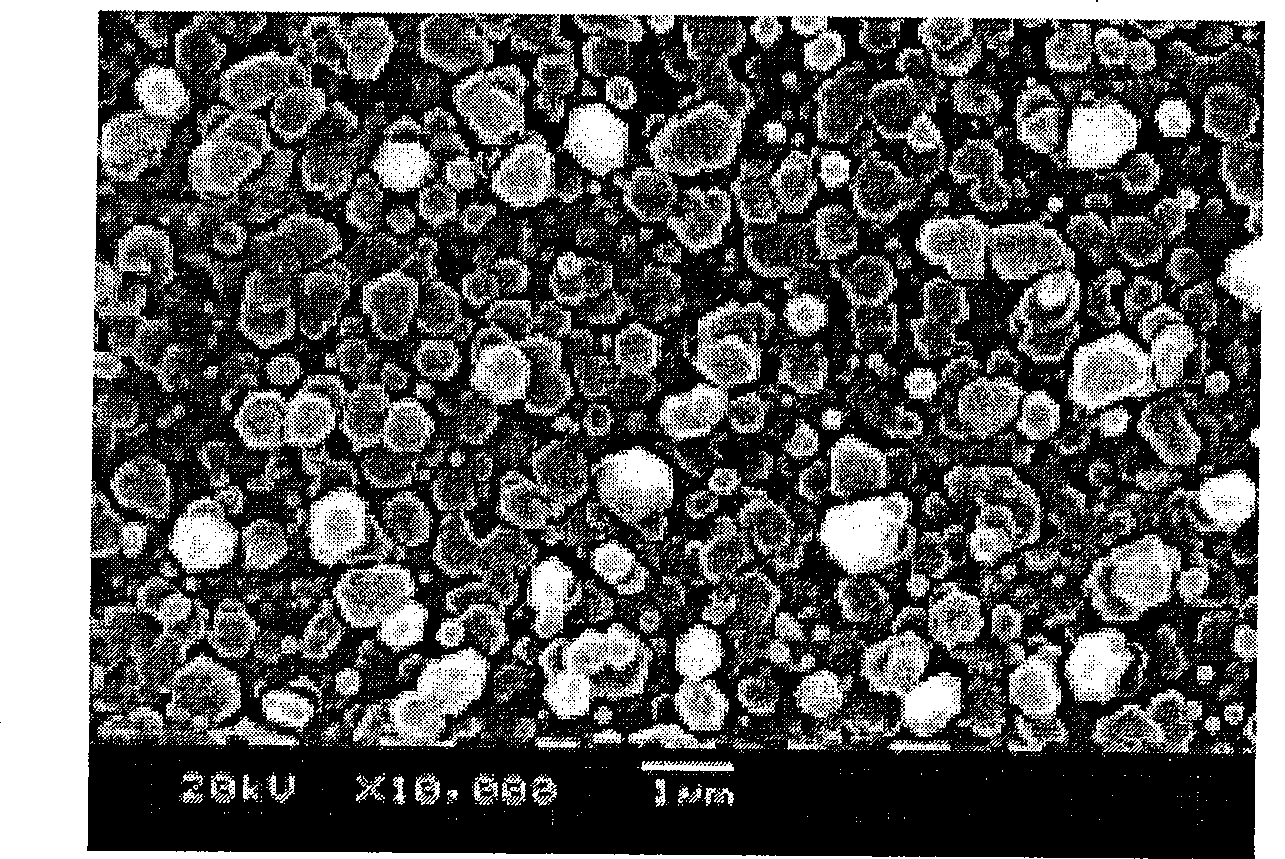

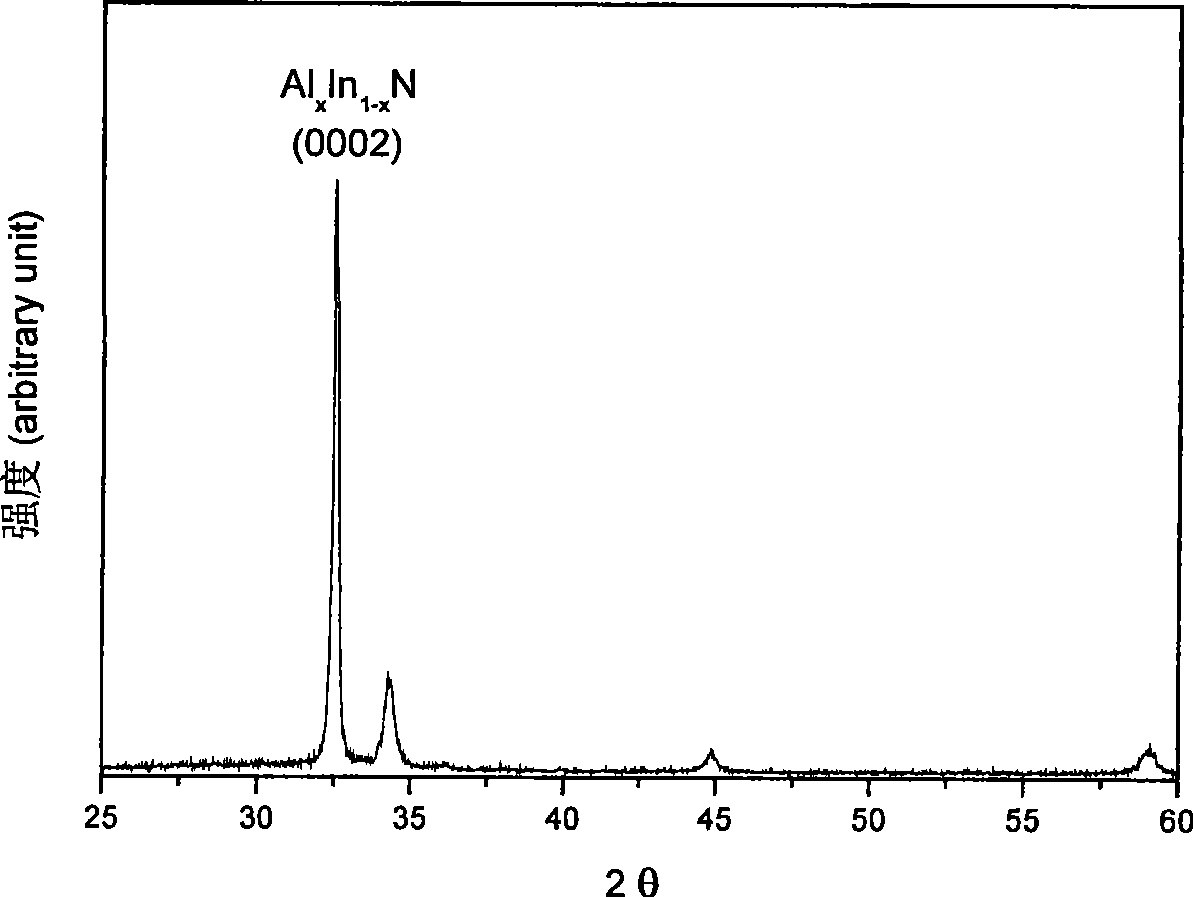

Method for preparing AlxIn1-xN film

InactiveCN101423927AReduce lattice mismatchAdequate responseVacuum evaporation coatingSputtering coatingSputteringNitrogen

The invention discloses a method for preparing AlxIn1-xN thin films. The method comprises the following steps: (1) a substrate is completely cleaned by washing at normal temperature and normal pressure and placed in an atmosphere of nitrogen to be dried; (2) the treated substrate is placed in a sputtering chamber, and a buffer layer AIN is grown on the substrate under a vacuum condition by a sputtering method which uses Al as a target material and carries out sputtering for 20 to 30 minutes under conditions of a flow ratio of N2 to Ar of 1 to 9, a DC sputtering power of between 50 to 60w and the temperature of the substrate during sputtering controlled between 400 to 500 DEG C; and (3) after growth of the buffer layer AIN, the target material is changed into Al-In(1:1) alloy and an AlxIn1-xN thin film is grown under a vacuum condition by a sputtering method which carries out sputtering for 10 to 30 minutes under conditions of a flow ratio of N2 to Ar of 3 to 1, a DC sputtering power of between 80 to 160w and the temperature of the substrate during sputtering controlled between 250 to 350 DEG C.

Owner:SICHUAN NORMAL UNIVERSITY

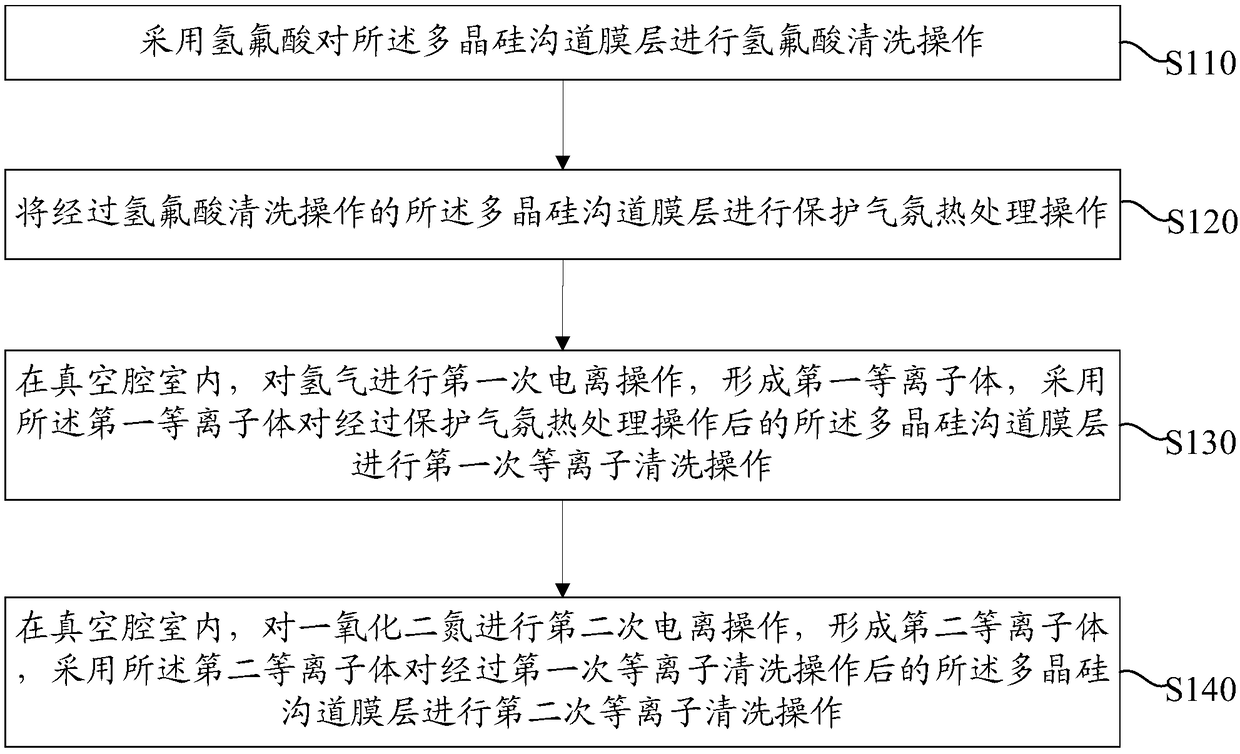

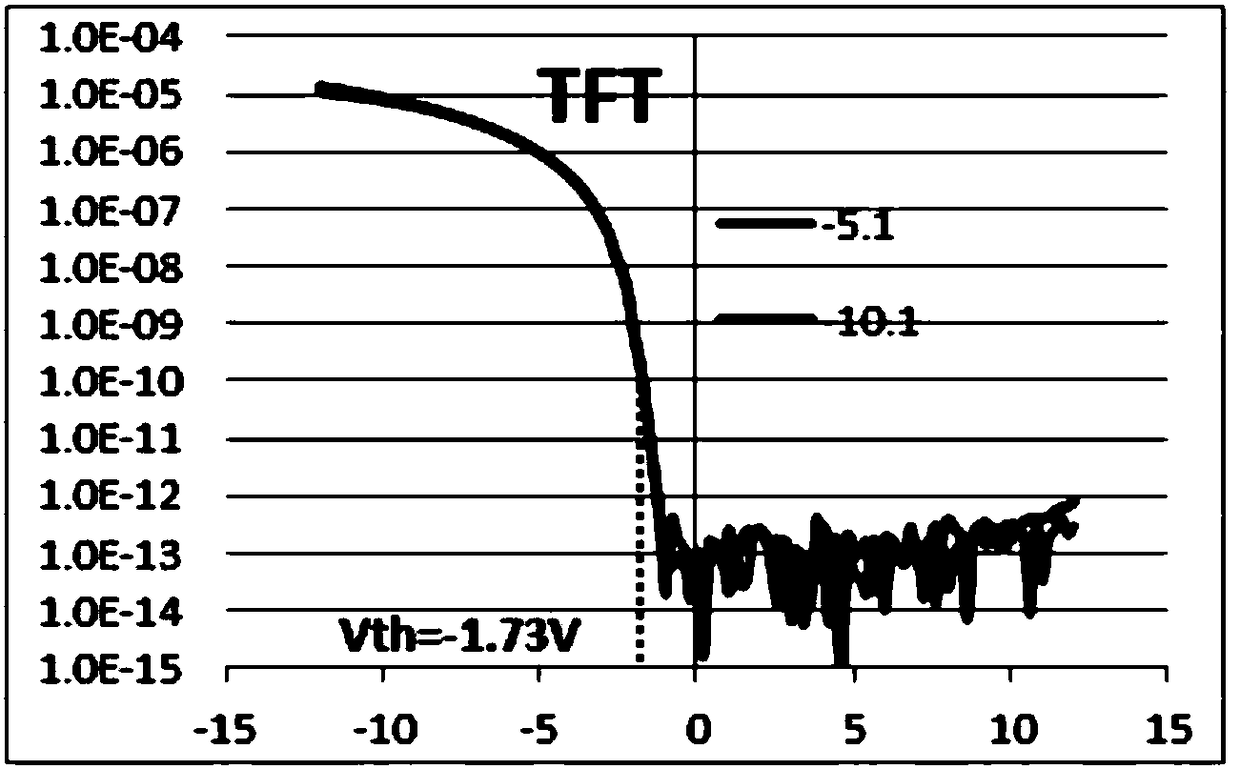

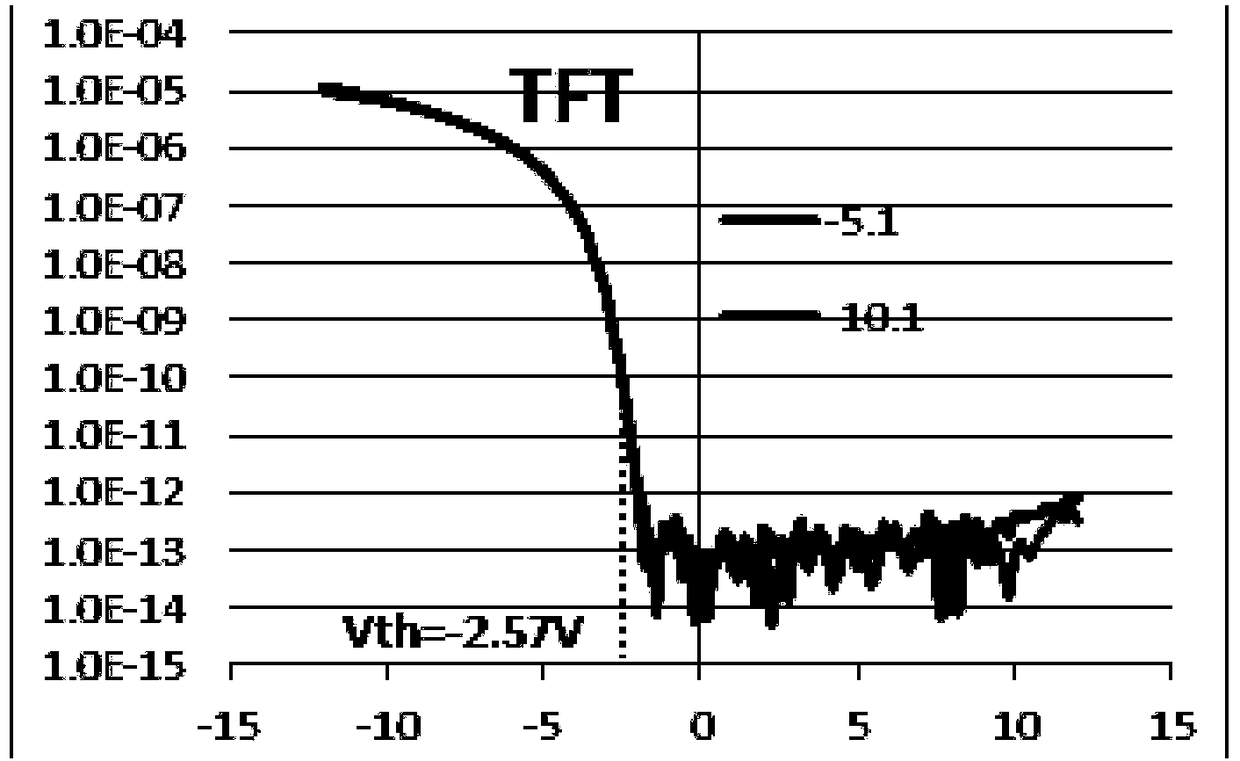

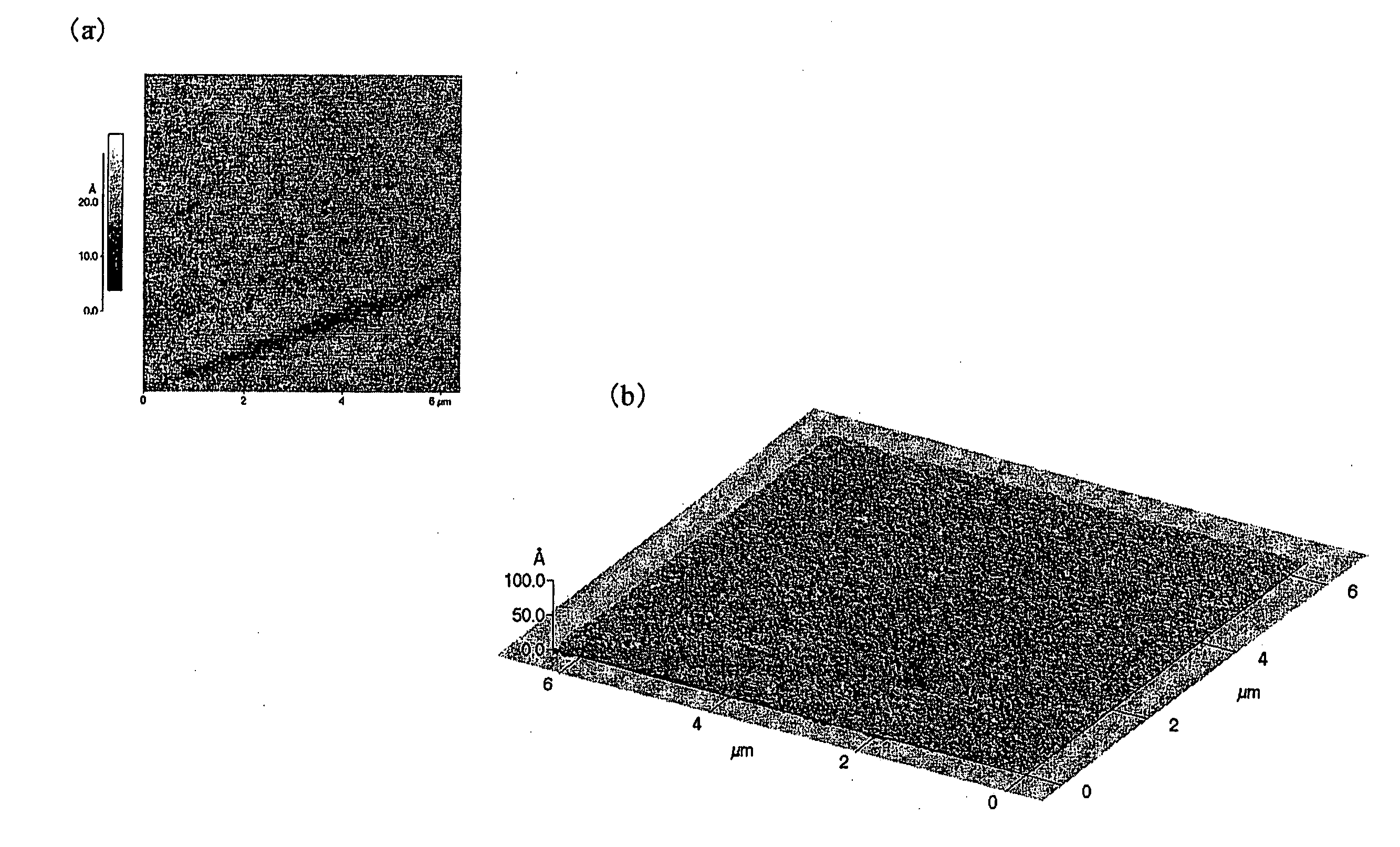

Processing method for improving threshold voltage of thin film transistor (TFT) device

ActiveCN108335969ARaise the threshold voltageImprove the state of the interfaceSemiconductor/solid-state device manufacturingSemiconductor devicesInsulation layerEngineering

A processing method for improving a threshold voltage of a thin film transistor (TFT) device is applied before a gate insulation layer formed on a poly-silicon channel film layer and comprises the following steps of performing hydrofluoric acid cleaning operation on the poly-silicon channel film layer with hydrofluoric acid; performing protection atmosphere thermal processing operation on the poly-silicon channel film layer subjected to hydrofluoric acid cleaning operation; performing first-time ionization operation on hydrogen in a vacuum chamber to form first plasma, and performing first-time plasma cleaning operation with the first plasma; and performing second-time ionization operation on nitrogen monoxide in the vacuum chamber to form second plasma, and performing second-time plasma cleaning operation with the second plasma. By the processing method for improving the threshold voltage of the TFT device, an interface state between the poly-silicon channel film layer and the gate insulation layer can be improved, the threshold voltage of the TFT device can be reduced, so that the threshold voltage of the TFT device can be improved.

Owner:TRULY HUIZHOU SMART DISPLAY

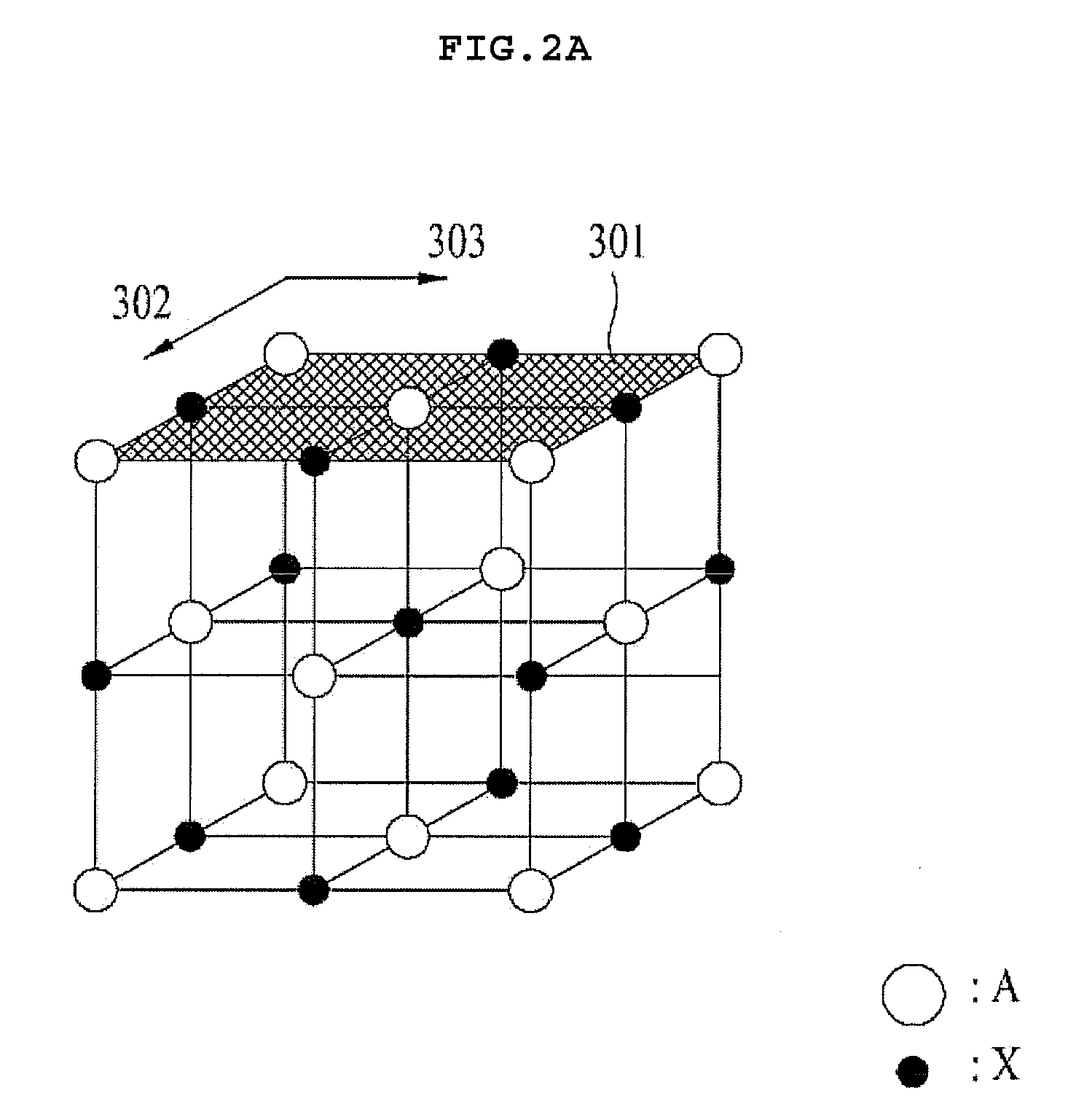

Gallium oxide single crystal composite, process for producing the same, and process for producing nitride semiconductor film utilizing gallium oxide single crystal composite

InactiveUS20090072239A1Quality improvementReduce mixMaterial nanotechnologyPolycrystalline material growthSingle crystalGallium nitride

Provided are: a gallium oxide single crystal composite, which can provide, for example, upon a crystal growth of a nitride semiconductor, a high-quality cubic crystal in which mixing of a hexagonal crystal is reduced to thereby realize dominant growth of a cubic crystal over hexagonal crystal, and which can be utilized as a substrate particularly suitable for epitaxial growth of cubic GaN; a process for producing the same; and a process for producing a nitride semiconductor film. The gallium oxide single crystal composite has a gallium nitride layer formed of cubic gallium nitride on a surface of the gallium oxide single crystal; the process for producing the gallium oxide single crystal composite includes subjecting the surface of gallium oxide single crystal to nitriding treatment using ECR plasma or RF plasma to form the gallium nitride layer formed of cubic gallium nitride on the surface of the gallium oxide single crystal; and further, the process for producing the nitride semiconductor film includes growing the nitride semiconductor film on the surface of the gallium oxide single crystal composite by an RF-MBE method.

Owner:NIPPON LIGHT METAL CO LTD +1

Quantum dot and preparation method thereof

InactiveCN109929552AEffective passivationReduce lattice mismatchMaterial nanotechnologySolid-state devicesLattice mismatchQuantum dot

The invention discloses a quantum dot and a preparation method thereof, wherein the quantum dot comprises a quantum dot core, a metal layer covering the quantum dot core, and a semiconductor shell layer covering the metal layer, and the metal element in the metal layer is one or a plurality of elements selected from Zn, Hg, Al, Ga and In. According to the present invention, the metal layer can bebonded to the quantum dot core by using the ligand on the surface of the quantum dot core as the linker so as to promote the surface activation of the quantum dot core, such that the further growth reaction of the semiconductor shell layer outside the quantum dot can be easily performed; and through the crystal structure formed by bonding the metal atom in the metal layer and the quantum dot core,the surface of the quantum dot core can be effectively passivated, the surface defect can be reduced, and the lattice mismatch between the core and the shell can be reduced, such that the light emitting efficiency and the size uniformity of the quantum dot material can be enhanced.

Owner:TCL CORPORATION

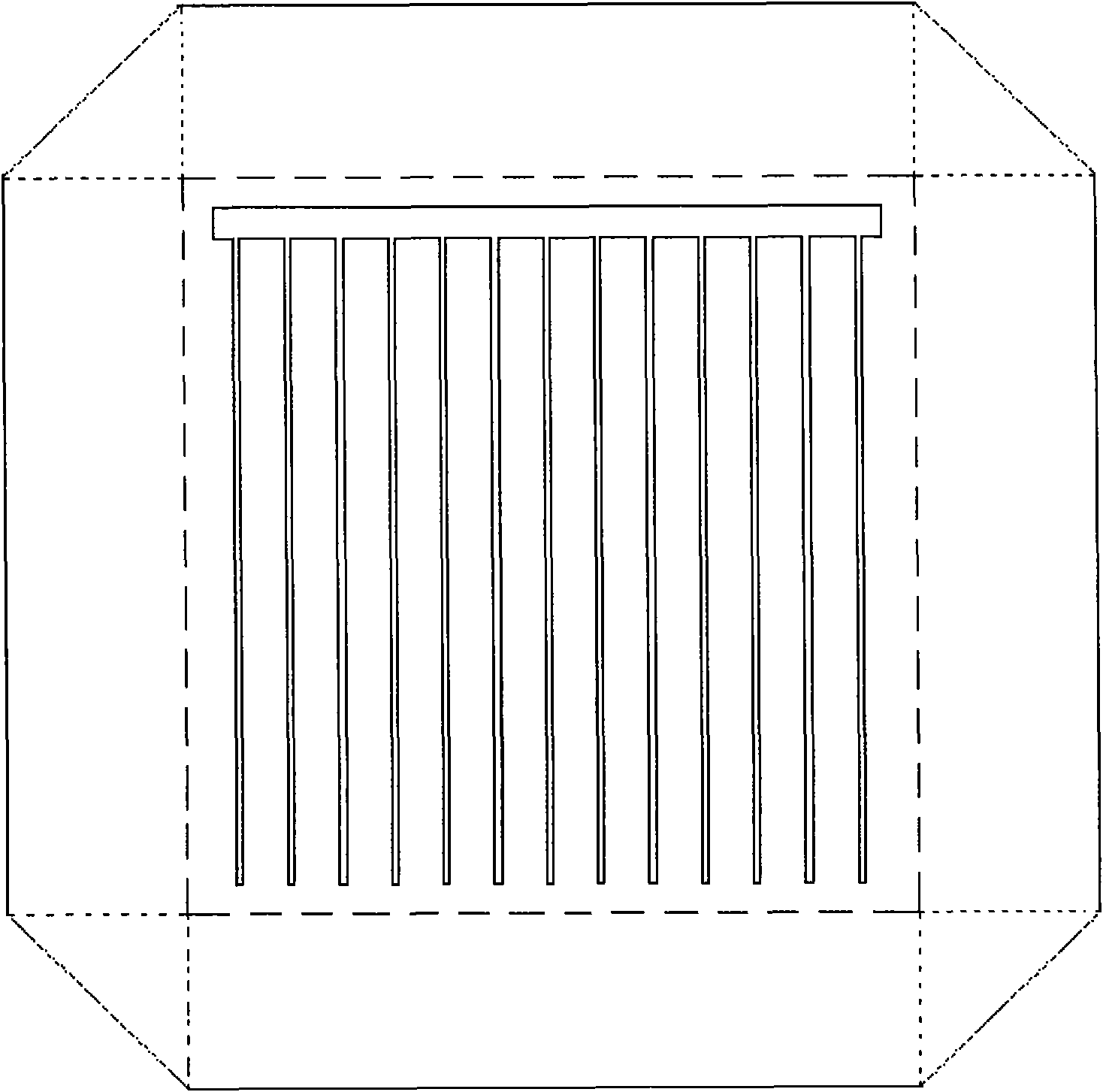

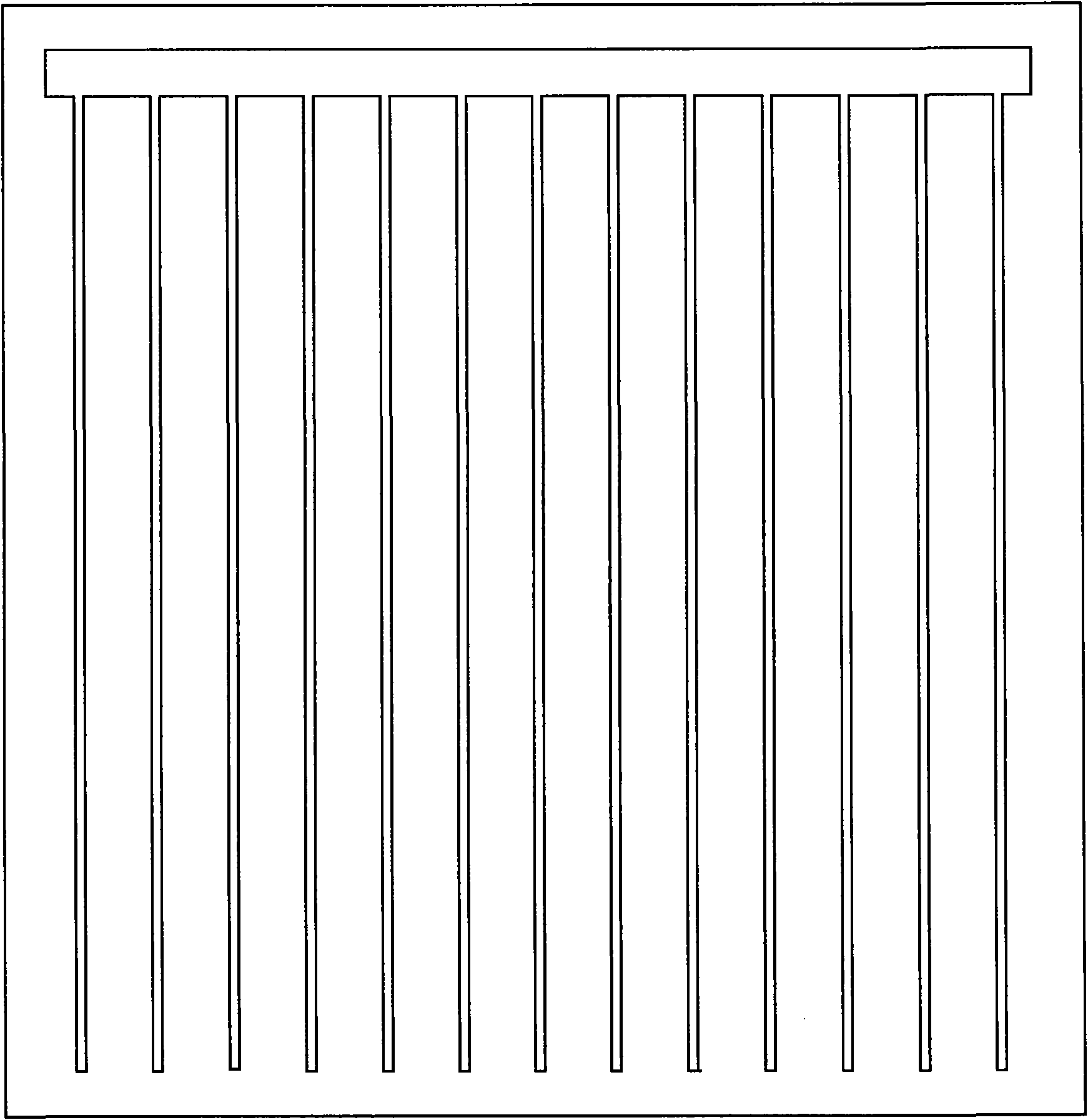

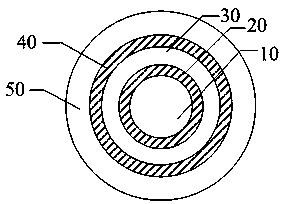

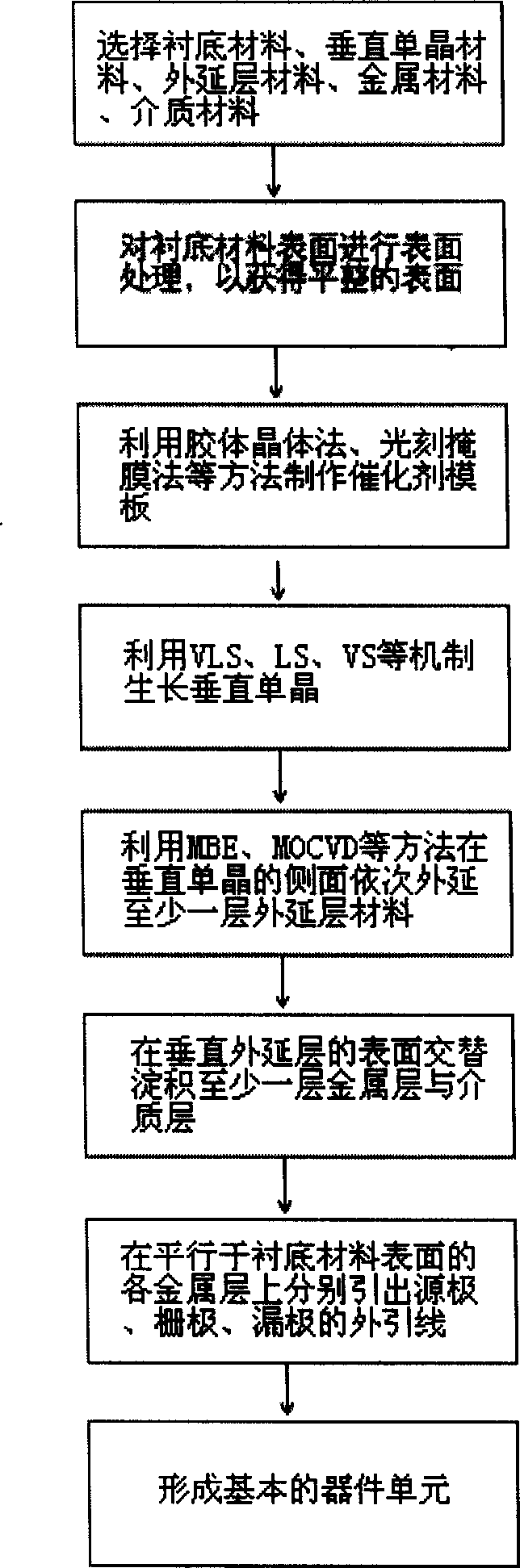

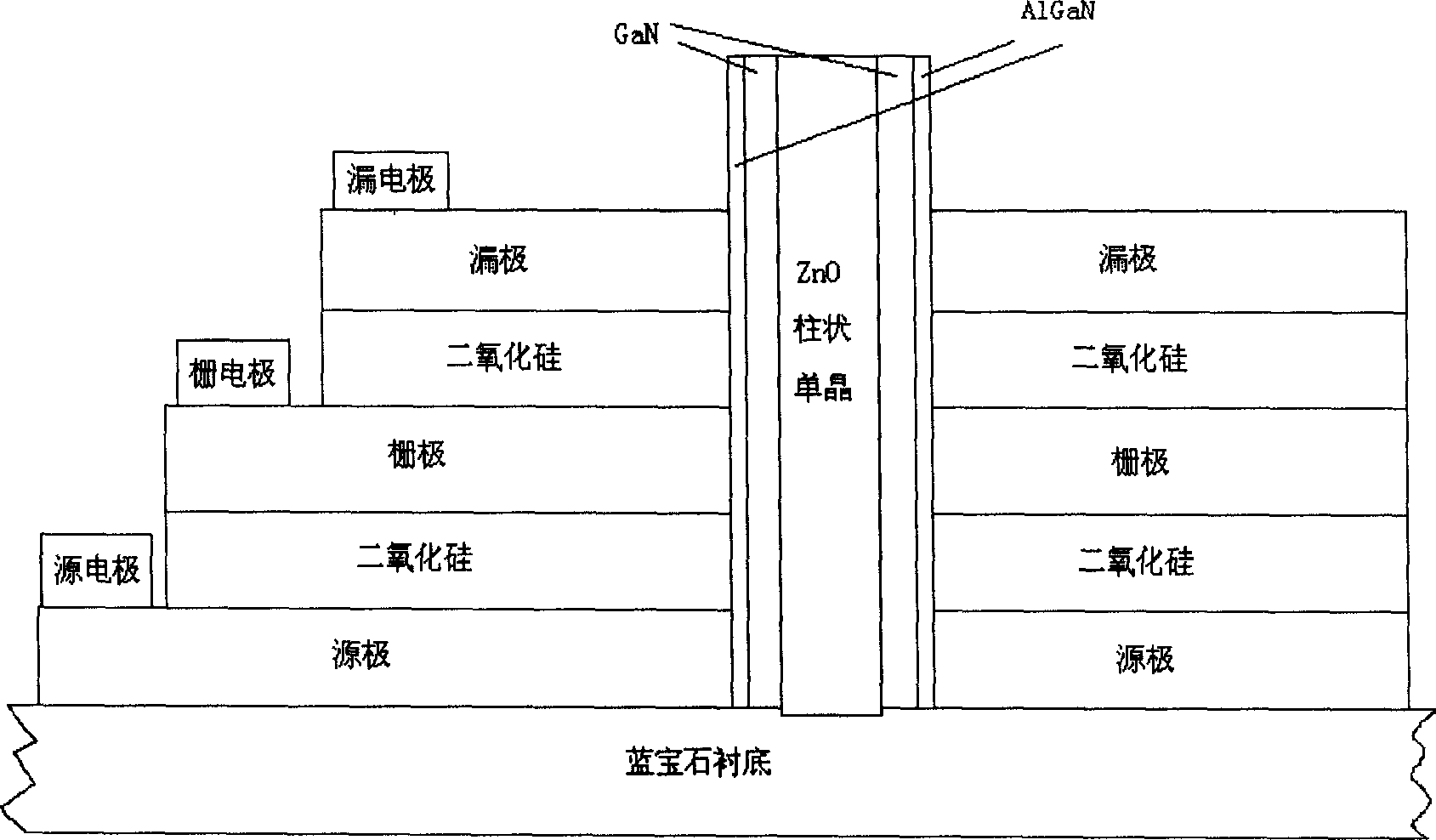

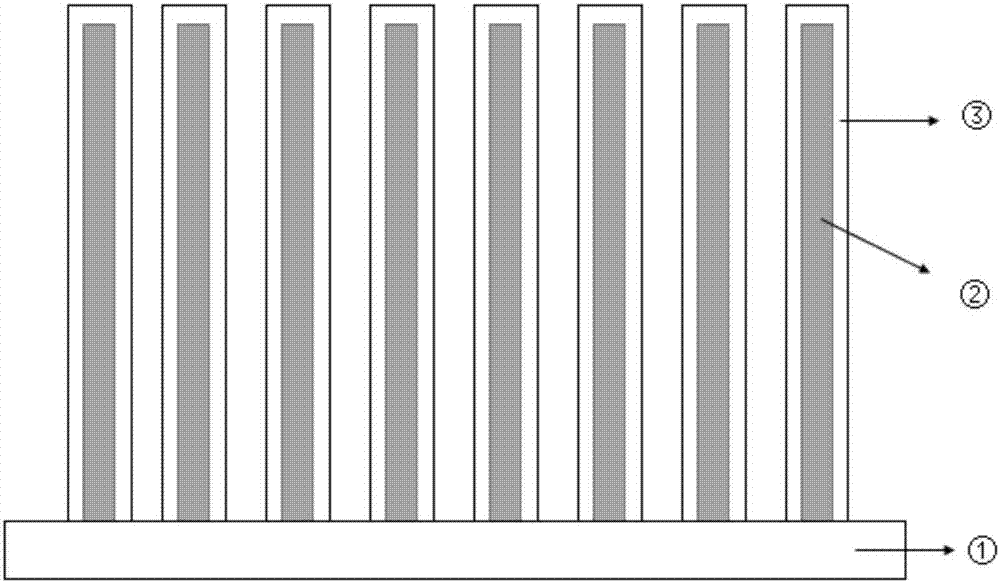

Vertical type wide bandgap semiconductor device structure and making method

InactiveCN1731587AImprove cooling effectQuality improvementSemiconductor/solid-state device manufacturingSemiconductor devicesMicrowaveSemiconductor materials

The invention discloses a vertical semiconductor component structure and preparing method, f or resolving the high defect concentration of wide forbidden band semiconductor materials / components and the heat dissipation of high power devices. The inventive structure exploits three-dimensional nanometer structure and comprises: substrate, vertical single crystal, epitaxial layer, metal layer, medium layer, wherein the vertical single crystal is vertical to the substrate, the epitaxial layer is vertical to the vertical single crystal and the metal layer is parallel to the surface of the substrate, and at least one layer, the medium layer is parallel between each metal layers for isolation; the surface of metal layer and epitaxial layer form the ohmic contact or rectifying contact; connecting out leads on the surface of metal layers. The invention has the advantages of good dissipation of heat, high electric property.

Owner:XIDIAN UNIV

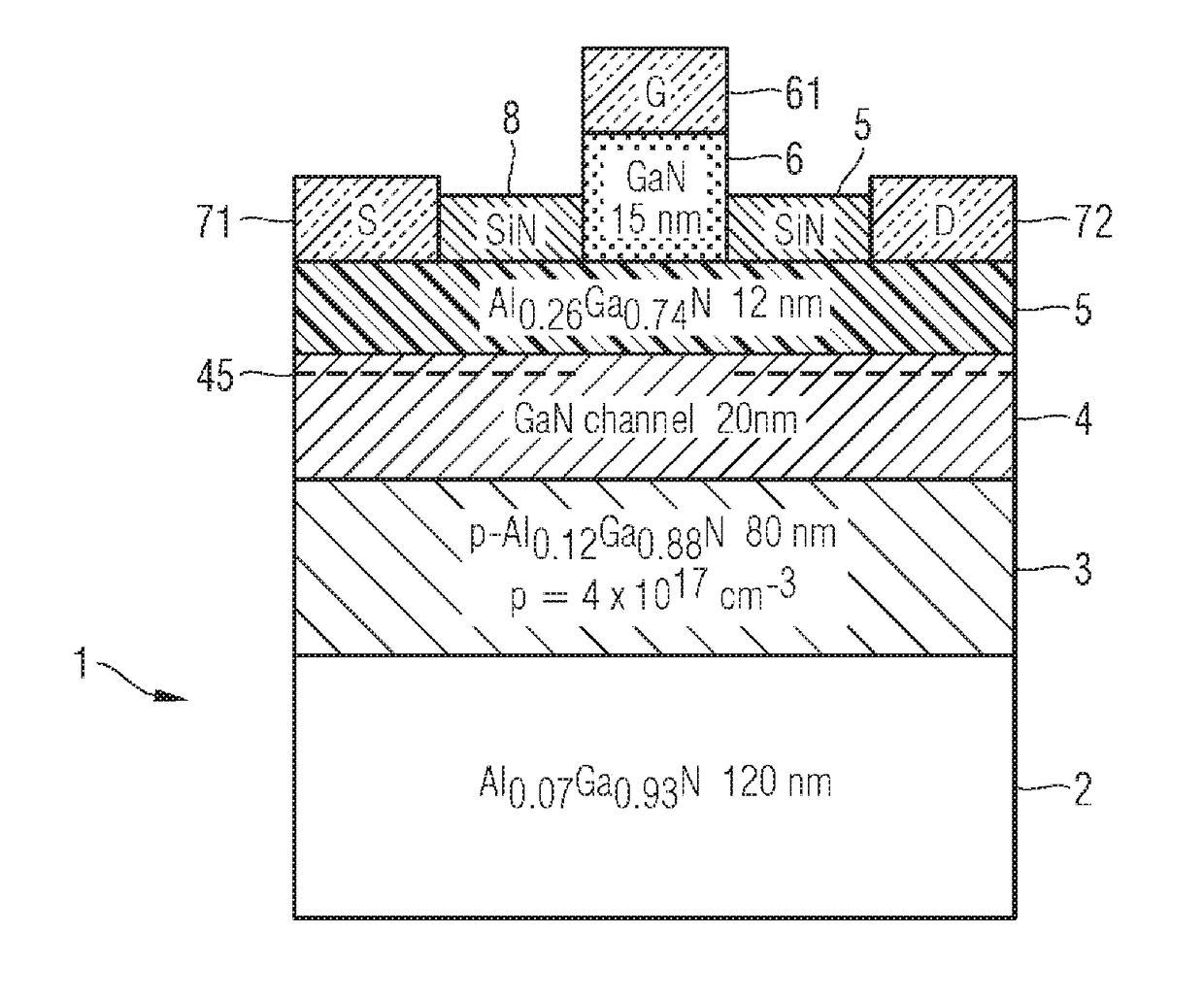

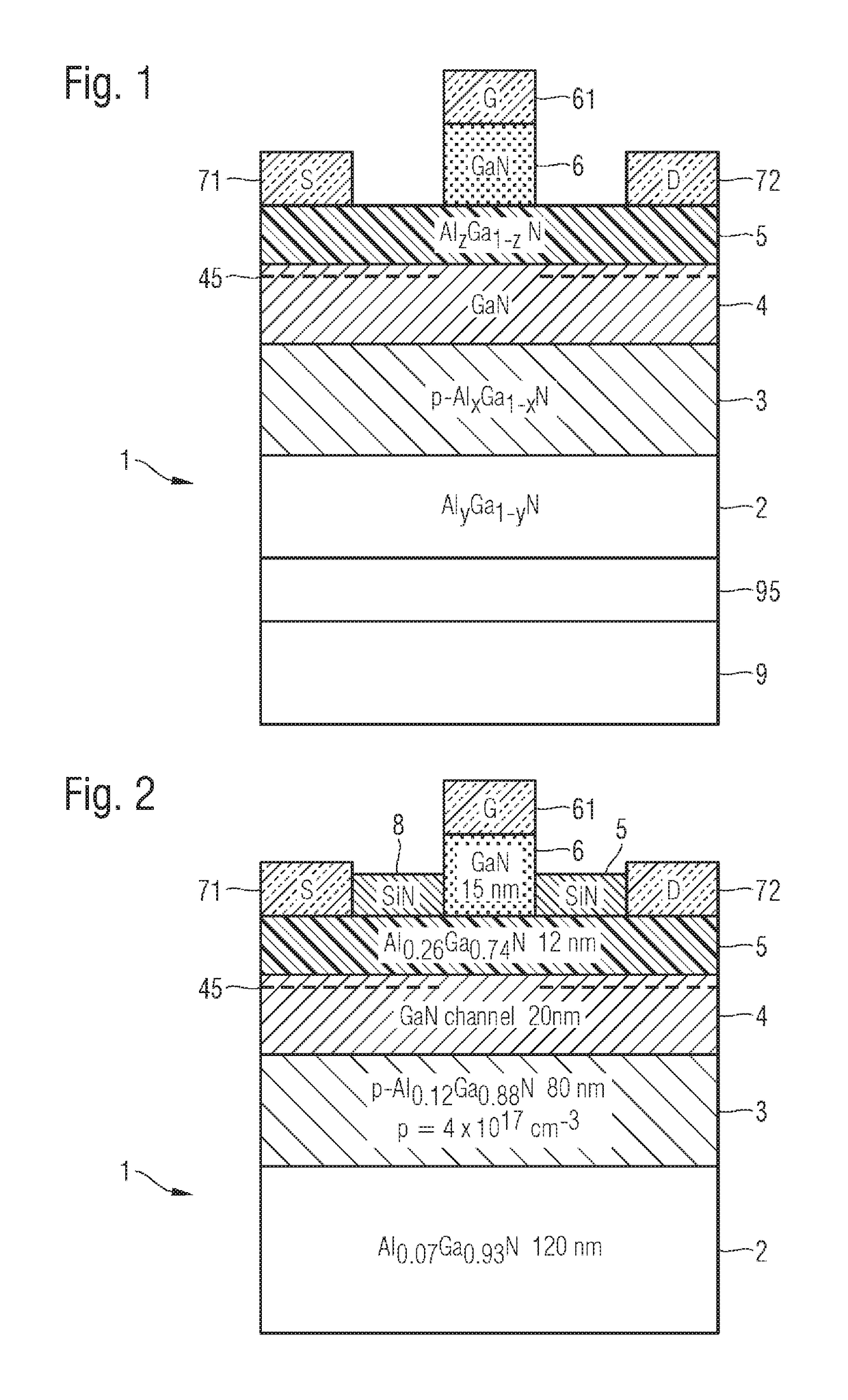

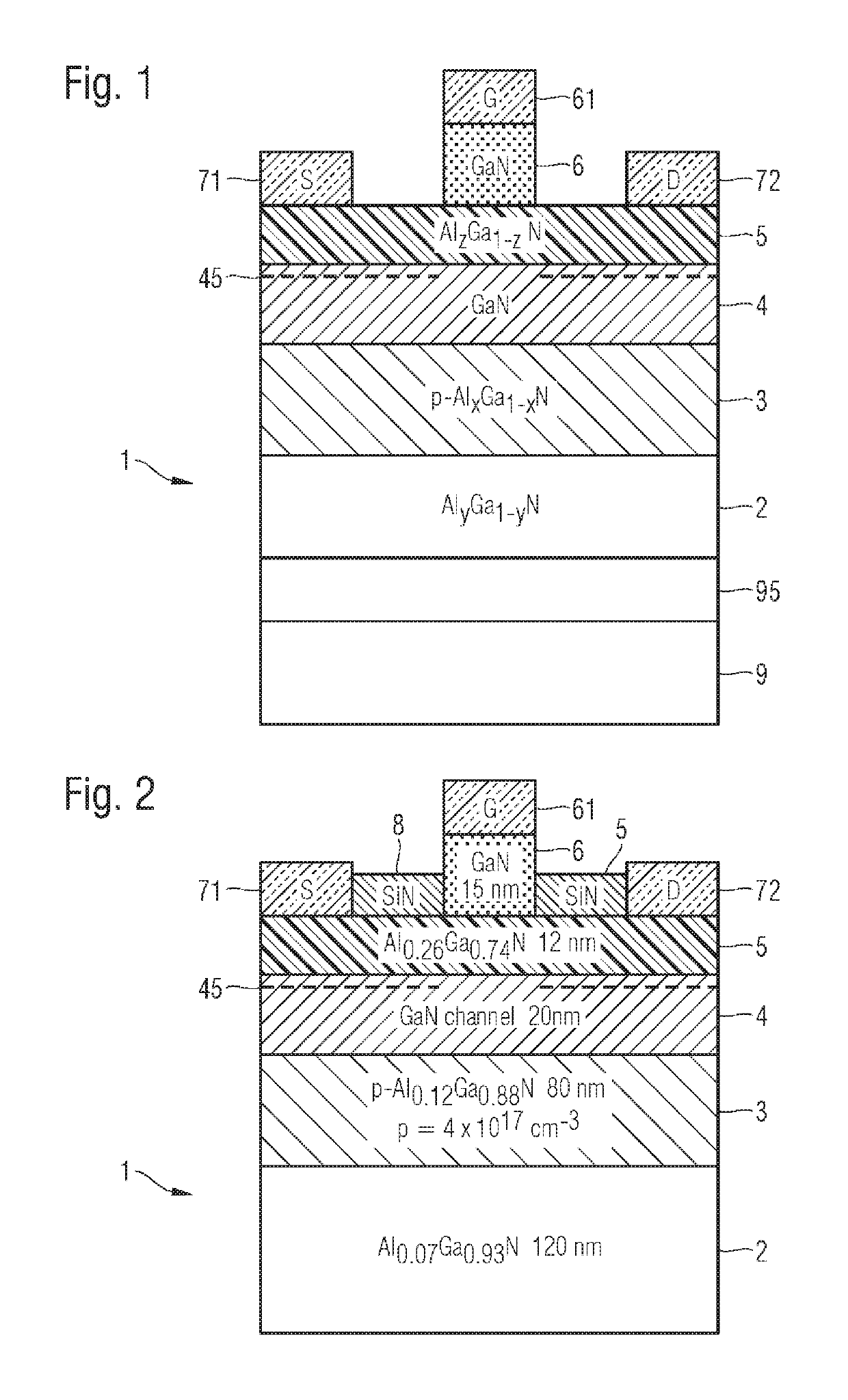

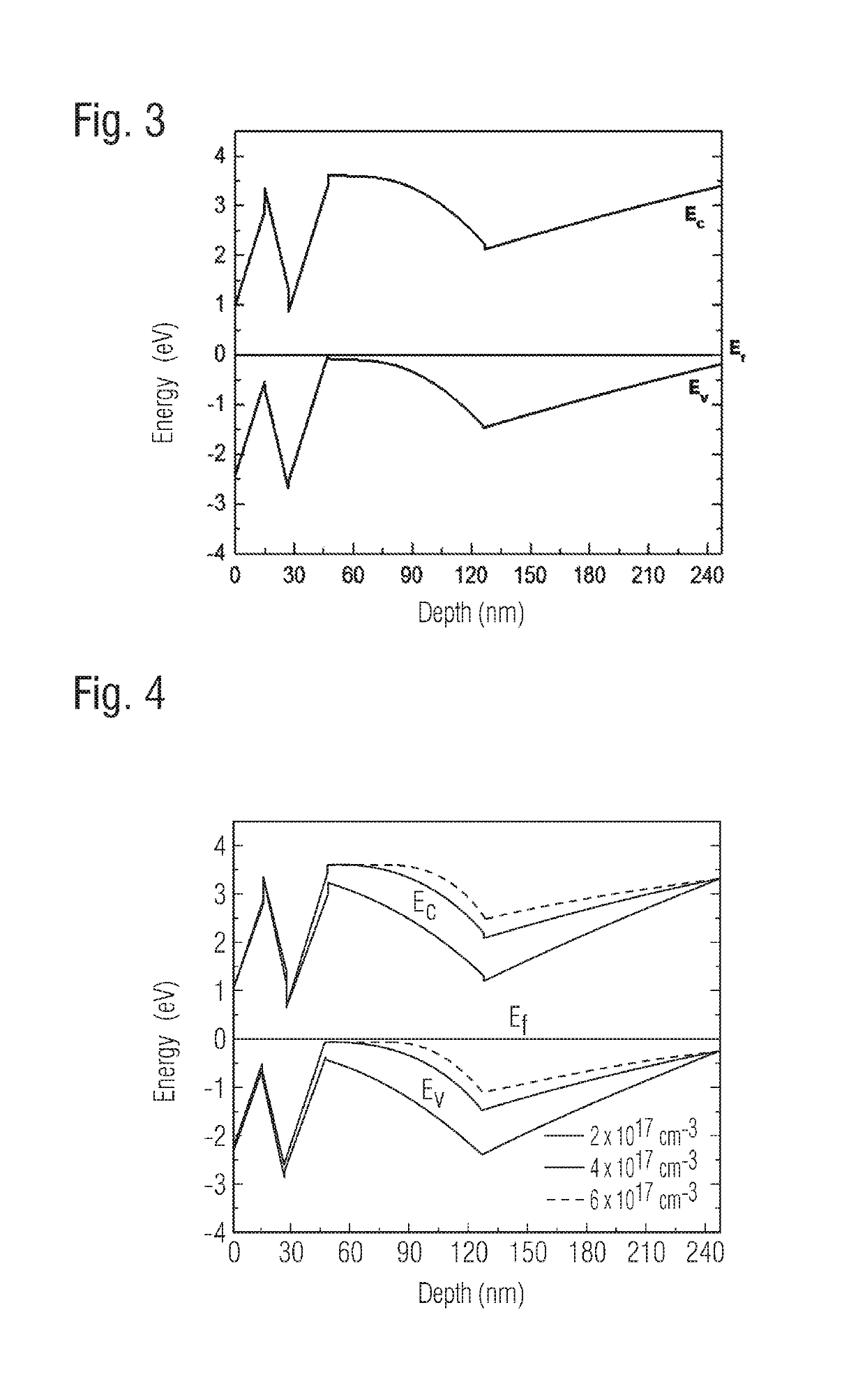

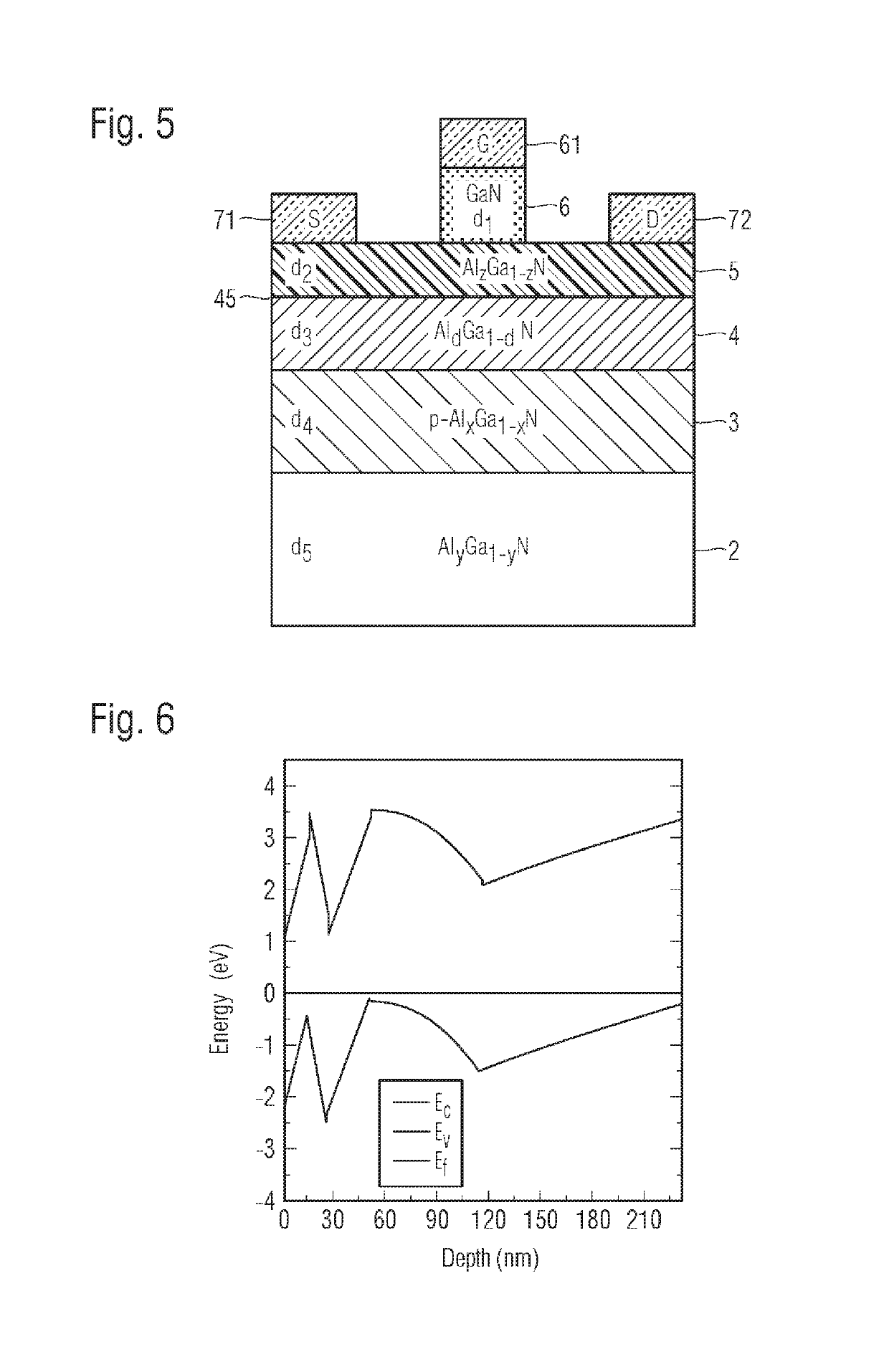

Semiconductor Device

ActiveUS20170373177A1Reduce lattice mismatchReduce leakage currentTransistorPower semiconductor deviceDopant

The invention relates to a semiconductor component comprising at least one field effect transistor, said transistor comprising at least a back barrier layer, a buried layer arranged on the back barrier layer, a channel layer arranged on the buried layer, a barrier layer arranged on the channel layer, and a gate layer arranged on the barrier layer, wherein the barrier layer comprises AlzGa1-zN and wherein the buried layer comprises AlxGa1-xN and at least one dopant causing a p-type conductivity, and wherein the gate layer comprises any of GaN and / or AluInvGa1-v-uN. A field effect transistor according to the disclosure may be configured to show a gate threshold voltage which is higher than approximately 0.5 V or higher than approximately 1.0 V.

Owner:FRAUNHOFER GESELLSCHAFT ZUR FOERDERUNG DER ANGEWANDTEN FORSCHUNG EV

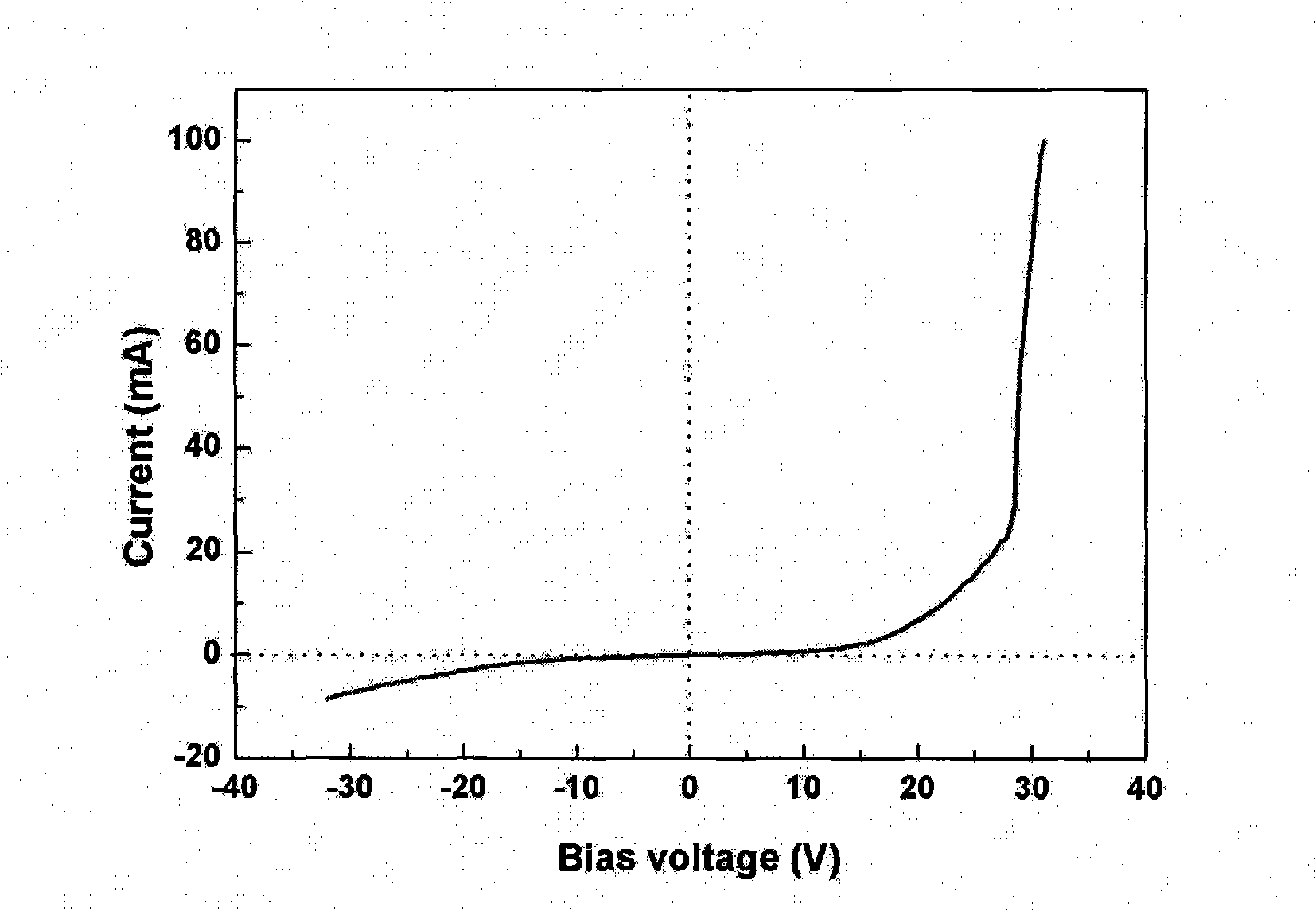

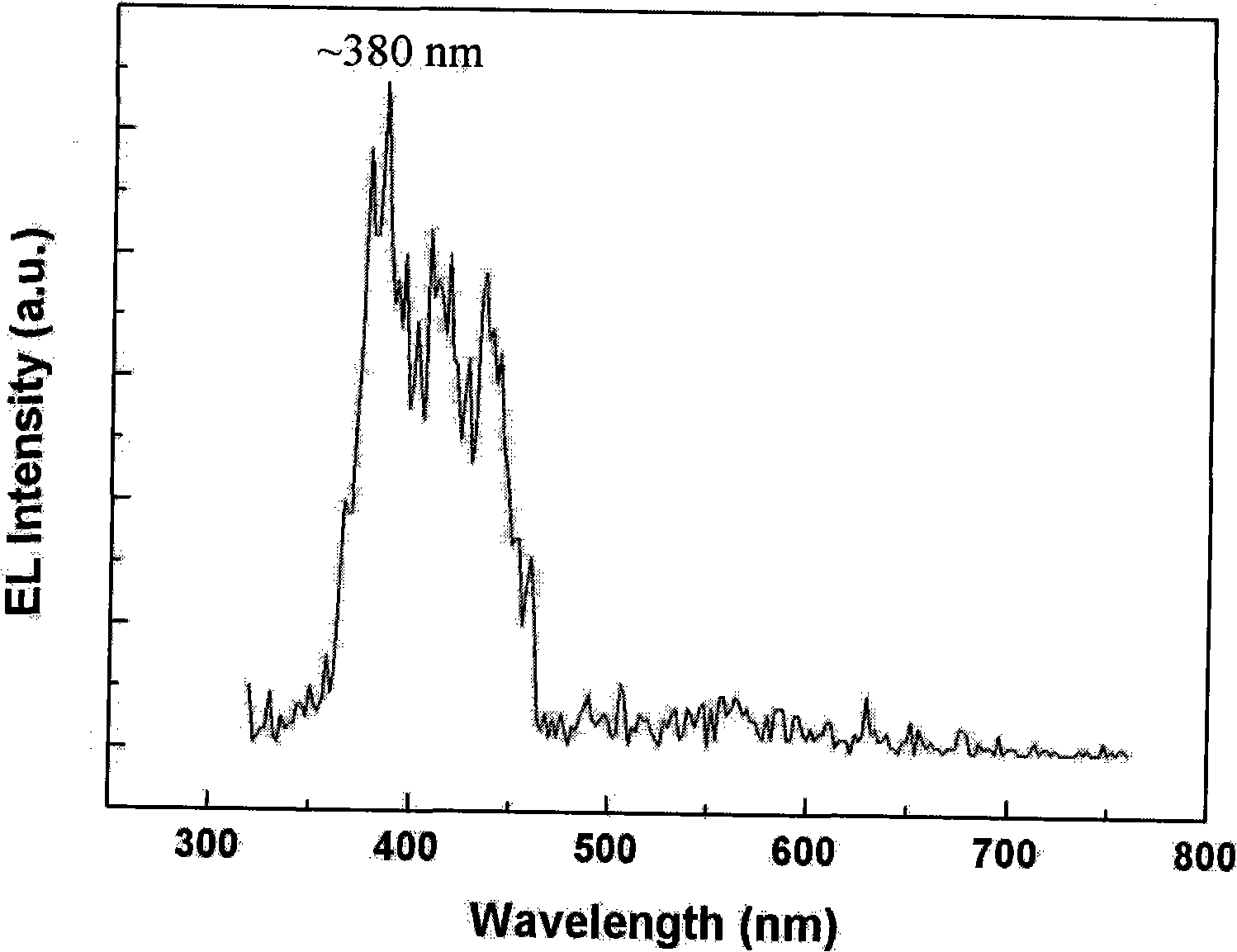

ZnO based LED of multiple quantum wells

InactiveCN101359706AReduce lattice mismatchImprove luminous efficiencySemiconductor devicesLight-emitting diodeCrystallization

The invention discloses a ZnO MQW (Multi-Quantum well) luminous diode. A ZnO buffer layer, an n-type ZnO layer, an n-type Zn1-xMgxO confinement layer, a Zn1-xMgxO / Zn1-yCdyO MQW layer formed by the alternative deposition of Zn1-xMgxO and Zn1-yCdyO, a Na-doped p-type Zn1-xMgxO film, a Na-doped p type ZnO film layer and a second electrode are sequentially arranged from upper to lower on a substrate. A first electrode and the n-type Zn1-xMgxO confinement layer are deposited on the n-type ZnO layer in parallel. The ZnO MQW (Multi-Quantum well) luminous diode is of good crystallization quality, good optical performance, good electric performance and high luminous efficiency.

Owner:ZHEJIANG UNIV

Blue-light LED (Light-Emitting Diode) epitaxial structure having asymmetrical barrier layer

ActiveCN104253182ASuppression of electron floodingReduce lattice mismatchSemiconductor devicesBlock layerElectron blocking layer

The invention discloses a blue-light LED (Light-Emitting Diode) epitaxial structure having an asymmetrical barrier layer, and relates to the technical field of epitaxy of light-emitting diodes. The structure comprises a sapphire substrate, an AlN (Aluminum Nitride) buffer layer, a U type GaN (Gallium Nitride) layer, an N type GaN layer, an active region, an electron blocking layer and a P type GaN layer in sequence from bottom to top, wherein the active region comprises a trap layer and a barrier layer; the growing period number of the active region is 3m; the active region comprises three parts, and each part grows for m periods; the barrier layer consists of an AlxGa1-xN layer, an AlyIn1-yN layer and an InzGa1-zn layer; and m is greater than or equal to 1 and smaller than or equal to 5. Compared with the prior art, the blue-light LED epitaxial structure has the advantages that an overflow phenomenon can be retarded, and bending of an energy band is reduced; and the internal quantum efficiency is increased, so that the light emitting efficiency is increased effectively.

Owner:NANTONG TONGFANG SEMICON +1

Quantum dot and preparation method thereof

PendingCN109929558AEffective passivationReduce lattice mismatchMaterial nanotechnologyNanoopticsElectrical conductorLattice mismatch

The invention discloses a quantum dot and a preparation method thereof. The quantum dot comprises a quantum dot core, a first metal layer covering the quantum dot core, a first semiconductor shell layer covering the first metal layer, a second metal layer covering the first semiconductor shell layer, and a second semiconductor shell layer covering the second metal layer, wherein the metal elementsin the first metal layer and the second metal layer are independently one or a plurality of elements selected from Zn, Hg, Al, Ga and In. According to the present invention, the metal layer can be bonded to the quantum dot core by using the ligand on the surface of the quantum dot core as the linker so as to promote the surface activation of the quantum dot core, such that the further growth reaction of the semiconductor shell layer outside the quantum dot can be easily performed; and through the crystal structure formed by bonding the metal atom in the metal layer and the quantum dot core, the surface of the quantum dot core can be effectively passivated, the surface defect can be reduced, and the lattice mismatch between the core and the shell can be reduced, such that the light emitting efficiency and the size uniformity of the quantum dot material can be enhanced.

Owner:TCL CORPORATION

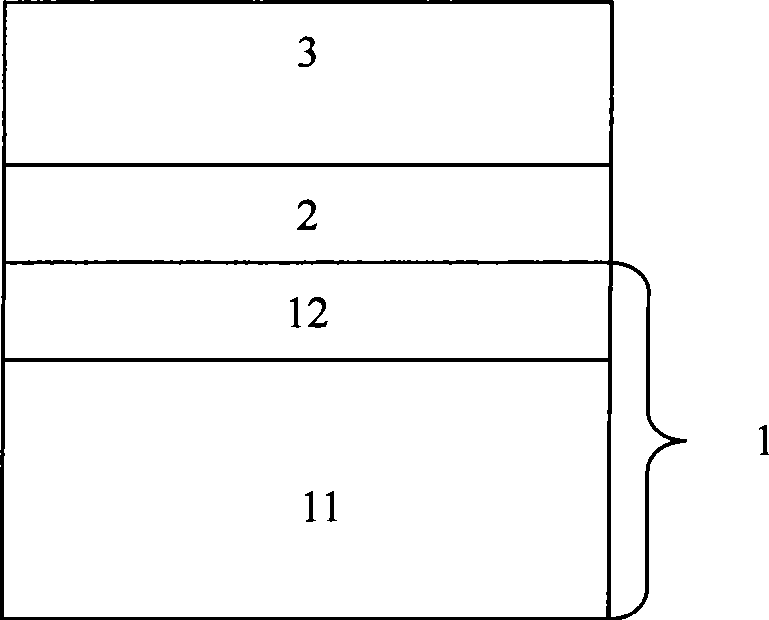

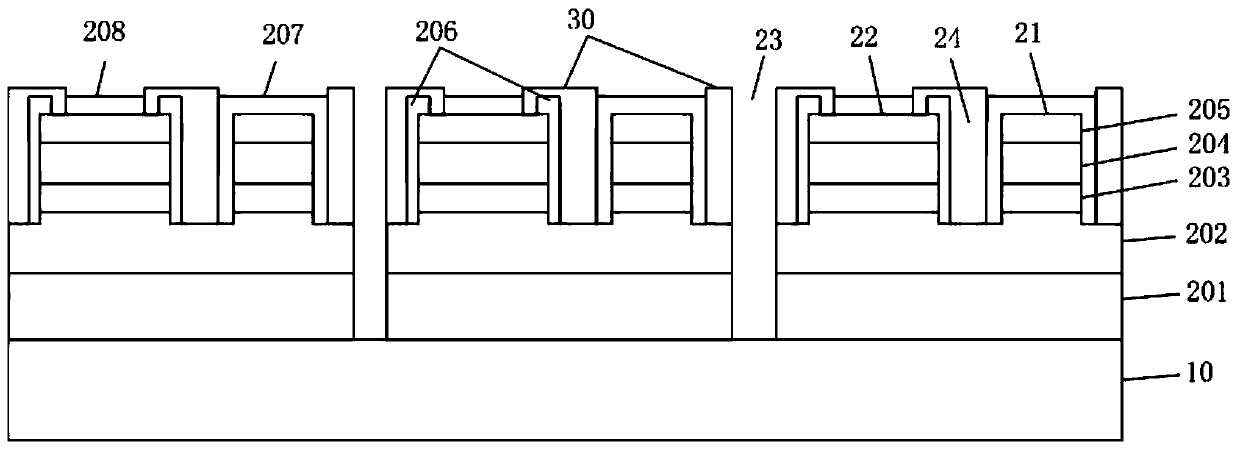

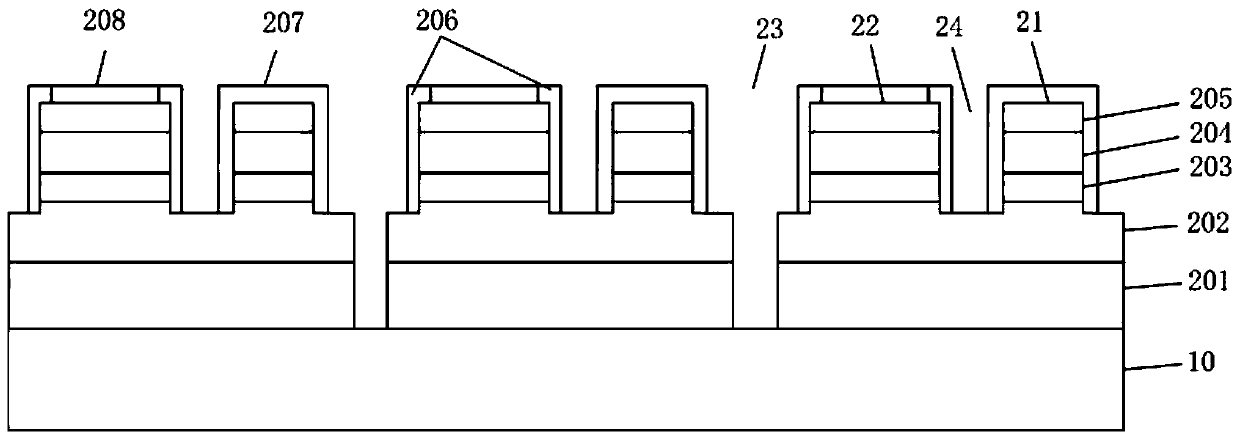

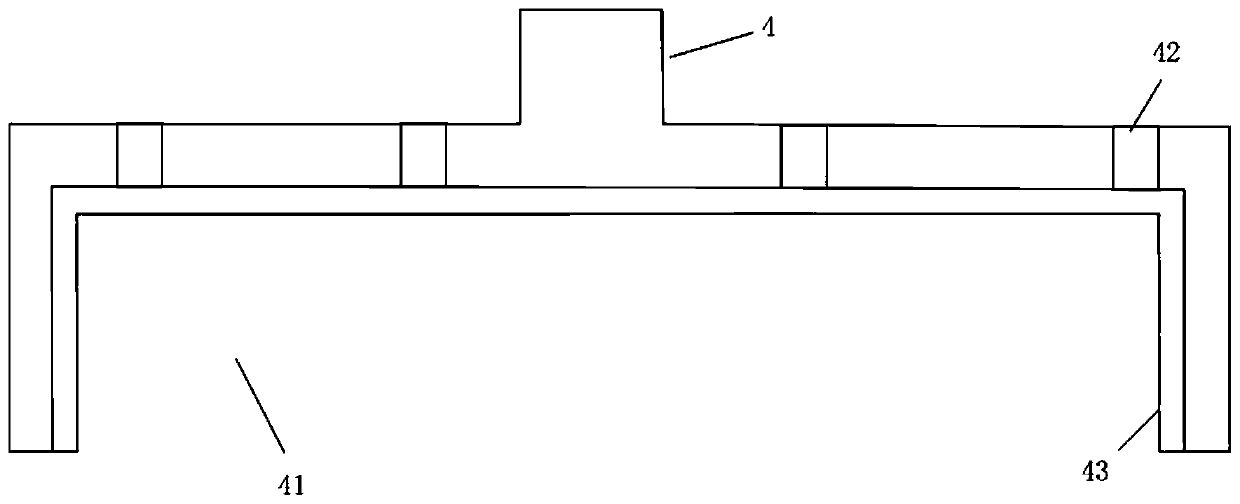

P-type cap layer enhanced HEMT device and preparation method thereof

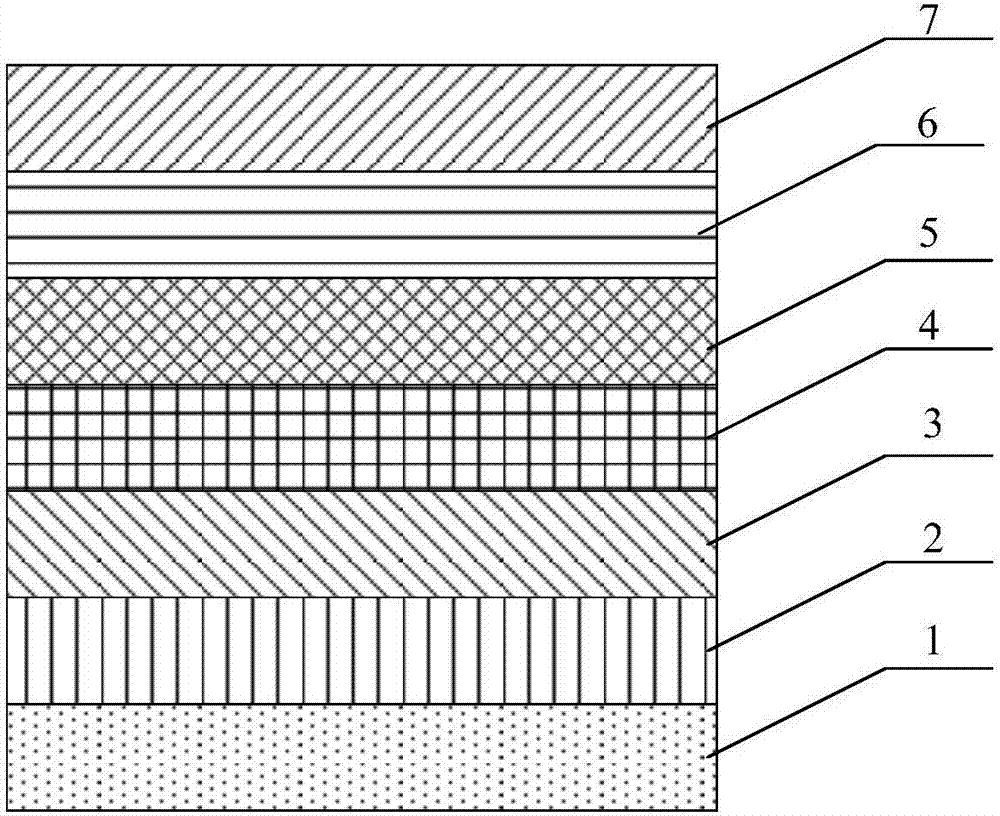

PendingCN112133749AAchieve epitaxial preparationEnabling Enhanced Epitaxy FabricationSemiconductor/solid-state device manufacturingSemiconductor devicesPhysical chemistryMaterials science

The invention discloses a P-type cap layer enhanced HEMT (High Electron Mobility Transistor) device and a preparation method thereof, and belongs to the technical field of microelectronics. The devicecomprise a substrate, a low-temperature nucleating layer, a buffer layer, a high-resistance layer, a channel layer, a barrier layer, an insertion layer and a P-GaN cap layer which are sequentially stacked from bottom to top. The invention provides a new structure and a new growth method, so that the epitaxial preparation of the enhanced HEMT device is realized, and the stability of the performance of the enhanced HEMT device is ensured.

Owner:西安电子科技大学芜湖研究院

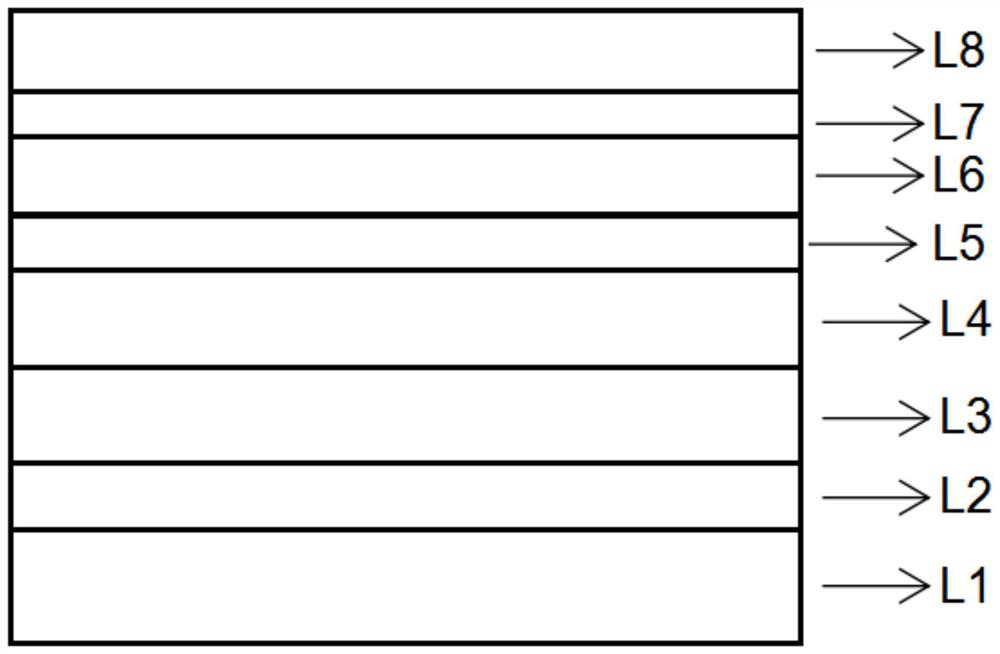

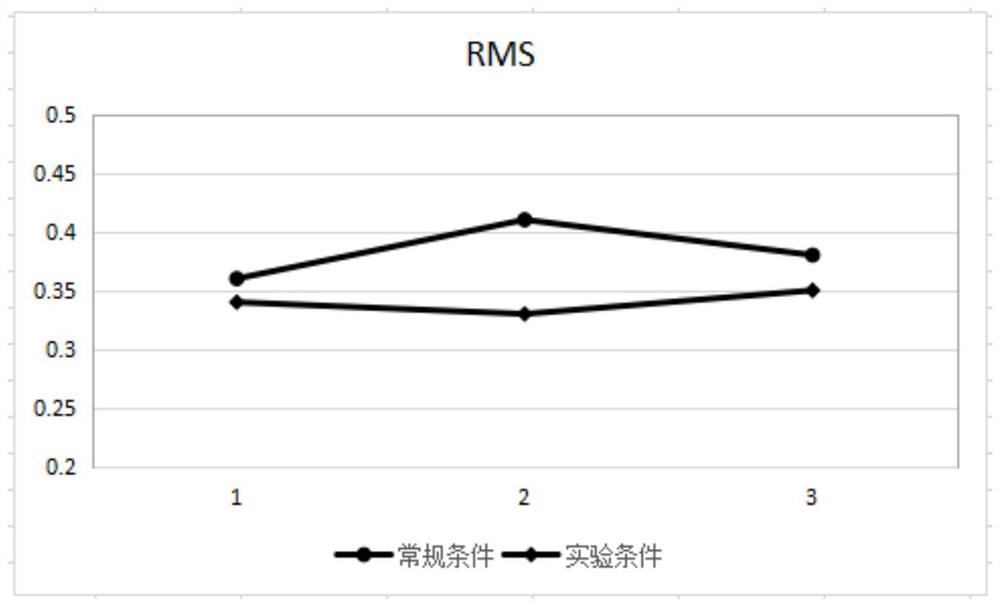

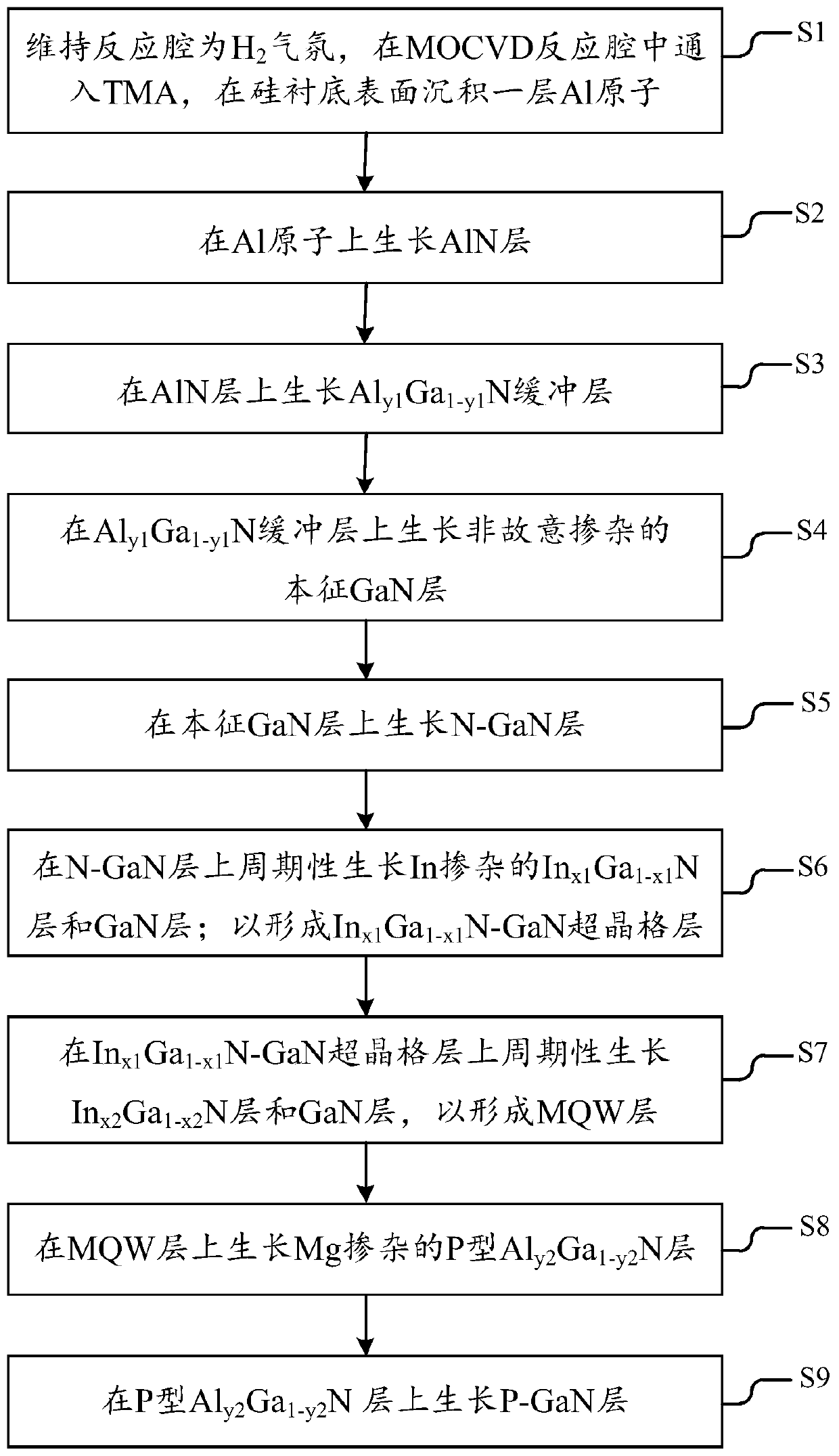

Preparation method of silicon substrate GaN-based epitaxial structure and epitaxial structure

InactiveCN110635001AReduced barrier spikesReduced valence barrier differenceSemiconductor devicesValence bandLattice mismatch

The invention discloses a preparation method of a silicon substrate GaN-based epitaxial structure. The preparation method comprises the following steps: forming Al atoms, a AlN layer, a Aly1Ga1-y1N buffer layer, an intrinsic GaN layer, a N-GaN layer, an Inx1Ga1-x1N-GaN superlattice layer, a MQW Layer, a P-type Aly2Ga1-y2N layer and a P-GaN layer on the surface of a silicon substrate so as to obtain a finished product of the silicon substrate GaN-based epitaxial structure, wherein the value range of y2 is 0-0.3 and y2 increases with the increase of the thickness of the P-type Aly2Ga1-y2N layerin the P-type Aly2Ga1-y2N layer. The P-type Aly2Ga1-y2N layer can reduce the barrier difference between the last barrier layer and the P-type Aly2Ga1-y2N layer, i.e. the lattice mismatch between the last barrier layer and the P-type Aly2Ga1-y2N layer so as to avoid the introduction of large strain and polarization field, reduce the barrier spike formed by the valence band of the electron barrier layer and reduce the obstacle of hole injection. Meanwhile, the barrier of the conduction band of electron barrier layer increases with the increase of Al composition and the blocking effect on electron overflow quantum well is enhanced, and thus the radiation recombination efficiency of the quantum well region can be increased and the brightness of LED can be improved.

Owner:FOSHAN NATIONSTAR SEMICON

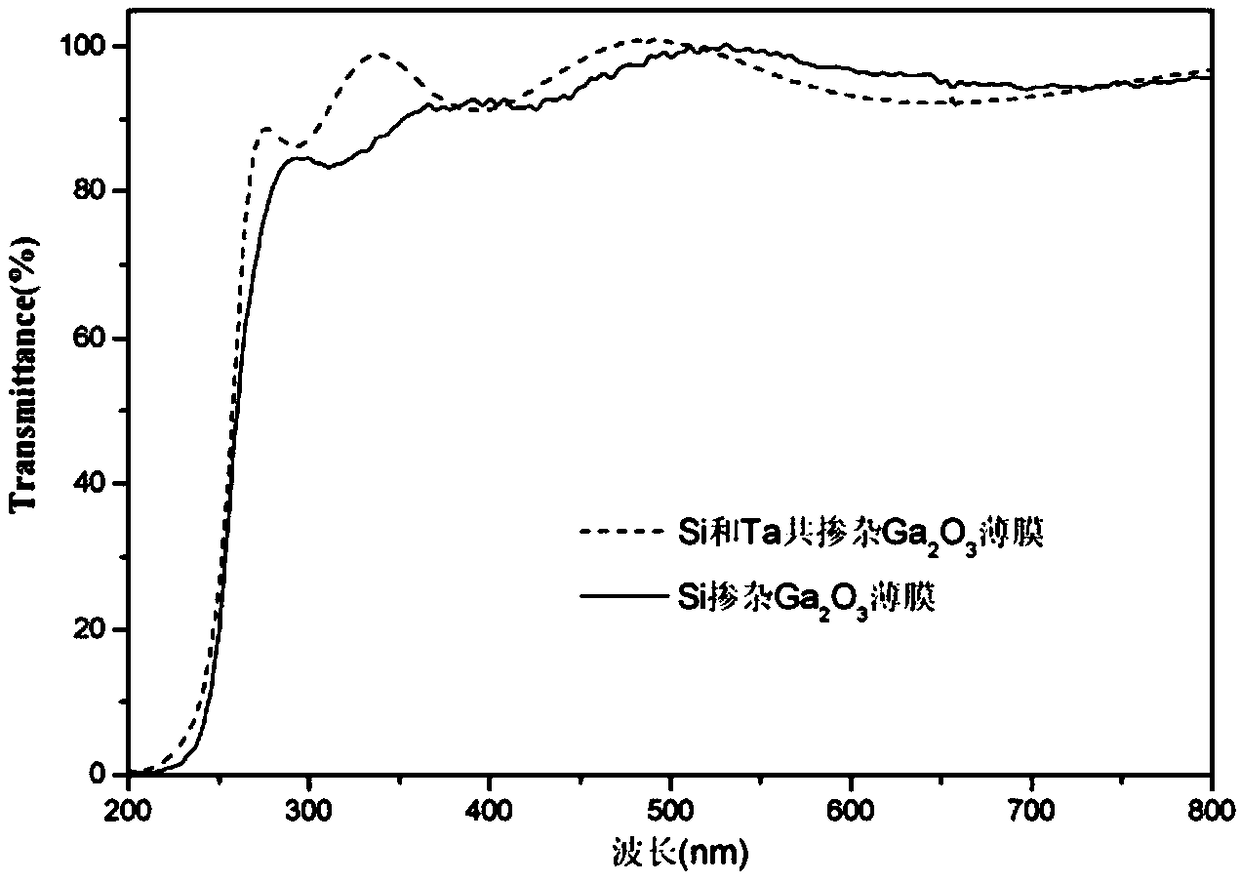

Ga2O3-based transparent conducting thin film and preparation method thereof

ActiveCN109082631AImprove conductivityWeaken energyVacuum evaporation coatingSputtering coatingHigh concentrationUltraviolet

The invention relates to a Ga2O3-based transparent conducting thin film and a preparation method thereof. The transparent conducting thin film is an n-type thin film with high concentration obtained by mixing Si and Ta elements into a Ga2O3 thin film. A thin film deposition method is adopted in the Ga2O3-based transparent conducting thin film is laser pulse deposition method, and the Ga2O3-based transparent conducting thin film is deposited on the substrate surface after a laser beam bombards Ca2O3-based adulteration mixed target. The obtained Ga2O3-based transparent conducting thin film has higher carrier concentration (>4 *10<19> cm<-3>) and good electrical conductivity, has high light-admitting quality (>82%) in deep ultra violet to a visible region, is suitable for as a window layer and an electrode layer material of ultra violet luminescent devices (such as LED, LD), solar-blind detector and other devices, and has a good application prospect.

Owner:SOUTH CHINA NORMAL UNIVERSITY

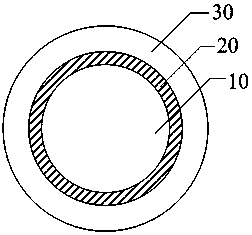

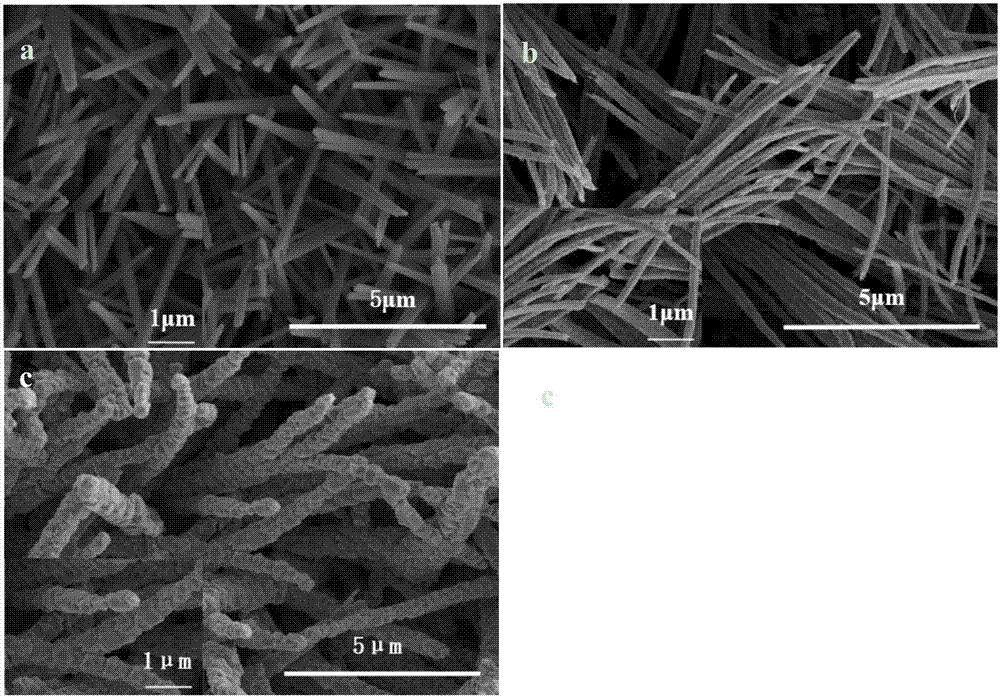

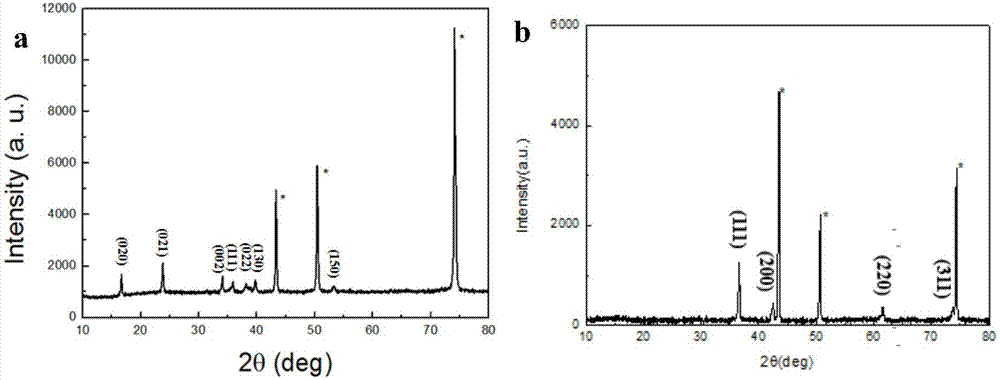

Cuprous oxide nanometer pn homojunction material of core-shell structure and preparation method thereof

ActiveCN107227476AImprove photoelectrochemical performanceImprove performanceMaterial nanotechnologyElectrolytic inorganic material coatingCore shellNanometre

The invention discloses a preparation method of a p-Cu2O / n-Cu2O nanometer homojunction material of a core-shell structure. A substrate of the Cu2O nanometer homojunction material is provided with inner-layer p-Cu2O nanorods and outer-layer n-Cu2O wrapping layers in sequence from bottom to top. The preparation method comprises the steps that (1), a Cu(OH)2 precursor is grown on a copper substrate through an electrochemical deposition method, and a p-CU2O nanorod array is obtained through annealing; and (2), the p-Cu2O is wrapped with a layer of n-Cu2O through the electrochemical deposition method again. According to the method, equipment is simple, operation is easy, the nanometer homojunction is good in crystallization quality, the size is uniform, and distribution is uniform; and wrapping is performed through the electrochemical deposition method, and the nanorod array can be uniformly wrapped with an outer layer directly.

Owner:ZHEJIANG UNIV

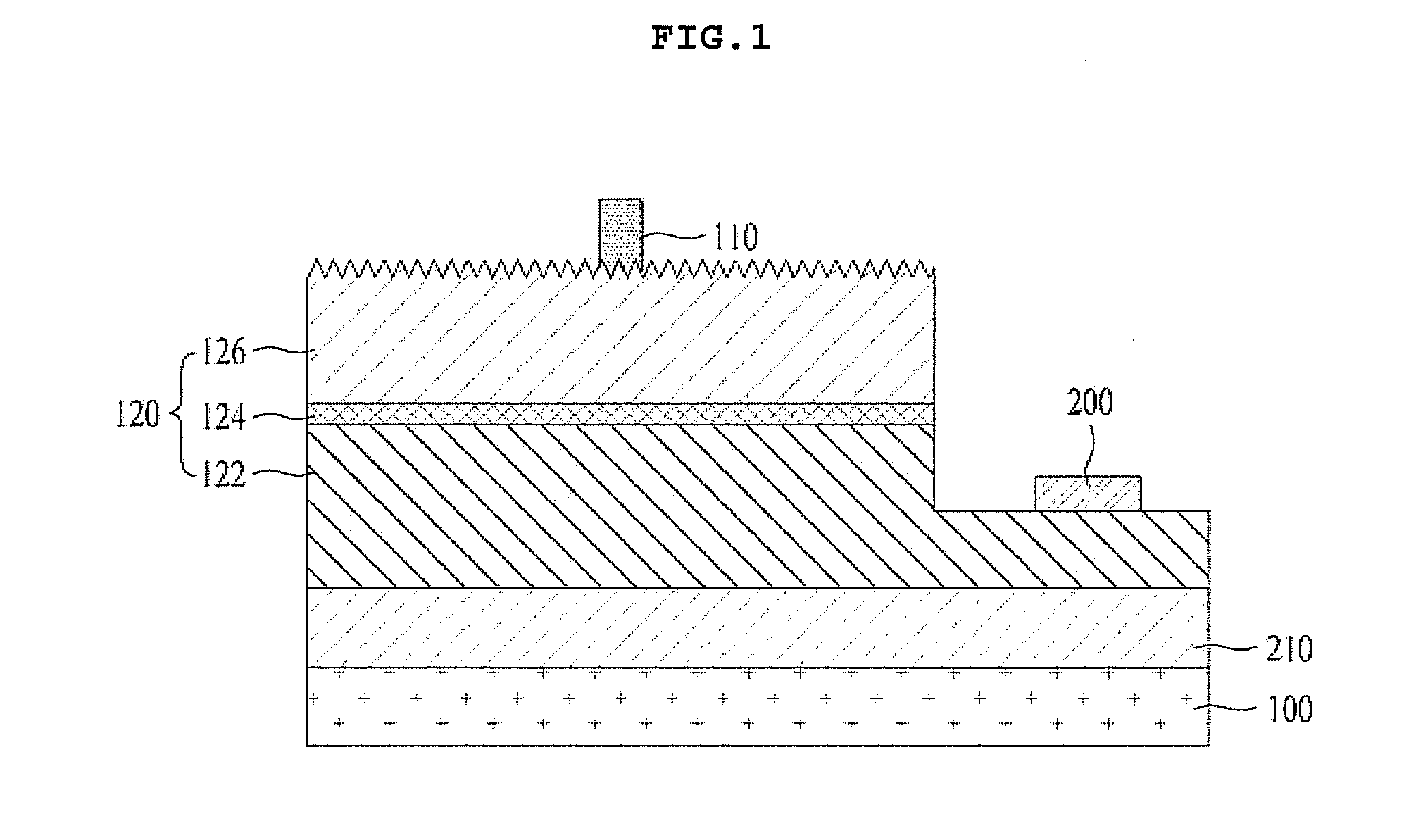

Light emitting diode epitaxial wafer and manufacturing method thereof

ActiveCN109449264AImprove luminous efficiencyIncrease stressSemiconductor devicesLattice mismatchLight-emitting diode

The invention discloses a light emitting diode epitaxial wafer and a manufacturing method thereof, and belongs to the technical field of semiconductors. A multi-quantum-well layer of the light emitting diode epitaxial wafer is of a multi-cycle superlattice structure, wherein each superlattice structure comprises an InGaN quantum well layer, and a transition layer and a GaN quantum barrier layer which are sequentially stacked on the InGaN quantum well layer; the transition layer comprises a first sub-layer and a second sub-layer arranged on the first sub-layer, wherein the first sub-layer is anAlInN layer, and the second sub-layer is an AlGaN layer. The AlInN material is relatively matched with the InGaN material lattice, the AlGaN material is relatively matched with the crystal lattice ofthe GaN material, and the AlInN material is relatively matched with the lattice of the GaN material, so that the lattice mismatch between the InGaN quantum well layer and the GaN quantum barrier layer can be reduced by arranging the first sub-layer and the second sub-layer, and therefore the defects are reduced, and the radiation composite luminescence efficiency of electrons and holes in the multi-quantum well layer is improved.

Owner:HC SEMITEK SUZHOU

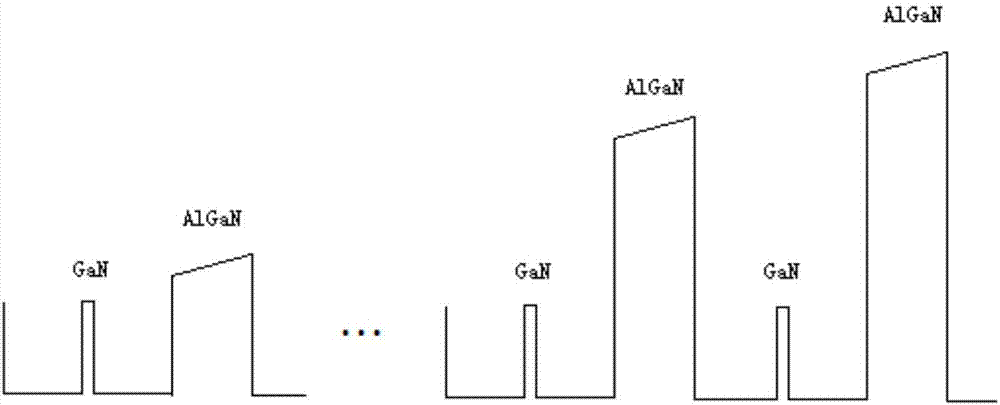

Ultraviolet light-emitting diode (LED) epitaxial structure and growth method thereof

ActiveCN107316925AImprove concentration distributionReduce lattice mismatchSemiconductor devicesElectron blocking layerCharge carrier

The invention provides an ultraviolet light-emitting diode (LED) epitaxial structure. The epitaxial structure sequentially comprises an AlN Buffer layer, a high-temperature UGaN layer, a composite N-type GaN layer, a multi-quantum well (MQW) structure, an active region light-emitting quantum-well layer, an electron blocking layer (EBL) and a P-type GaN layer from bottom to top, wherein the active region light-emitting quantum-well layer comprises n layers of In<x>Ga<1-x>N / Al<y>Ga<1-y>N multi-quantum wells, each layer of In<x>Ga<1-x>N / Al<y>Ga<1-y>N multi-quantum well comprises a main barrier and a movable barrier, the movable barrier is embedded into the main barrier, the main barrier comprises Al<y>Ga<1-y>N, the height of the main barrier is gradiently increased with the increase of Al constituent, the movable barrier comprises GaN, and the thickness of each layer of movable barrier is 1-20 nanometers. By the ultraviolet LED epitaxial structure and a growth method thereof, the stress in the quantum wells is reduced, the hole injection efficiency is improved, electrons of an active layer is prevented from overflowing, and the carrier recombination probability and the internal quantum efficiency of an ultraviolet LED are improved.

Owner:宁波安芯美半导体有限公司

Semiconductor device

ActiveUS10283630B2Reduce lattice mismatchReduce leakage currentTransistorDopantField-effect transistor

The invention relates to a semiconductor component comprising at least one field effect transistor, said transistor comprising at least a back barrier layer, a buried layer arranged on the back barrier layer, a channel layer arranged on the buried layer, a barrier layer arranged on the channel layer, and a gate layer arranged on the barrier layer, wherein the barrier layer comprises AlzGa1-zN and wherein the buried layer comprises AlxGa1-xN and at least one dopant causing a p-type conductivity, and wherein the gate layer comprises any of GaN and / or AluInvGa1-v-uN. A field effect transistor according to the disclosure may be configured to show a gate threshold voltage which is higher than approximately 0.5 V or higher than approximately 1.0 V.

Owner:FRAUNHOFER GESELLSCHAFT ZUR FOERDERUNG DER ANGEWANDTEN FORSCHUNG EV

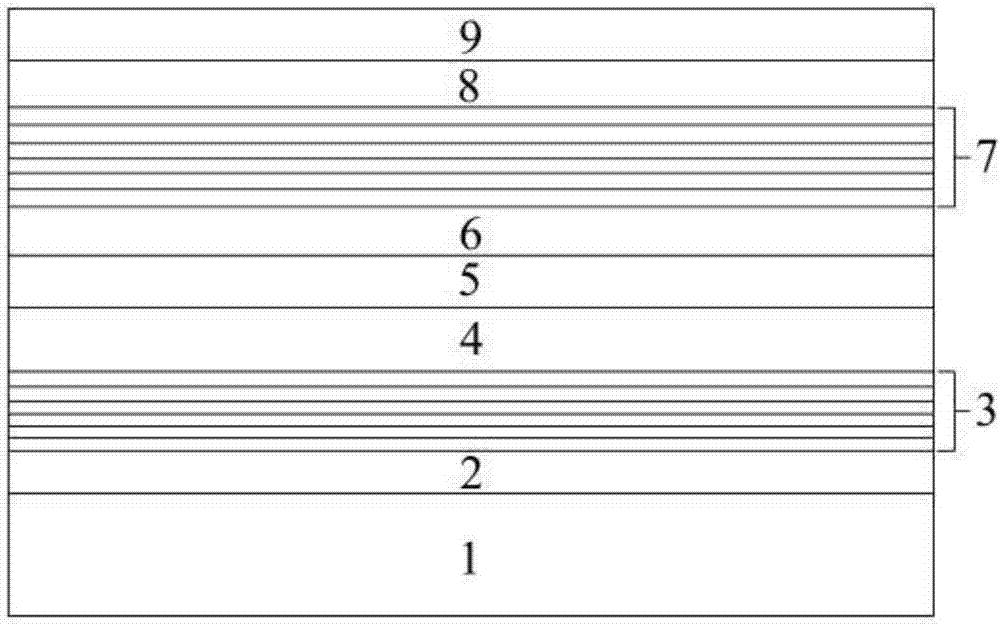

InAs/AlSb high electron mobility transistor (HEMT) epitaxial structure and fabrication method thereof

ActiveCN107123668AReduce lattice mismatchPrevent oxidationSemiconductor/solid-state device manufacturingSemiconductor devicesIsolation layerPhysics

The invention discloses an InAs / AlSb high electron mobility transistor (HEMT) epitaxial structure and a fabrication method thereof. The InAs / AlSb HEMT epitaxial structure disclosed by the invention comprises a substrate, a buffer layer, a AlAs<x>Sb<1-x> lower barrier layer, an InAs channel layer, a AlSb isolation layer, an InAs doping layer, a AlAs<x>Sb<1-x> upper barrier layer, an InAlAs hole barrier layer and an InAs cap layer from bottom to top, wherein the buffer layer employs Si, the AlAs<x>Sb<1-x> lower barrier layer is a AlAs<x>Sb<1-x> barrier layer with a stepped variable constituent mode, and the AlAs<x>Sb<1-x> upper barrier layer is a AlAs<x>Sb<1-x> barrier layer with a stepped variable constituent mode. The AlAs<x>Sb<1-x> lower barrier layer and the AlAs<x>Sb<1-x> upper barrier layer are grown by employing a stepped variable constituent method, and the stability and the reliability of a device are effectively improved.

Owner:XIDIAN UNIV

Nickel-based high-temperature alloy powder and preparation method for applying nickel-based high-temperature alloy powder to hollow turbine blade

ActiveCN114214554ADelayed expansionHigh densityTurbinesAdditive manufacturing apparatusSelective laser meltingTurbine blade

The invention provides nickel-based high-temperature alloy powder and a preparation method for applying the nickel-based high-temperature alloy powder to a hollow turbine blade, and solves the technical problem of cracking in the process of preparing the hollow turbine blade through selective laser melting. The Ni-Cr-Co-Ti-W alloy material comprises the following components in percentage by weight: 25% to 30% of Cr, 17.5% to 19% of Co, 2.5% to 3.0% of Al, 2.3% to 2.5% of Ta, 2.6% to 2.8% of Ti, 1.7% to 2.1% of W, 1.5% to 2.5% of Re, 0.1% to 0.15% of C, 0.8% to 1% of Cb, 0.2% to 0.3% of Zr, 0.005% to 0.01% of B, 0.5% to 0.7% of V and the balance of Ni. The method can be widely applied to the technical field of additive manufacturing.

Owner:HARBIN INST OF TECH AT WEIHAI

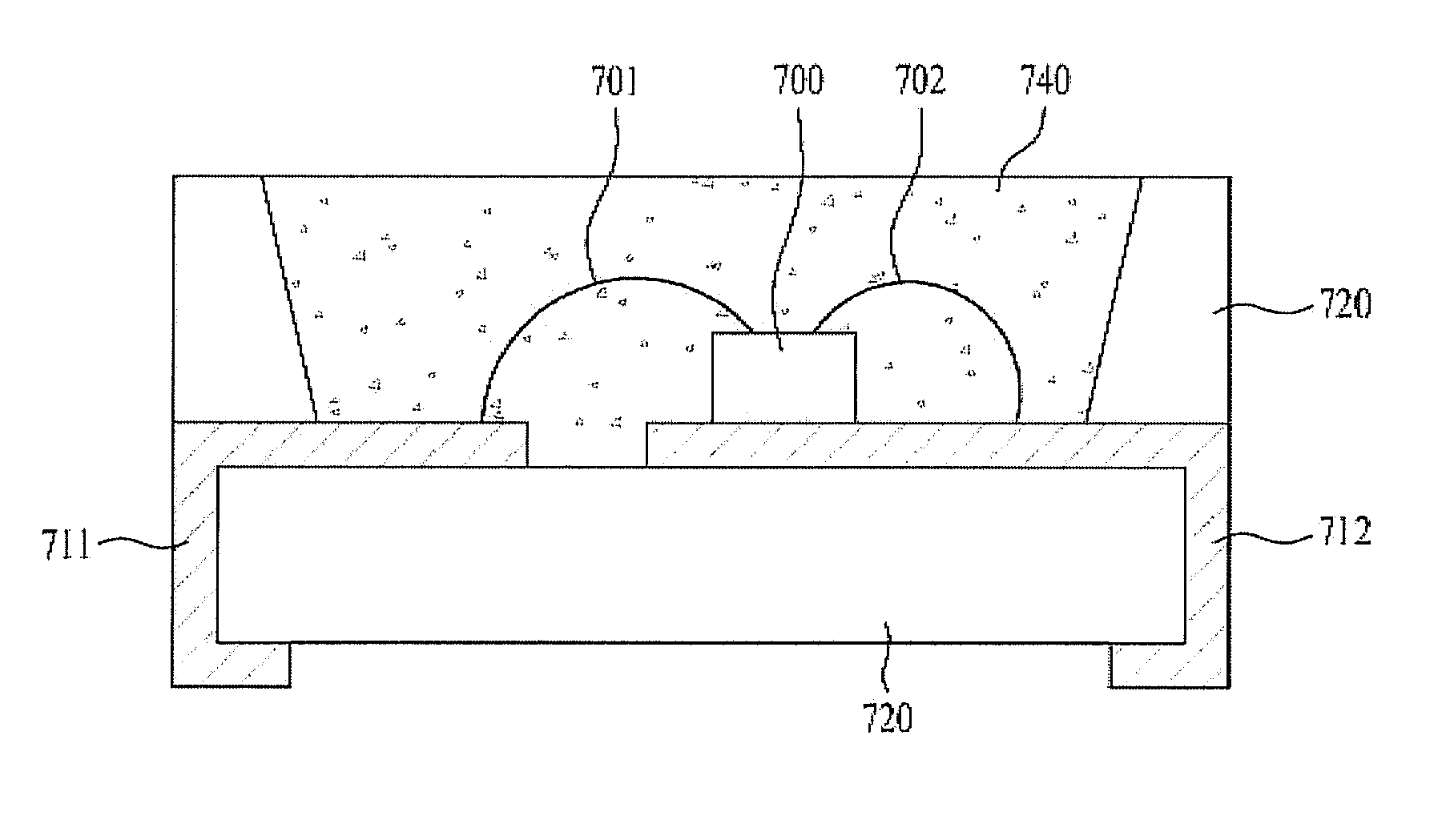

Light emitting device

ActiveUS20120138957A1Reduce lattice mismatchEnhancing stability and reliabilitySolid-state devicesSemiconductor/solid-state device manufacturingPhotochemistryMaterials science

Embodiments disclose a light emitting device including a substrate, a buffer layer disposed on an R-plane of the substrate, the buffer layer having a rock salt structured nitride, and a light emitting structure arranged on the buffer layer, the light emitting structure being grown in an a-plane.

Owner:SUZHOU LEKIN SEMICON CO LTD

Preparation of AlN growth face composite substrate and nitride semiconductor device

InactiveCN101503826AGood opticsReduce lattice mismatchPolycrystalline material growthSemiconductor/solid-state device manufacturingComposite substrateTransition layer

The invention discloses a preparation method for an AlN growth face composite substrate and a nitride semiconductor device, relates to a nitride semiconductor material, and provides a preparation method f an AlN growth face composite substrate for growing the nitride semiconductor material and a nitride semiconductor device. An AlN epitaxial layer grows on a substrate to obtain the AlN growth face composite substrate. The nitride semiconductor device is provided with the AlN growth face composite substrate, a transition layer and a nitride semiconductor device structural material layer. The transition layer grows on the AlN growth face composite substrate and consists of a nitride material AlxInyGa(1-x-y)N(x is more than 0 and less than or equal to 1, and y is more than or equal to 0 and less than or equal to 1.) containing Al. The nitride semiconductor device structural material layer grows on the transition layer, comprises an n-shaped layer, luminescent and absorbing functional structural layers and a p-shaped layer, and contains the component of the AlxInyGa(1-x-y)N(x is more than 0 or equal to and less than or equal to 1, and y is more than or equal to 0 and less than or equal to 1.).

Owner:XIAMEN UNIV

Silicon-based micro LED chip and manufacturing method thereof

PendingCN110854154AAvoid destructionImprove yieldSolid-state devicesSemiconductor devicesEngineeringGallium nitride

The invention discloses a silicon-based micro LED chip and a manufacturing method thereof. The chip comprises a silicon substrate, a plurality of light emitting structures, cutting grooves and an organic insulating layer, wherein the cutting grooves are formed among the light emitting structures. The chip is advantaged in that the silicon substrate is adopted to replace a sapphire substrate, so damage to a gallium nitride material and a micro LED chip caused by N2 generated by decomposition after gallium nitride absorbs laser during laser stripping of the sapphire substrate is avoided, the silicon substrate is removed through a physical grinding and chemical corrosion two-step method, the light emitting structure can be protected against damage while the silicon substrate is effectively removed, and the removal yield and reliability of the substrate are improved.

Owner:FOSHAN NATIONSTAR SEMICON