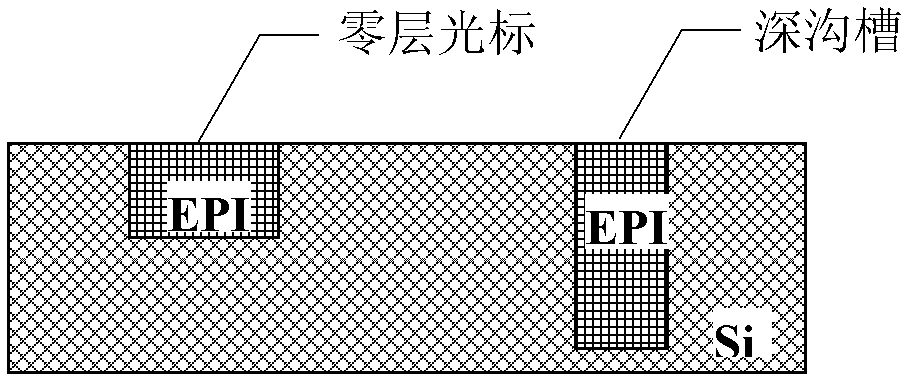

Method for producing zero layer photoetching marking of high-voltage device without barrier layers

A technology of zero-layer lithographic marking and high-voltage devices, which is applied in the field of semiconductor technology, can solve problems such as unusable, unrecognizable, and affecting the smooth process flow, so as to ensure the process flow, improve the yield rate, and ensure the smooth effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0035] The present invention makes the method for the zero-layer lithography mark of the high-voltage device without barrier layer, comprises the following steps:

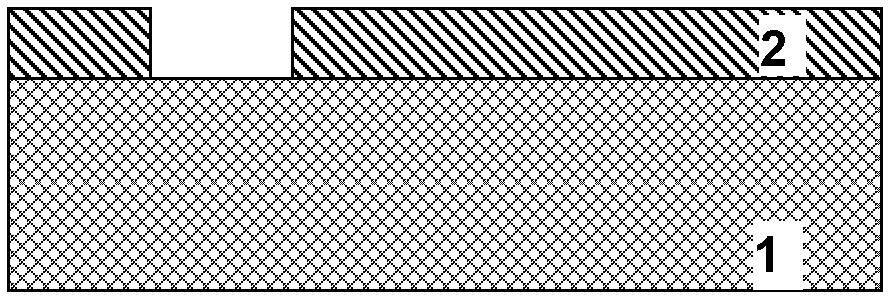

[0036] The first step, in the figure 2 A layer of photoresist 2 is formed on the silicon substrate 1 shown, and exposure and development are carried out on the silicon substrate 1, as image 3 Shown; Then etch out the zero-layer photolithography mark groove on the silicon substrate 1, as Figure 4 As shown; the depth of the zero-layer lithographic marking groove is 0.1-10 microns, the width is 1-10 microns, and the length is 1-10 microns; the shape of the groove can be vertical or inclined;

[0037] The size of the zero-layer lithography marking groove is preferably: 0.5-5 microns in depth, 1-6 microns in width, and 1-10 microns in length;

[0038] In the second step, the photoresist 2 on the silicon substrate 1 is removed, such as Figure 5 Shown; Then a layer of dielectric layer 3 is deposited on the silicon ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| depth | aaaaa | aaaaa |

| width | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More