Trimming resistor and preparation method thereof

A technology for trimming resistors and manufacturing methods, which is applied in semiconductor/solid-state device manufacturing, circuits, electrical components, etc. It can solve problems such as trimming failure, insufficient trimming, and increased test condition debugging, and achieves small and easy fusing areas. Trimming and solving the effect of excessive trimming

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0079] See attached Figure 5 , combined with Figures 6 to 14 The process of the manufacturing method of the trimming resistor whose curved shape is a corner provided by the present invention is described in detail.

[0080] S1: Provide a semiconductor substrate, and fabricate a dielectric layer on the semiconductor substrate.

[0081] see Figure 6 , a semiconductor substrate 30 is provided, and a dielectric layer 31 is formed on the semiconductor substrate 30 .

[0082] Wherein, the semiconductor substrate 30 may be a silicon substrate, a silicon germanium substrate, a III-V group element compound substrate or other semiconductor material substrates known to those skilled in the art, and a silicon substrate is used in this embodiment. . More specifically, a MOS field effect silicon-containing material or a silicon compound may be formed in the semiconductor substrate 30 used in this embodiment. The semiconductor substrate provided for bipolar circuits is usually a P(11...

Embodiment 2

[0108] See attached Figure 5 , combined with Figures 16 to 26 The process of the manufacturing method of the trimming resistor whose bending shape is arc-shaped provided by the present invention is described in detail.

[0109] Step S1 in the present embodiment (referring to appended Figure 16 ) and step S2 (see attached Figure 17 ) Please refer to the content in steps S1 and S2 in the first embodiment, and details will not be repeated here.

[0110] The difference between this embodiment and the first embodiment lies in the difference between step S3 and step S4. The specific difference of step S3 is as follows:

[0111] see Figure 18 and Figure 19 , Figure 19 for Figure 18 In the top view of the front, the curved shape made in the area where the fuse is not removed has at least one arc 32a, so that the trimming structure with changing current density is formed, and the arc is made to have a radian θ is a circular or elliptical arc of 1-359 degrees, preferabl...

Embodiment 3

[0124] See attached Figure 5 , combined with Figures 27 to 32 The process of the manufacturing method of the trimming resistor with a curved shape having steps provided by the present invention will be described in detail.

[0125] Step S1 in the present embodiment (referring to appended Figure 27 ) Please refer to the content in step S1 in the first embodiment, which will not be repeated here.

[0126] The difference between this embodiment and the first embodiment lies in the difference of step S2, step S3 and step S4. The specific differences of step S2 are as follows:

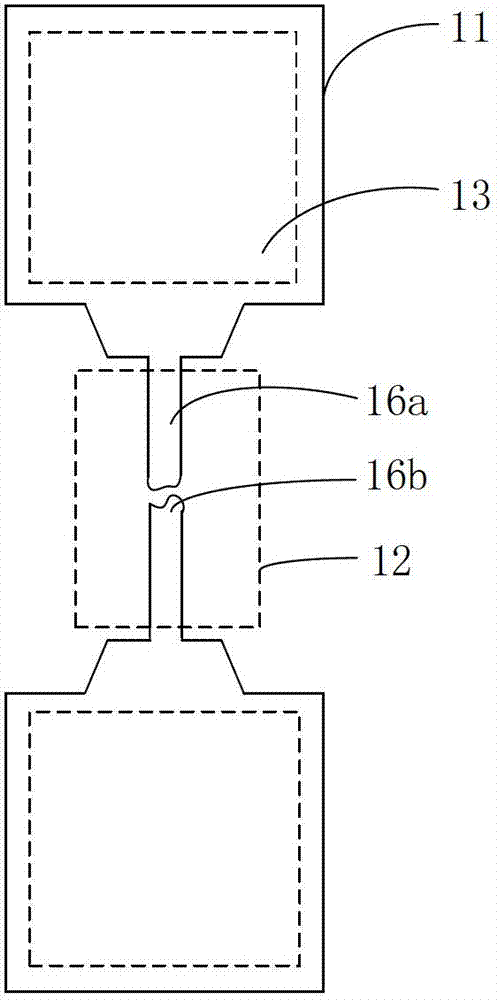

[0127] see Figure 28 , before depositing the fuse 32, carry out processes such as photolithography and etching on the dielectric layer 31, and the etching stays in the dielectric layer 31, so that the dielectric layer 31 forms a shape with at least one step 31a, and The step height and the number of steps required by the dielectric layer 31 can be determined, and the number of steps 31a can be one,...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Radian | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More