Patents

Literature

45results about How to "Reduce Reliability Risk" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

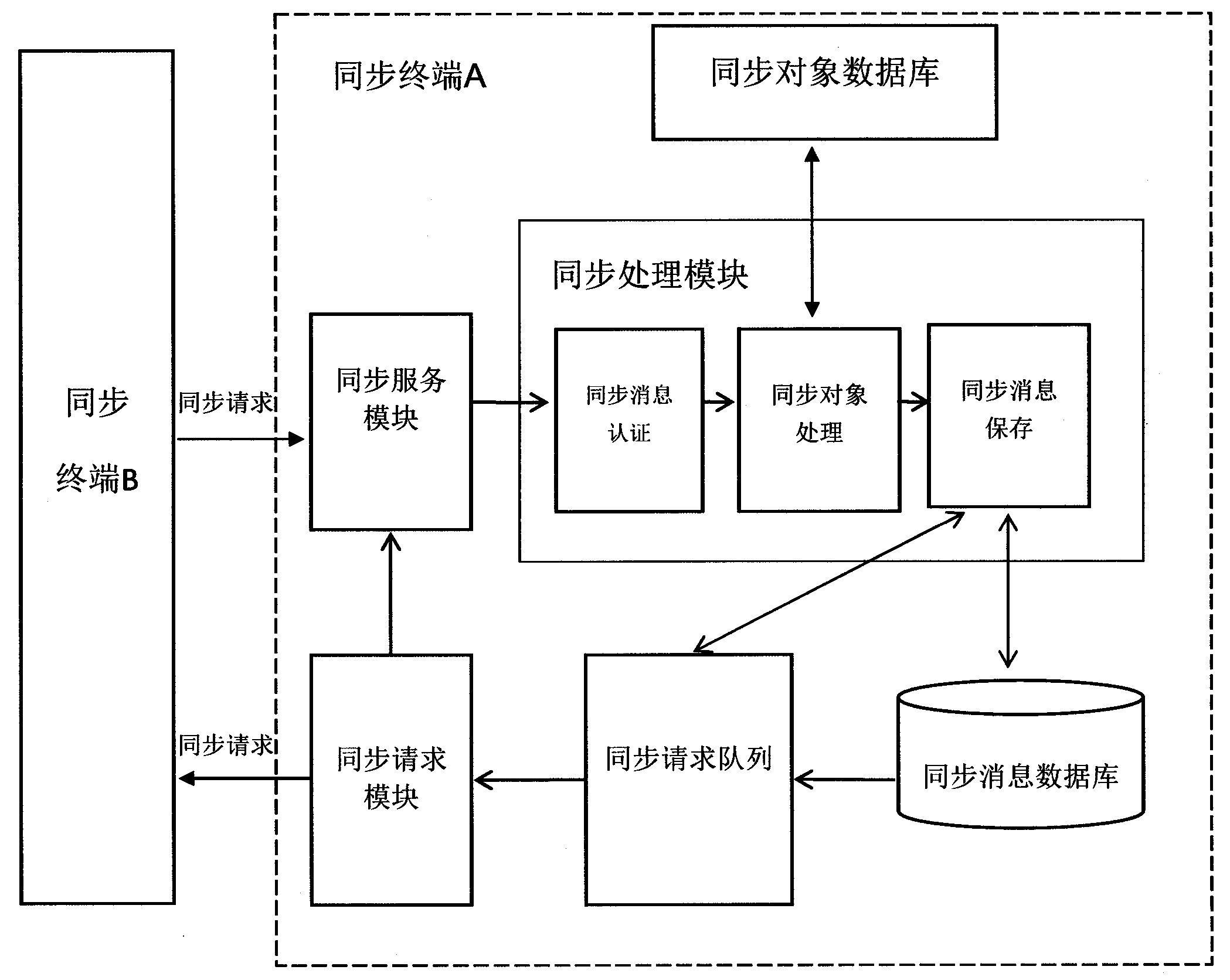

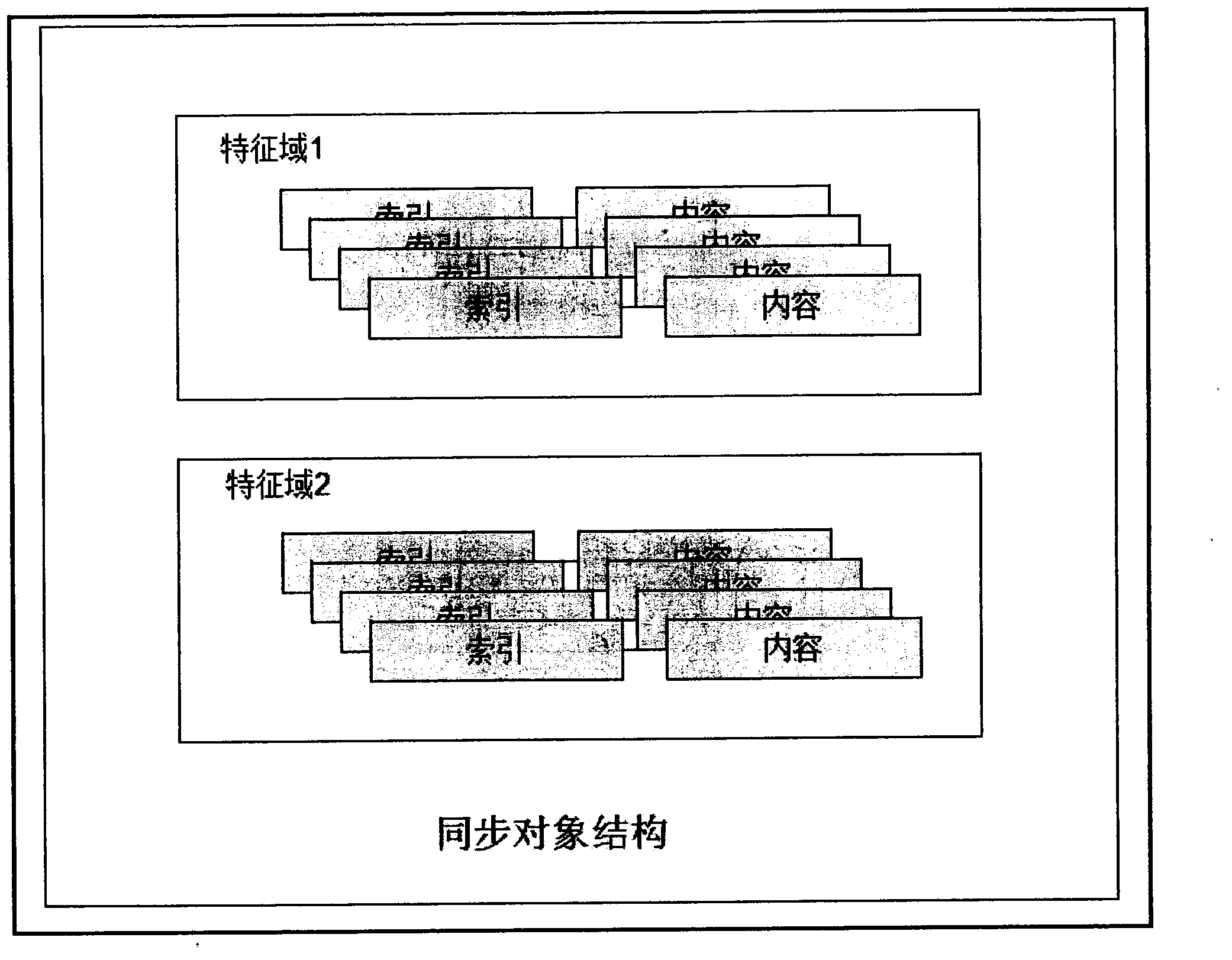

Distributed multi-point synchronization system and synchronization method thereof

InactiveCN104052768ASave bandwidth and storage costsReduce reliability and security risksTransmissionTime informationDistributed computing

The invention discloses a distributed multi-point synchronization system and a synchronization method thereof. The system is formed by more than two distributed synchronous terminals including synchronized object databases, synchronous message databases, synchronous processing modules, synchronous request modules and synchronized service modules. According to the system and the method, real-time information content synchronization among a plurality of user terminals in a network can be realized without the need to use a center server. The user terminals carry out direct communication and synchronous content exchanging by a synchronous protocol and there is no need for the synchronous server to carry out content transferring and distribution, thereby substantially improving reliability and security of the system.

Owner:彭涛

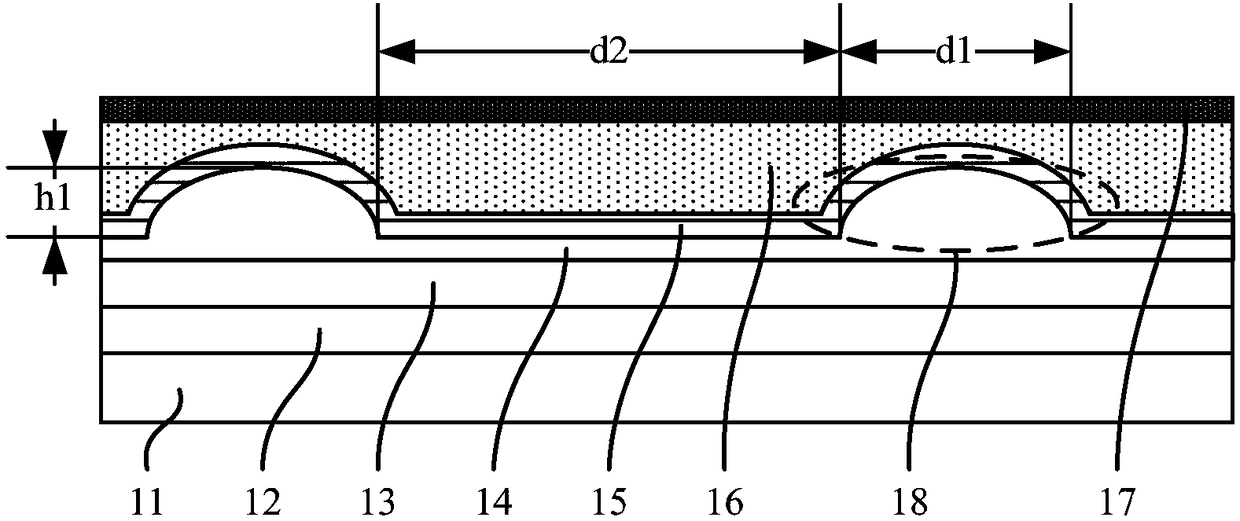

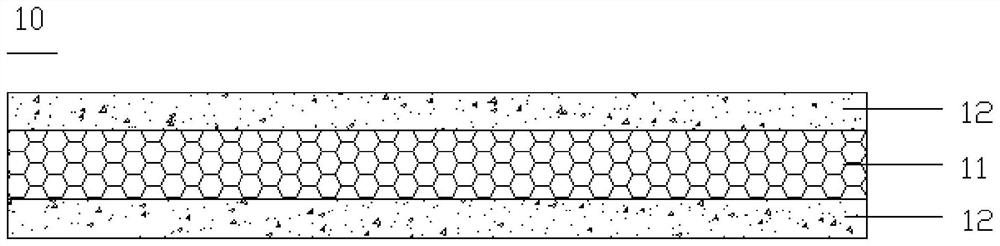

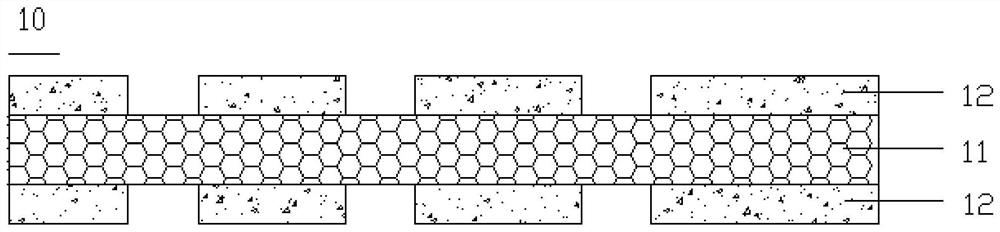

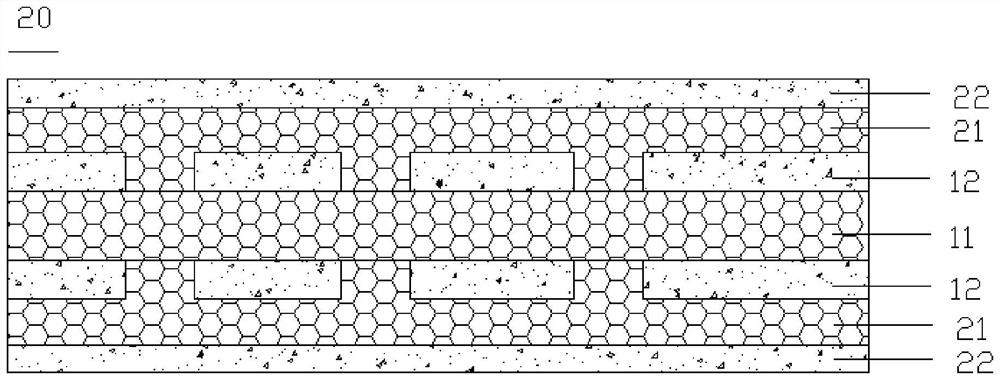

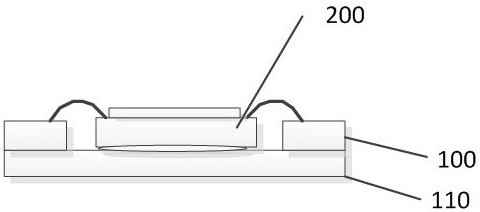

Cover plate, forming method thereof, cover plate mother board and electronic equipment

InactiveCN109239815AReduce usageImprove performanceSemiconductor/solid-state device manufacturingOptical elementsGlass coverTransmittance

The invention discloses a cover plate, a forming method thereof, a cover plate mother board and electronic equipment. The forming method of the cover plate comprises the following steps: providing a mother board base, wherein the mother board base comprises a base layer and a sacrificial layer positioned on the base layer; carrying out schematization on the sacrificial layer to form a graphic sacrificial layer; and by using the graphic sacrificial layer as a mask, etching the base layer to form a substrate and a texture bulging the substrate. The substrate and the texture are formed by etchingthe base layer, compared with a glass cover plate comprising a UV glue material graphic layer, the application of the UV glue material graphic layer is omitted, the problems caused by the UV glue material graphic layer and a forming technology thereof can be avoided effectively, the performance, reliability and manufacturing yield of the formed cover plate are improved, the structure of the coverplate is simplified, the light transmittance of the cover plate is improved, and the performance and aesthetic degree of the formed electronic equipment are improved.

Owner:SHANGHAI OXI TECH

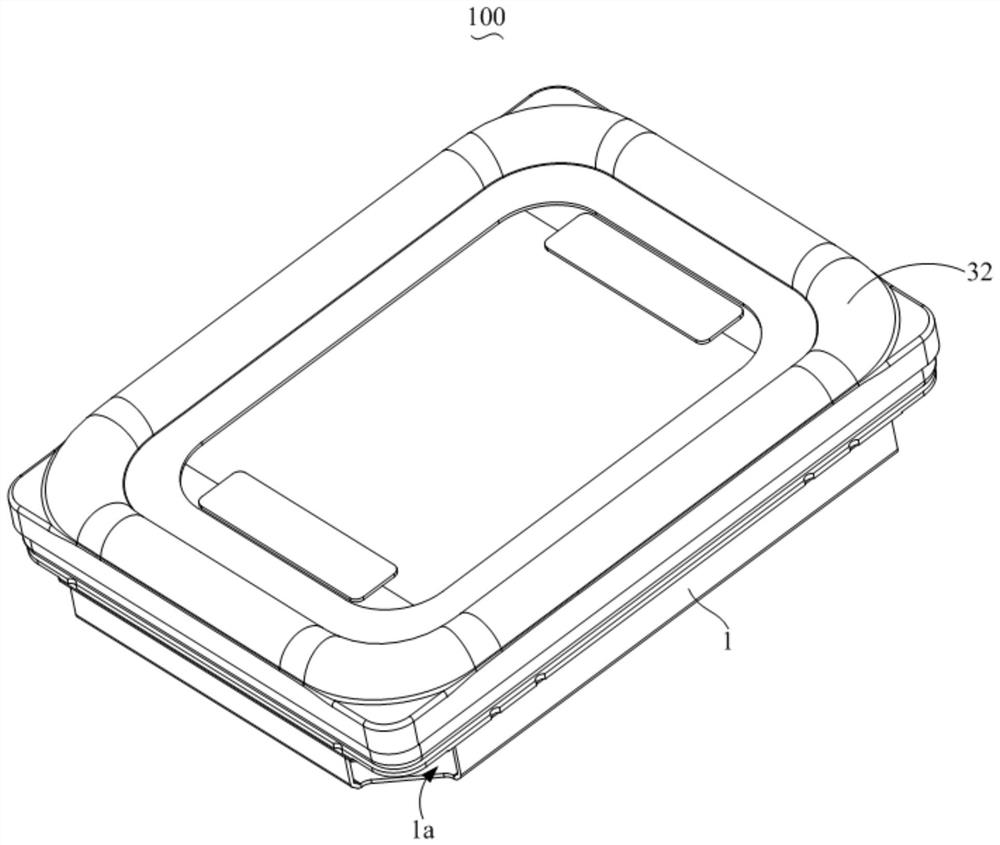

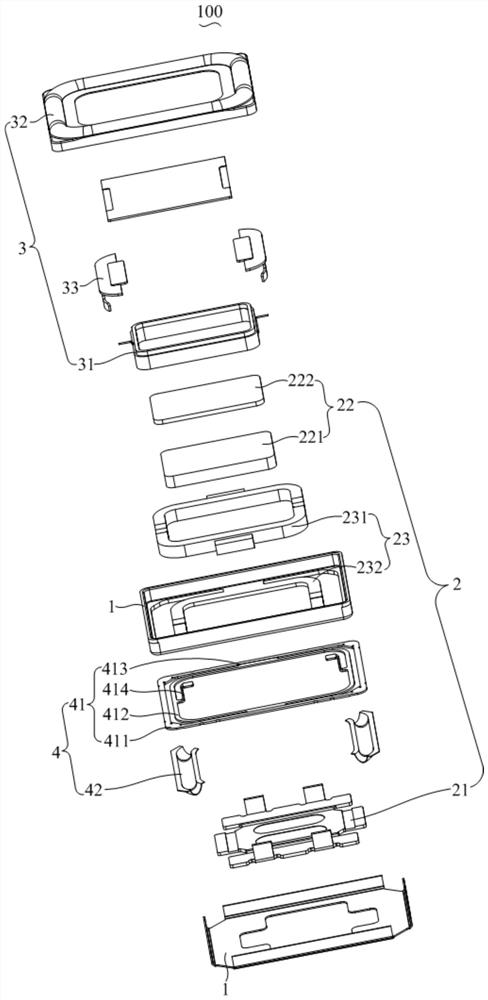

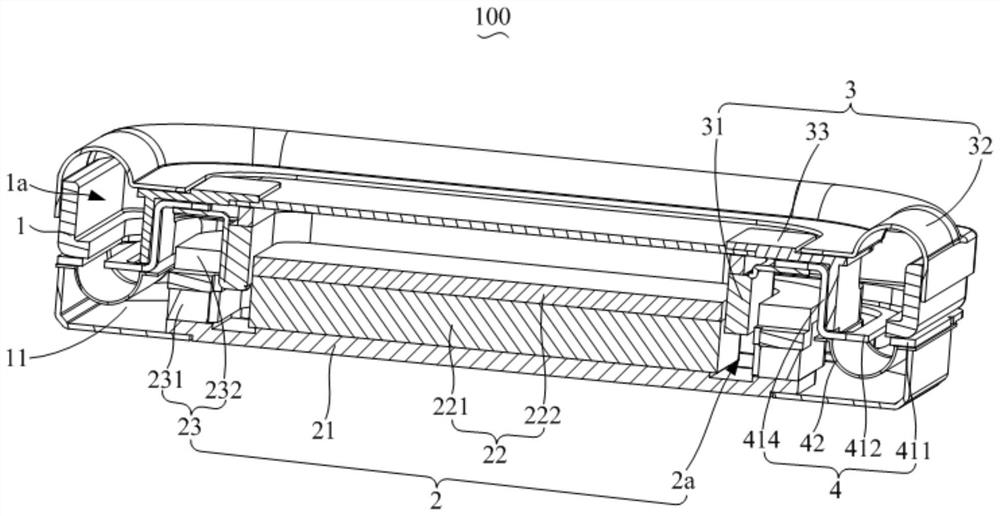

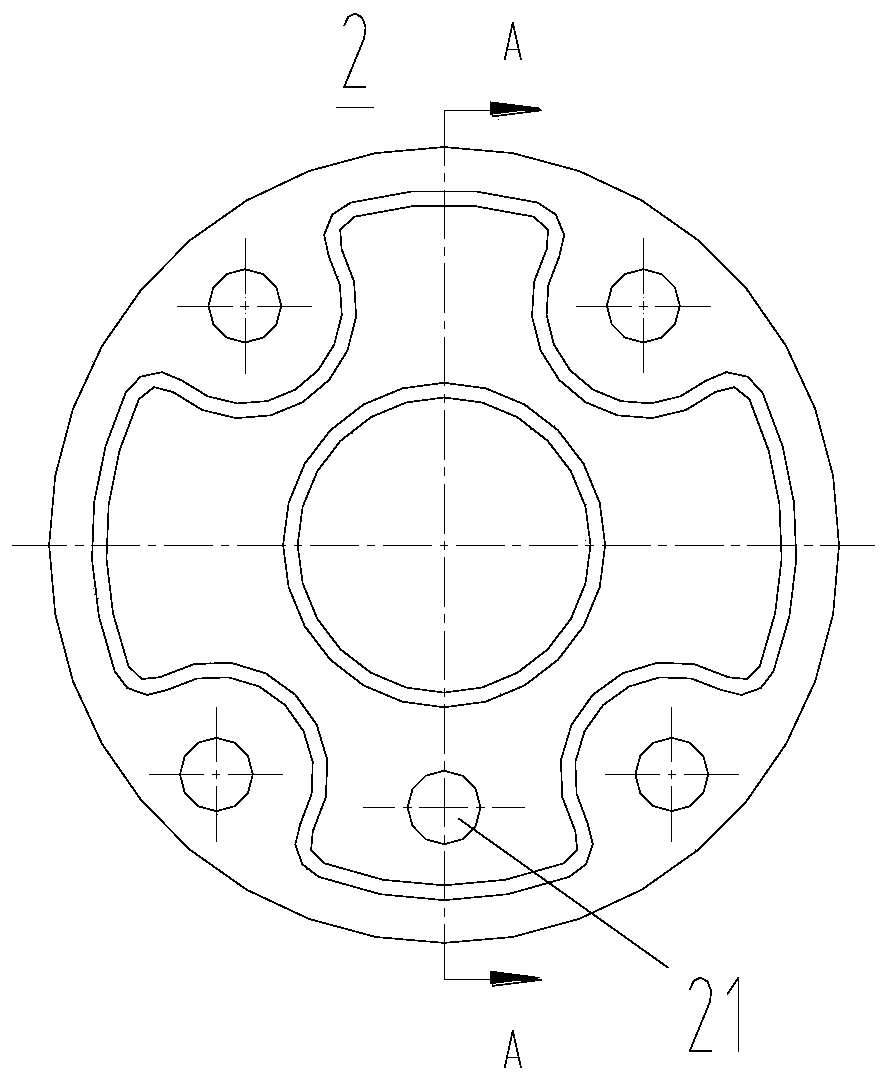

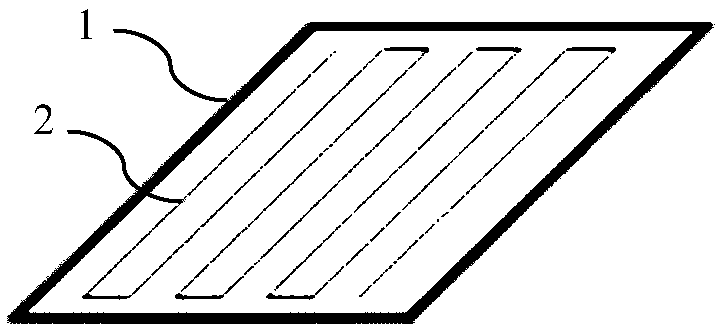

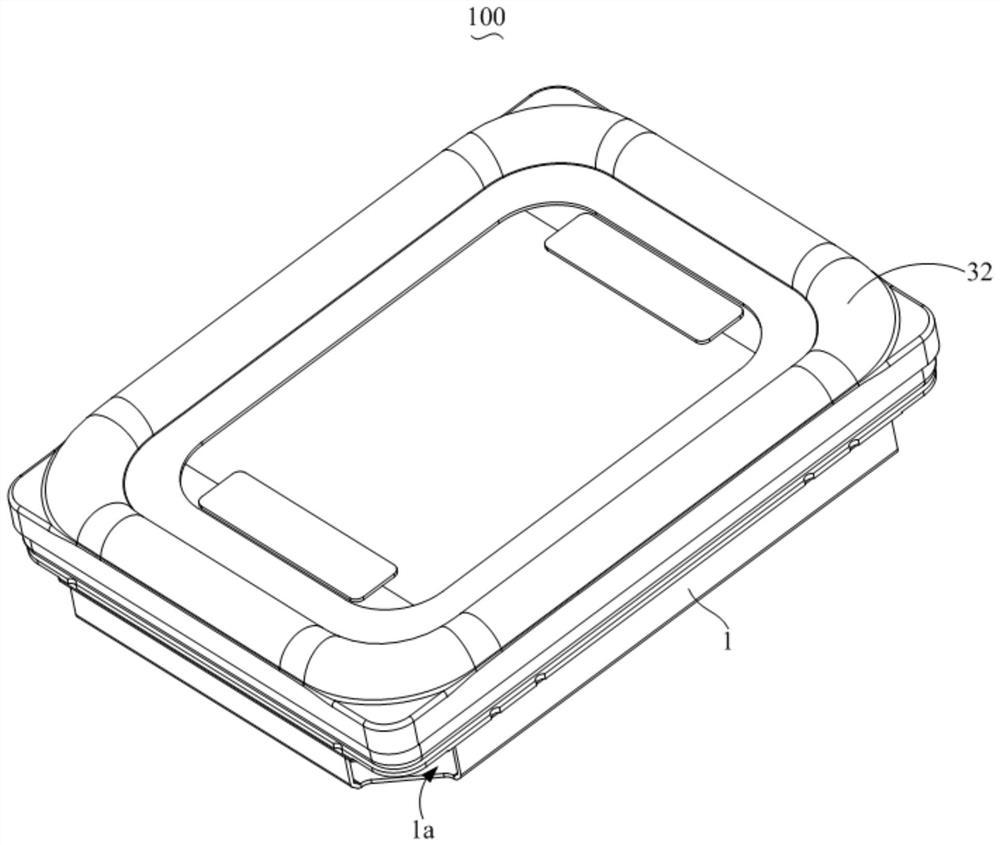

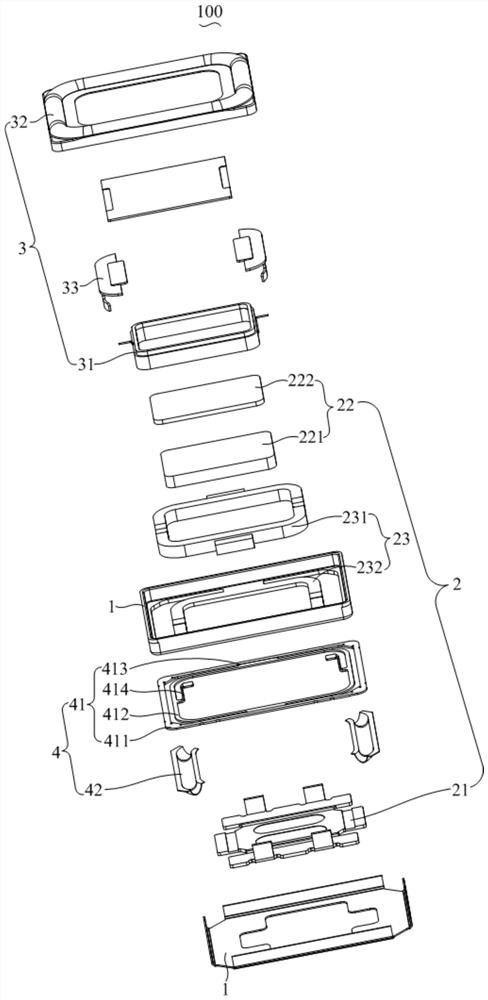

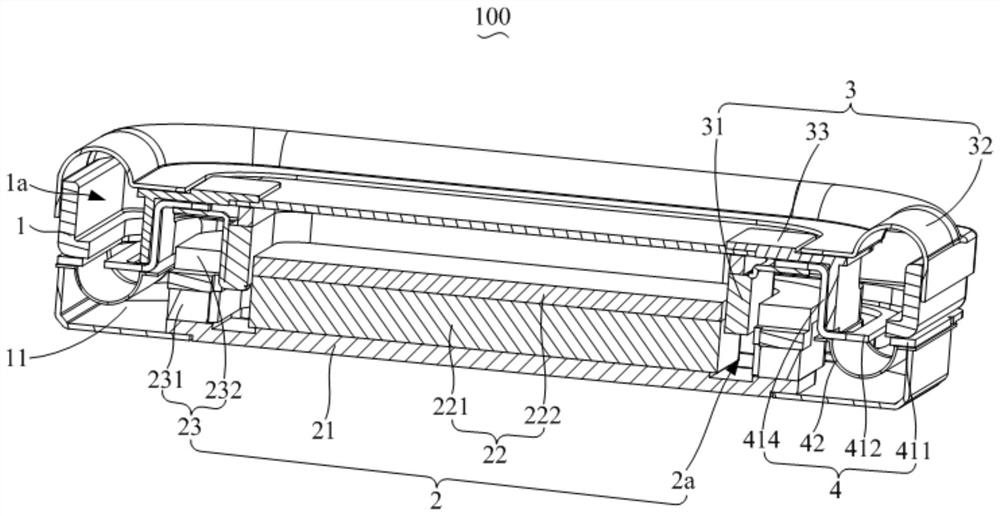

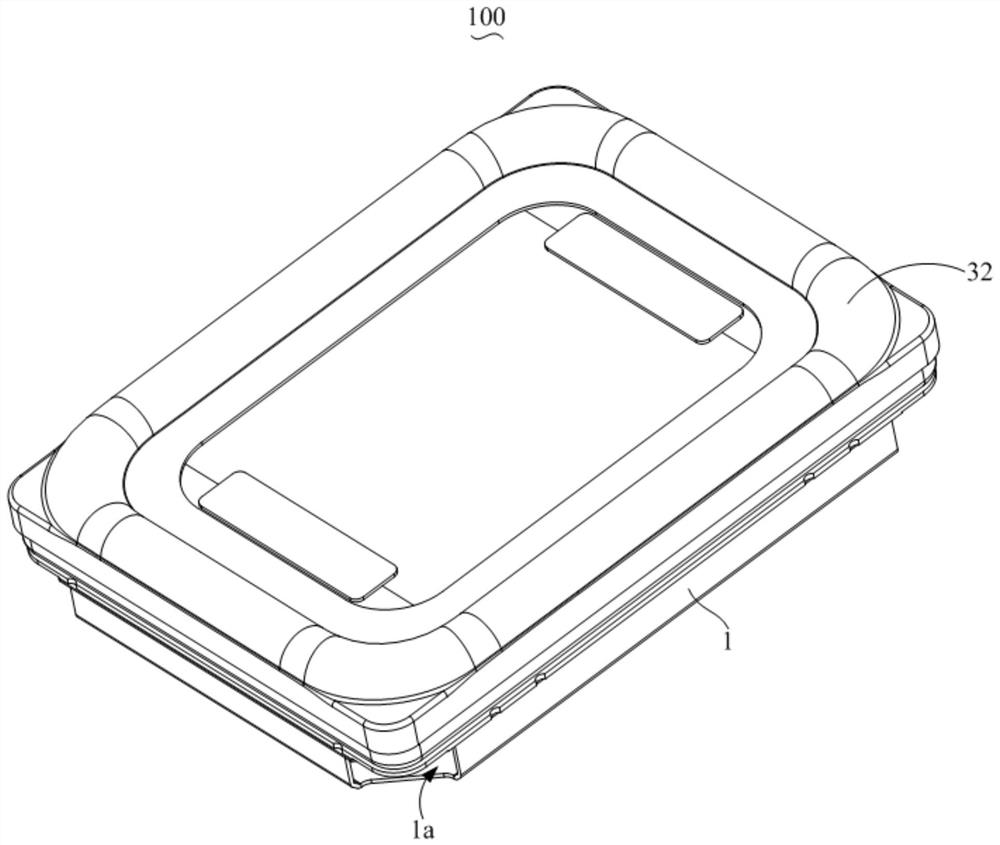

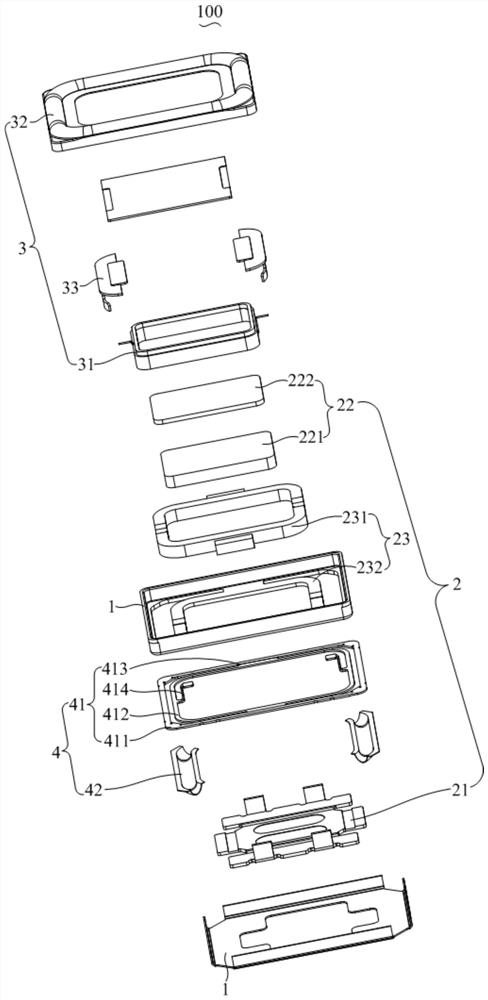

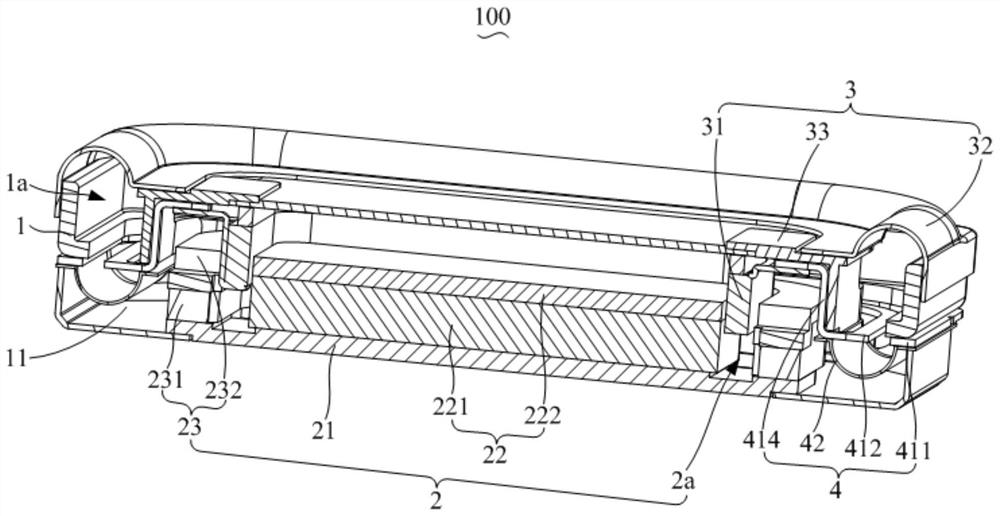

Loudspeaker unit and electronic terminal

ActiveCN111901714AImprove installation stabilityAvoid resonance or oscillationLoudspeaker transducer fixingLoudspeaker casing supportsLoudspeakerEngineering

The invention discloses a loudspeaker unit and an electronic terminal, the loudspeaker unit comprises a shell assembly, a magnetic circuit system, a vibration system and a balance assembly, the balance assembly comprises a centering support chip, the centering support chip comprises an outer fixing part, an elastic support part and a connecting section, and the outer fixing part is annular; the elastic supporting part is annular and located on the inner side of the outer fixing part. The connecting section is located between the outer fixing part and the elastic support part and connected withthe outer fixing part and the elastic support part. The outer fixing part is connected with the shell assembly, the elastic support part is located in the gap and partially connected with a support of a vibration system, and the elastic support part elastically deforms along with vibration of a support. The invention aims to provide the loudspeaker unit which can effectively prevent a bending part of the centering support chip from being easily broken, so that the loudspeaker unitcan effectively reduce the product reliability risk.

Owner:GOERTEK INC

Preparation method of silicon carbide power diode device

ActiveCN112038398AIntegrity guaranteedReduce Reliability RiskSemiconductor/solid-state device manufacturingSemiconductor devicesPhysicsCarbide silicon

The invention relates to a preparation method of a silicon carbide power diode device. The preparation method comprises the following steps: growing a SiC epitaxial layer with an N type active regionon a first surface of a SiC substrate; depositing a first barrier layer on the surface of the SiC epitaxial layer, opening an injection window in the N type active region through etching, and performing ion injection in the injection window of the N type active region; through high-temperature activation, forming P type regions arranged at intervals in the N type active region; and covering a first metal layer forming ohmic contact with the P type region with a second metal layer, so that the first metal layer is prevented from being corroded by a BOE solution in the process of removing the second barrier layer through wet etching, the integrity of the first metal layer is greatly guaranteed, the problem that metal particles contaminate a device is avoided, the reliability risk caused by metal particle contamination is reduced, and the device manufacturing yield is greatly improved.

Owner:XIAMEN SANAN INTEGRATED CIRCUIT

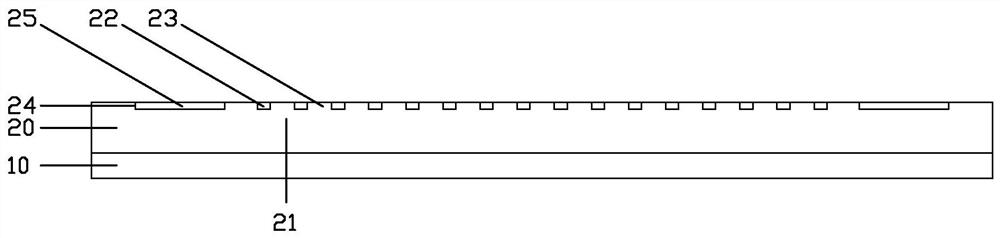

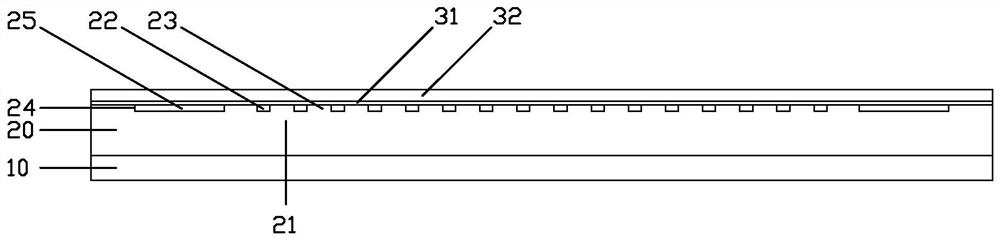

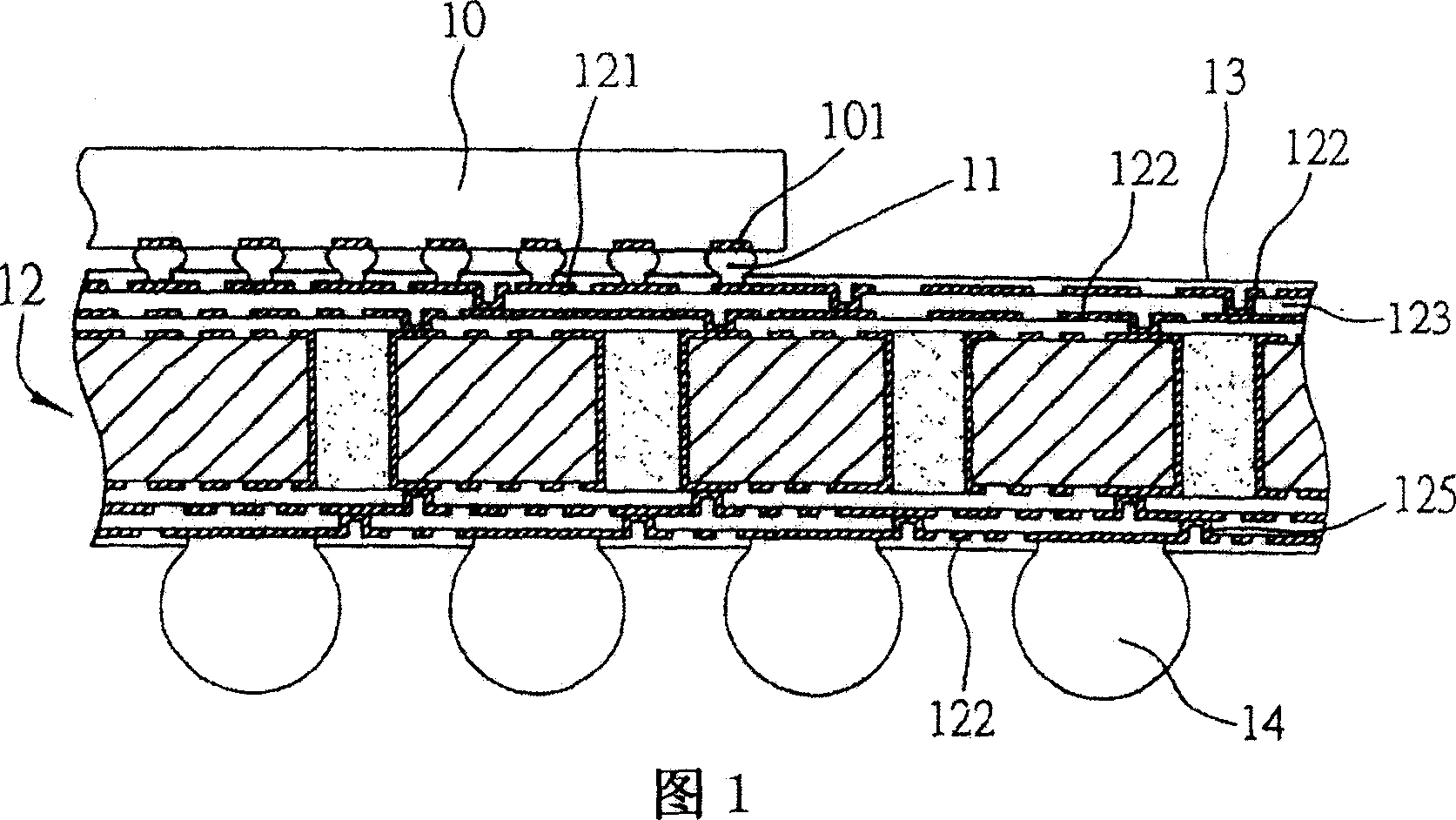

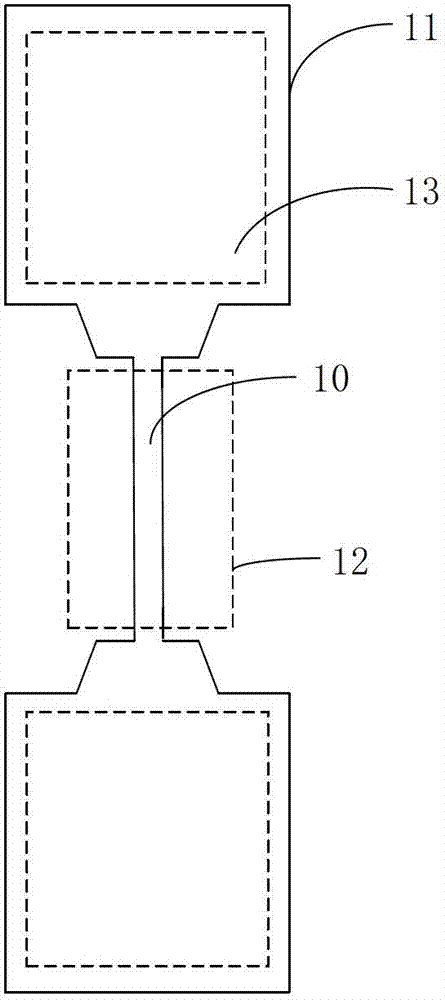

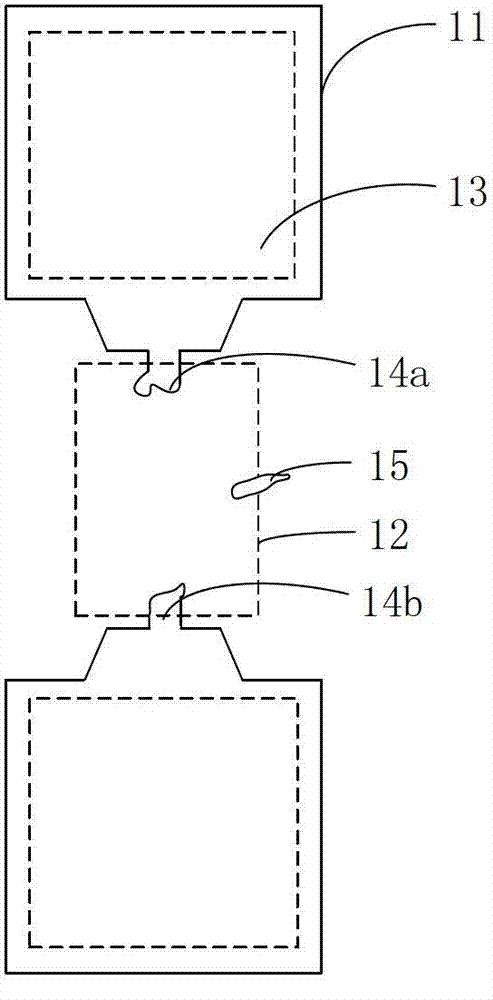

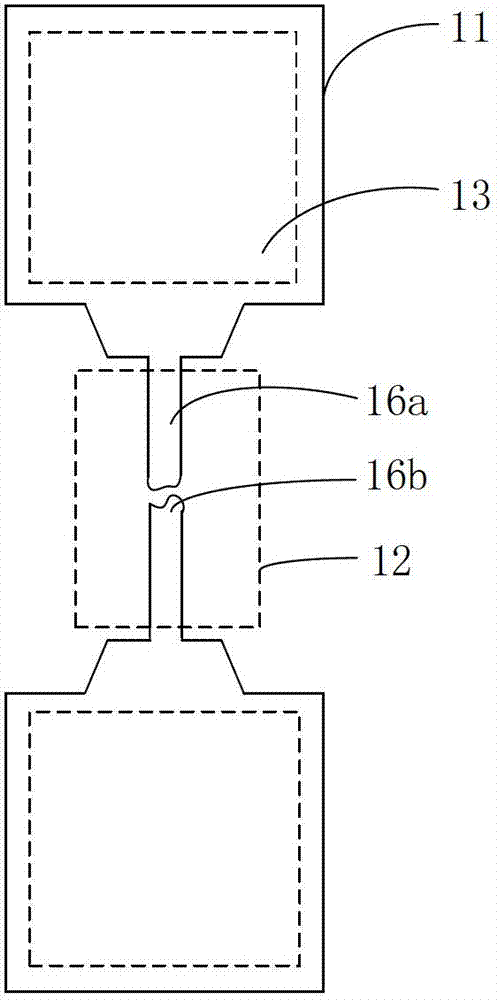

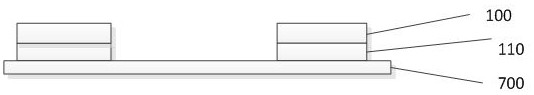

Carrying structure for electron element

ActiveCN1925152ASolve complexitySolve the costSemiconductor/solid-state device detailsSolid-state devicesSemiconductor packageEngineering

This invention provides one electron element supportive structure, which comprises the following parts: at least one supportive board with at least one opening; at least one electron element with main interface and non active surface set in the opening of supportive board and at least one adhesive layer for form supportive board surface, wherein, the adhesive layer part is filled into gap between opening and electron element to fix the electron element into the opening holes.

Owner:PHOENIX PRECISION TECH CORP

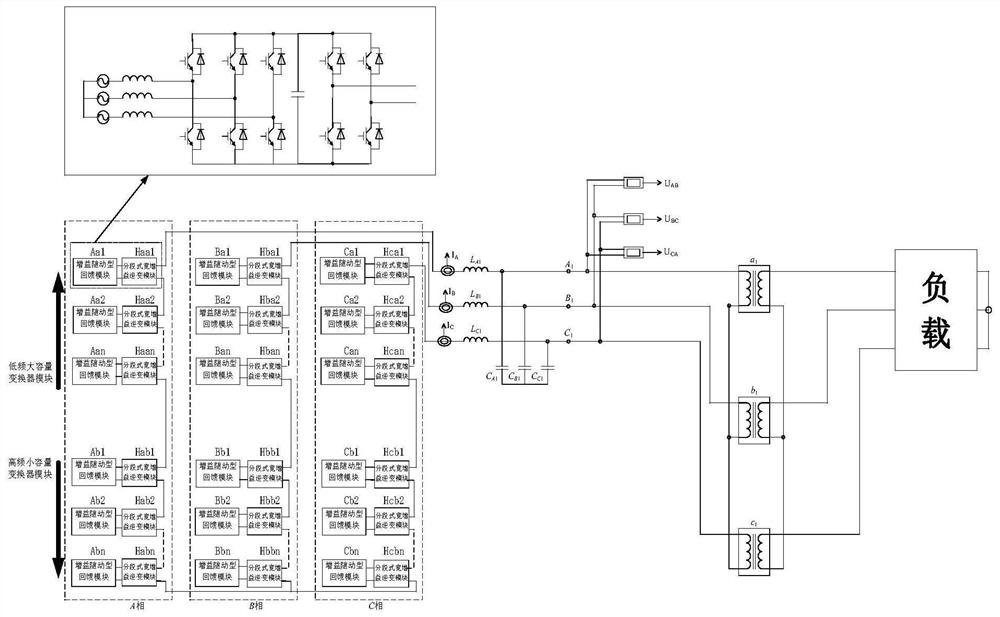

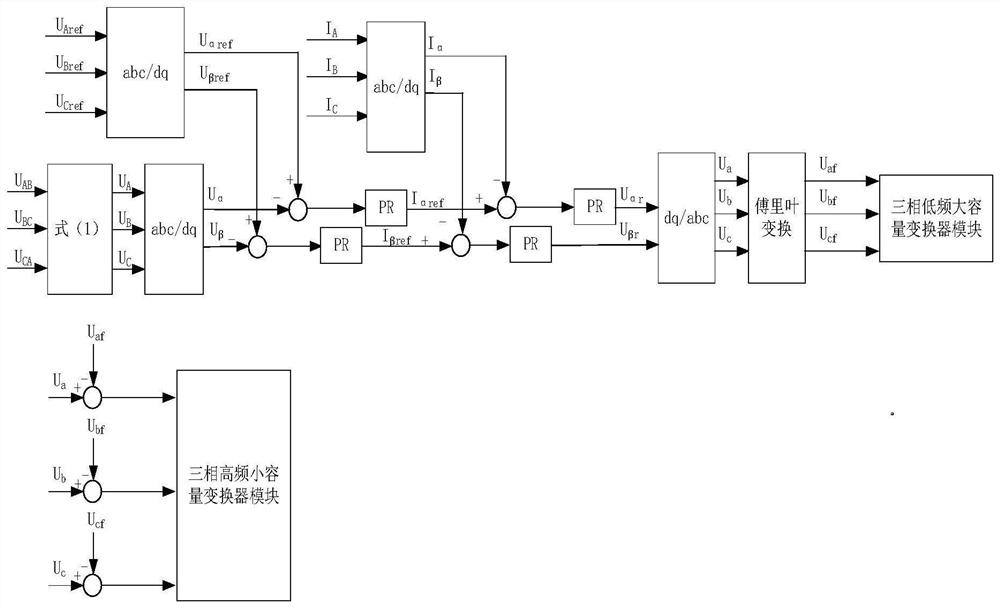

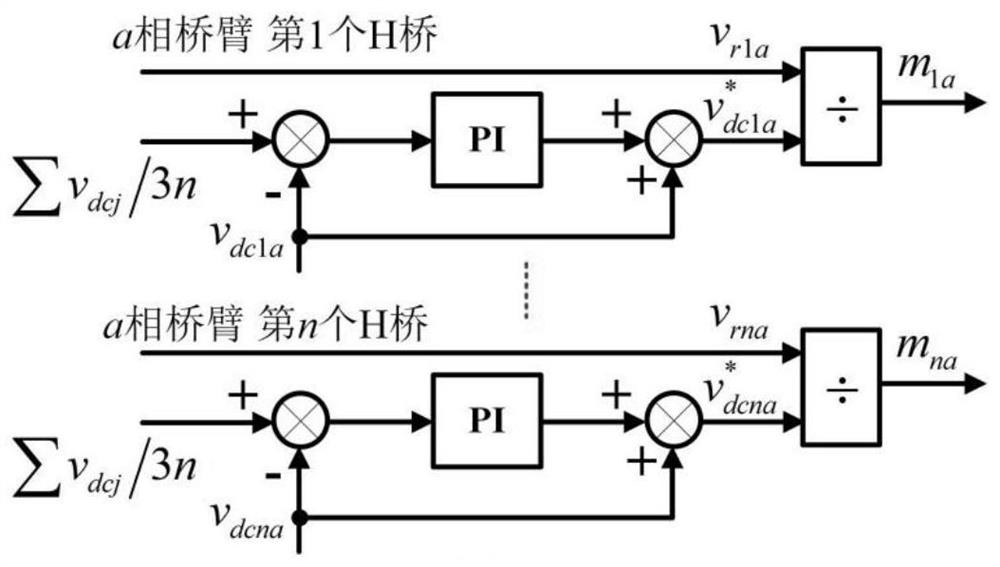

Power grid simulator topological structure and control method thereof

ActiveCN112886828AAvoid bottlenecksLow costConversion with intermediate conversion to dcFault location by conductor typesTransformerHarmonic control

The invention discloses a power grid simulator topological structure and a control method thereof. The topological structure comprises an A phase, a B phase, a C phase, an A phase LC filter, a B phase LC filter and a C phase LC filter, an A phase transformer, a B phase transformer and a C phase transformer and a load, wherein the A phase, the B phase and the C phase are identical in structure. A simulator can operate in a four-quadrant mode, feedback of electric energy to a power grid is achieved, three-phase power grid voltage output can be provided, and various power grid fault conditions such as voltage drop, frequency deviation, three-phase imbalance and harmonic distortion of the power grid can be simulated. On the level of designing the controller, the control mode of the power grid simulator is divided into fundamental wave control and harmonic wave control, namely, a low-frequency large-capacity module and a high-frequency small-capacity module are controlled respectively. In addition, a direct current side voltage follow-up control strategy is provided to solve the problem of power mismatching among modules.

Owner:JIANGSU GOLDWIND SCI & TECH CO LTD +1

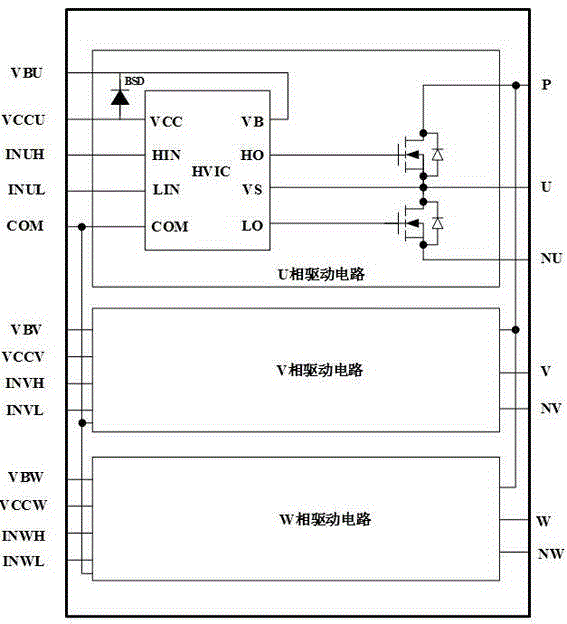

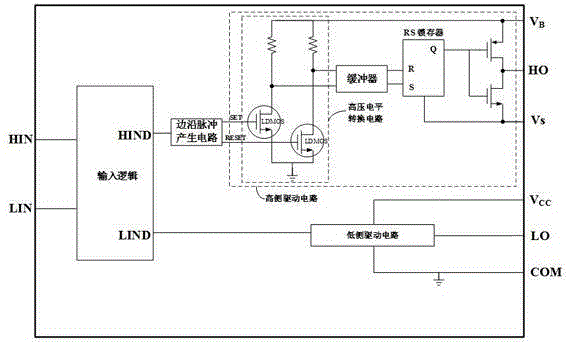

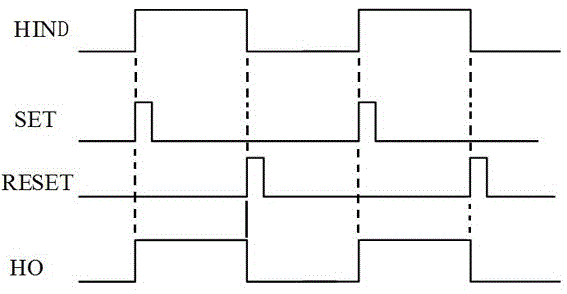

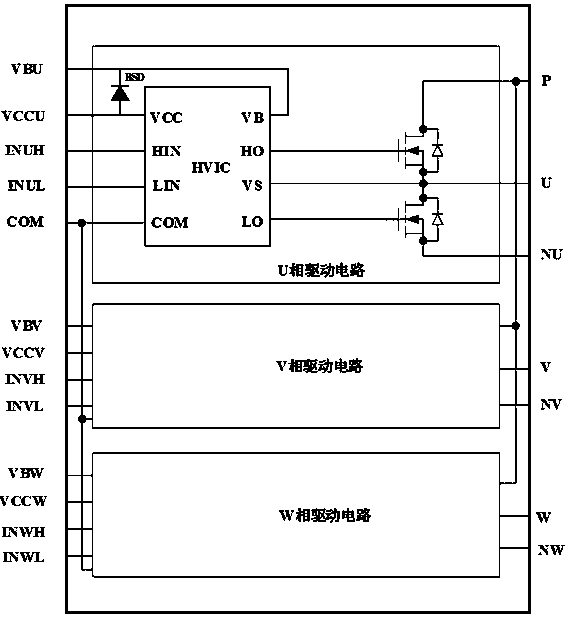

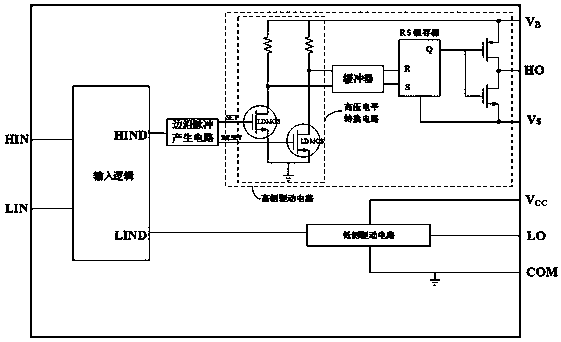

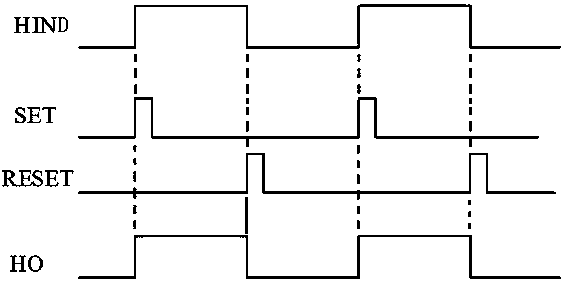

High-reliability edge pulse generating circuit of intelligent power module

ActiveCN105007062AReduce transmission delayGuaranteed normal outputElectric pulse generator circuitsMOSFETControl signal

The invention relates to a high-reliability edge pulse generating circuit of an intelligent power module. The high-reliability edge pulse generating circuit is designed based on a brand-new circuit design framework, and could be applied to high-side control signals with any pulse width. The high-reliability edge pulse generating circuit could ensure the normal output of a RESET pulse signal no matter the input signal has normal pulse width, or is a narrow pulse, even a super-narrow pulse so as to fundamentally solve the problem that a high-side output signal could not reset because of a narrow pulse input signal and reduce risk of straightway reliability of the MOSFET at the high side and the low side to effectively ensure the work stability of each module in the applied intelligent power module. And not only that, the high-reliability edge pulse generating circuit designed by the invention is simple in structure and overcomes the limitation of a traditional edge pulse generating circuit to input pulse width so as to save multi-level noise filter circuit in a signal transmission path, reduce the transmission delay of the signal and promote frequency of an operating switch.

Owner:豪威模拟集成电路(北京)有限公司

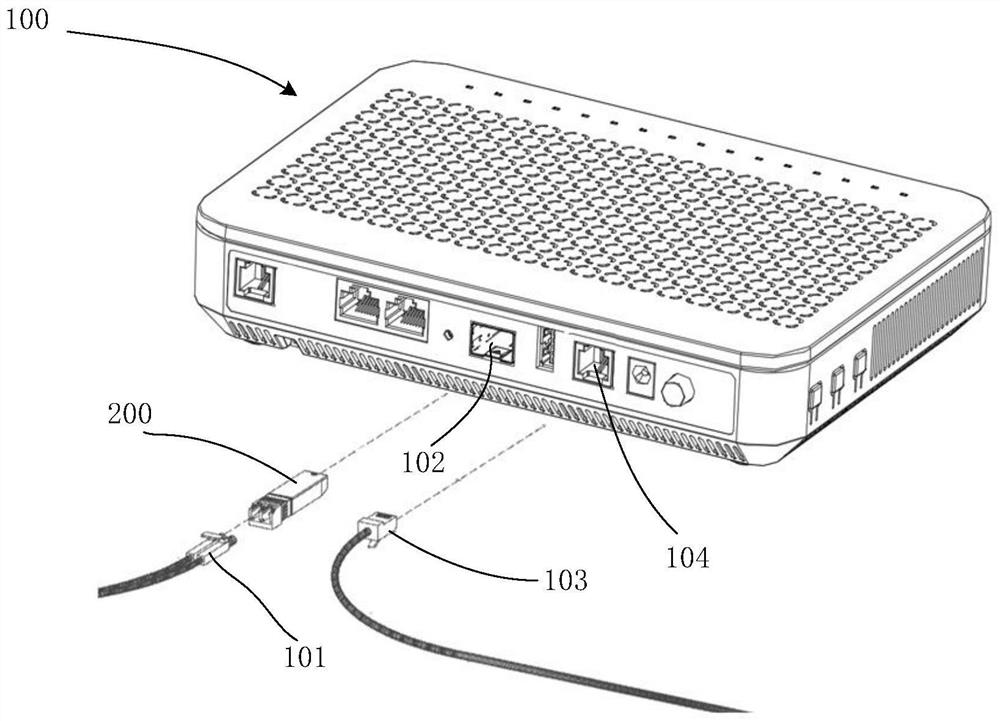

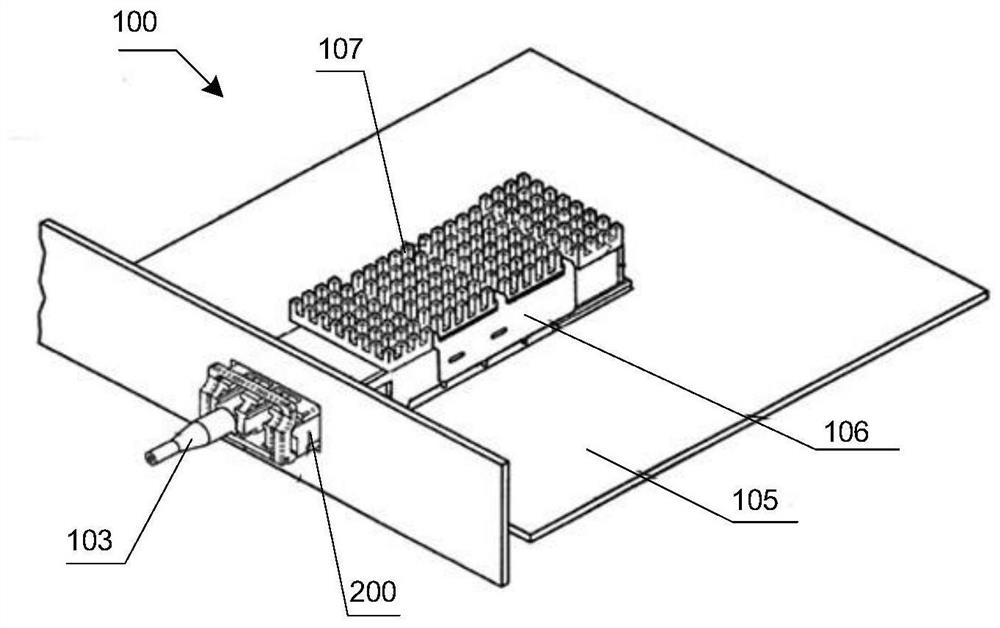

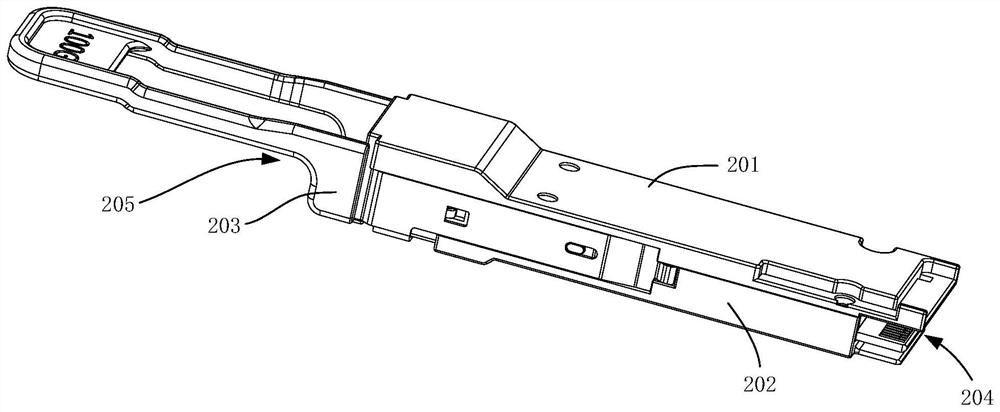

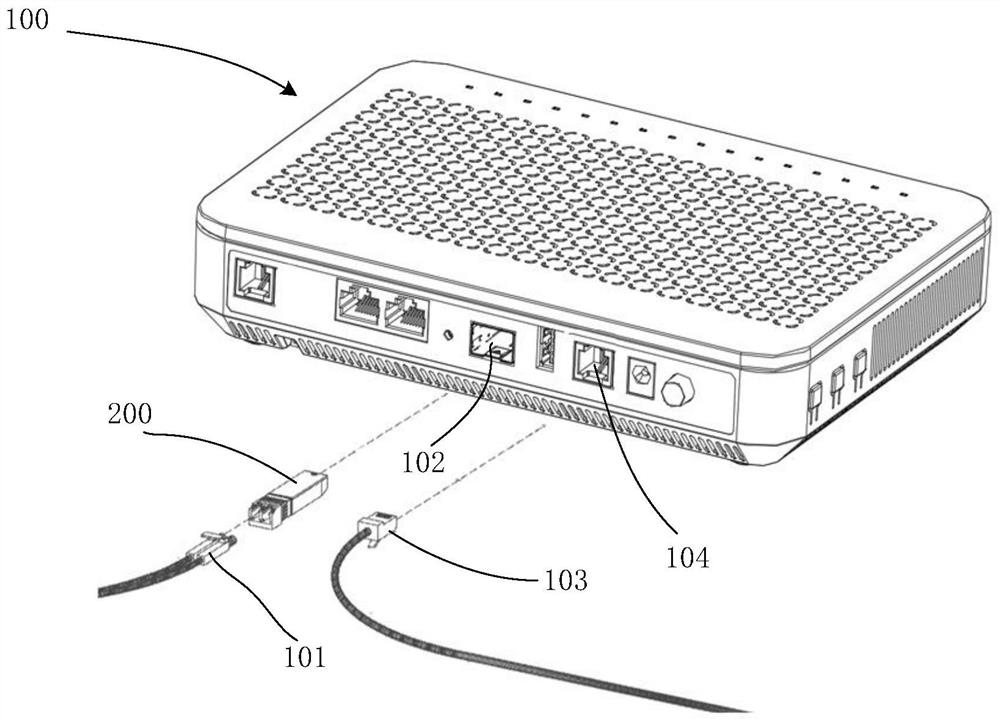

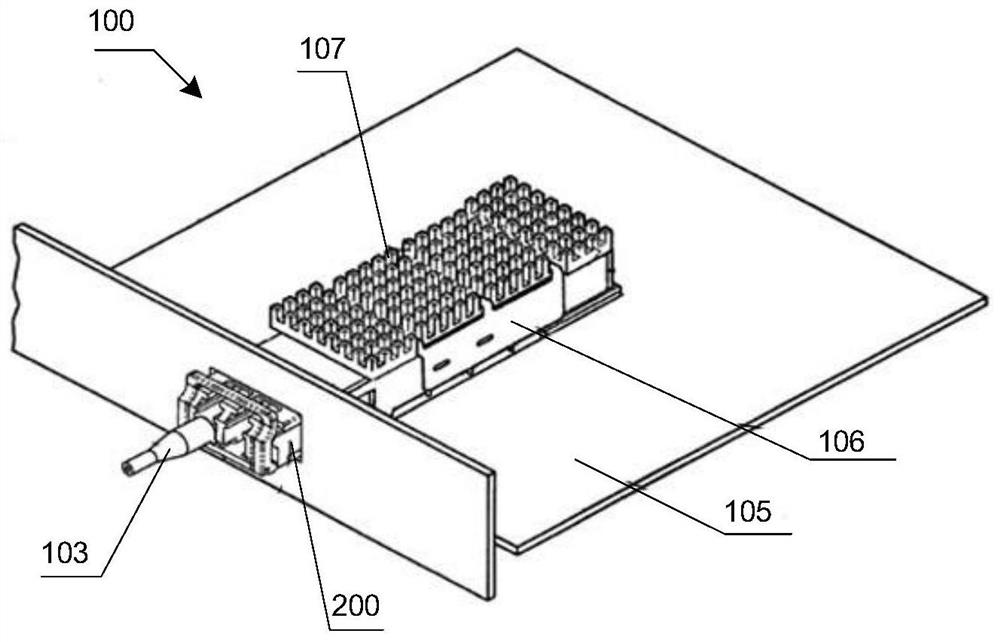

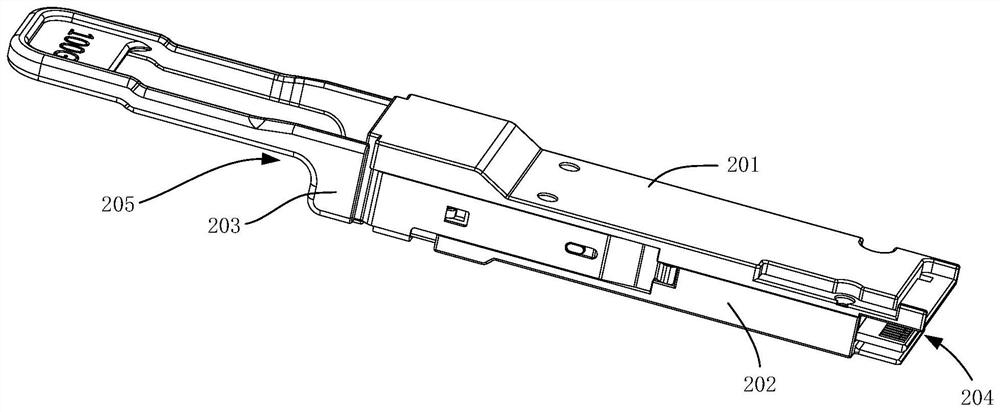

Optical module

ActiveCN112230350AHigh electromagnetic shieldingAchieve fixationCoupling light guidesOptical ModuleMechanical engineering

The invention discloses an optical module. The optical module comprises an upper shell, a lower shell, a circuit board, a lens assembly and a clamping jaw assembly, and the lens assembly is arranged at the end, close to an optical port of the optical module, of the circuit board; the clamping jaw assembly is arranged at the optical port of the optical module, one end of the clamping jaw assembly is directly connected with the lens assembly, and the other end of the clamping jaw assembly is connected with an external optical fiber; the clamping jaw assembly comprises a clamping jaw and a shielding plate connected with the clamping jaw, a first limiting piece is arranged on the lower shell, a second limiting piece is arranged on the clamping jaw, and the first limiting piece is embedded in the second limiting piece; and a first positioning piece is arranged in the first limiting piece, a second positioning piece is arranged on the side face, provided with the second limiting piece, of the clamping jaw, and the second positioning piece is inserted into the first positioning piece. According to the optical module, the lens assembly is arranged at the end, close to the optical port of the optical module, of the circuit board, direct connection between the external optical fiber and the lens assembly is achieved through the clamping jaw assembly fixed to the shells, an optical fiberribbon is not needed, space is saved to a certain degree, and further development of the optical module is facilitated.

Owner:HISENSE BROADBAND MULTIMEDIA TECH

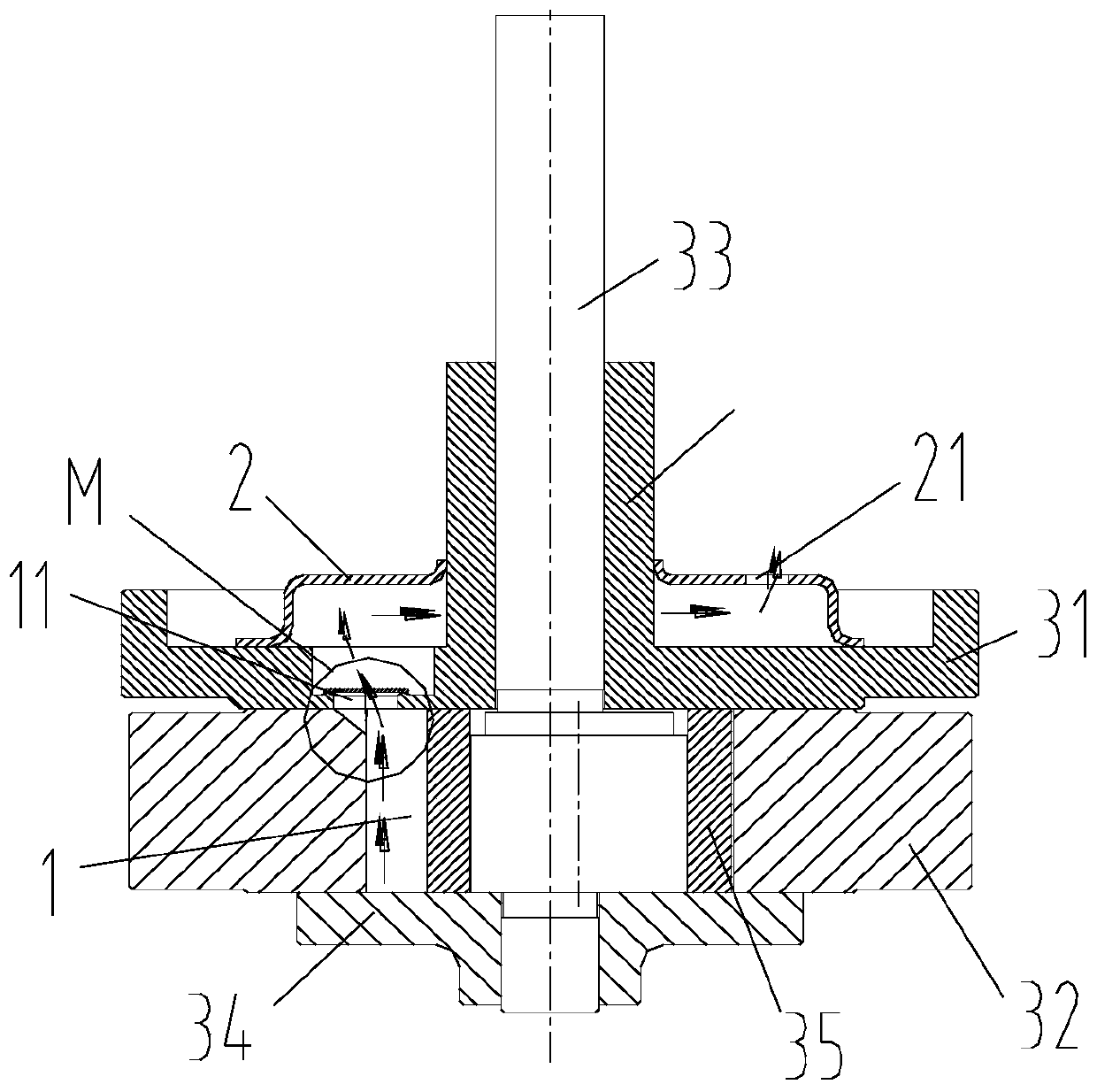

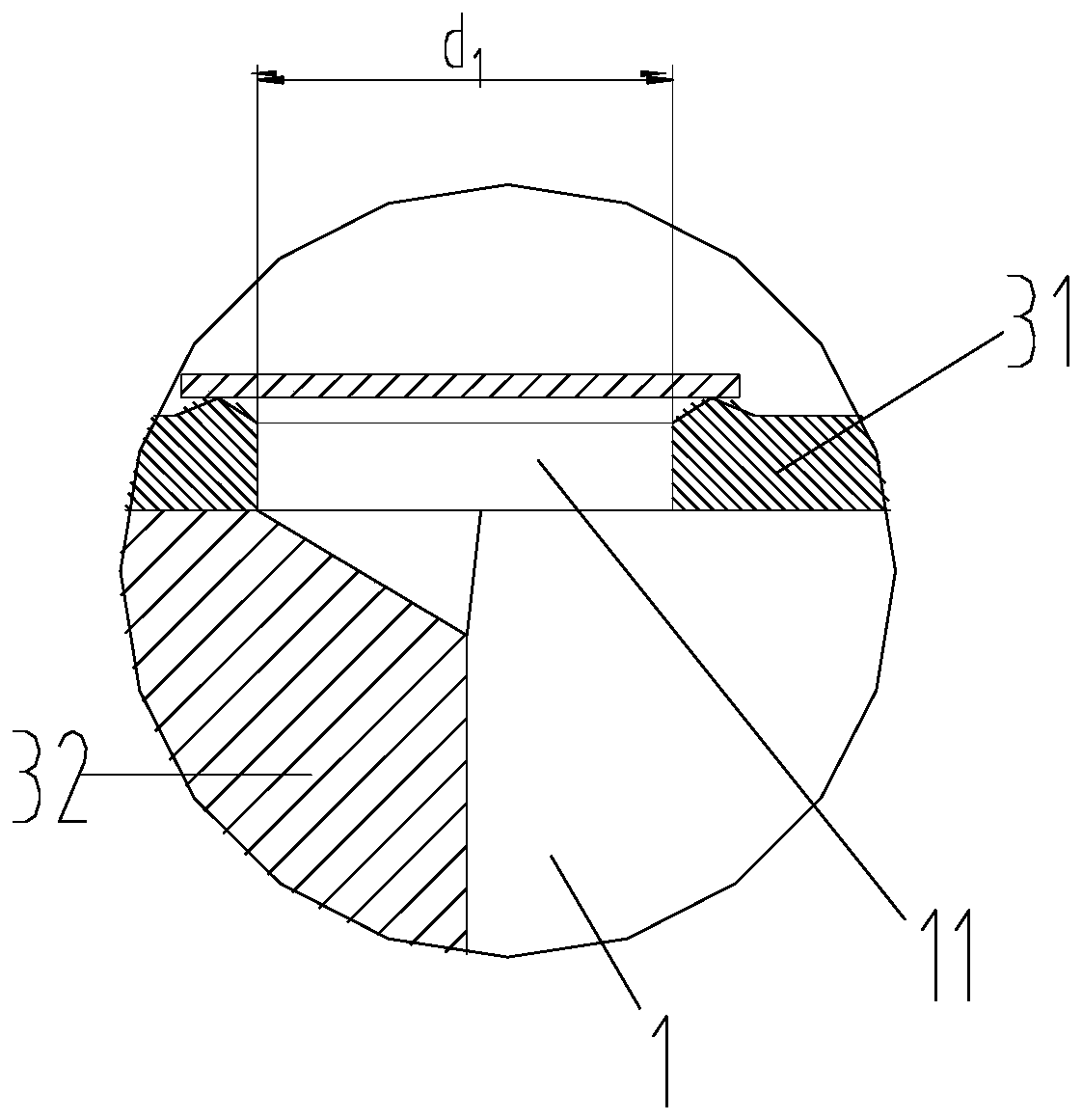

Pump body assembly, rotary compressor and air conditioner

PendingCN111059056AReduce high frequency oil spit rateReduce Reliability RiskRotary/oscillating piston combinations for elastic fluidsRotary piston pumpsMufflerLubrication

The invention provides a pump body assembly, a rotary compressor and an air conditioner. The pump body assembly comprises an air exhaust chamber; the air exhaust chamber is provided with a first air exhaust port; a silencer is arranged at the downstream of the first air exhaust port; the silencer is used for buffering and reducing noise of airflow exhausted by the first air exhaust port; a secondair exhaust port is formed in the silencer; the through-flow area of the first air exhaust port is S1; the through-flow area of the second exhaust port is S0; and S0 and S1 satisfy an relational expression that 0.314<S0 / S1<0.865. According to the pump body assembly, the rotary compressor and the air conditioner, the oil spitting rate of the compressor can be reduced, so that the reliability risk of the compressor caused by insufficient lubrication due to a too high oil spitting rate is reduced; and the refrigerating capacity of the compressor is improved, and high efficiency of the compressoris achieved.

Owner:ZHUHAI GREE REFRIGERATION TECH CENT OF ENERGY SAVING & ENVIRONMENTAL PROTECTION

Optical module

ActiveCN112230349AHigh electromagnetic shieldingAchieve direct connectionCoupling light guidesOptical ModuleEngineering

The invention discloses an optical module. The optical module comprises a circuit board, a light emitting chip, a light receiving chip, a lens assembly and a clamping jaw assembly, the lens assembly is arranged at the end, close to an optical port of the optical module, of the circuit board and covers the light emitting chip and the light receiving chip, one end of the clamping jaw assembly is connected with the lens assembly, and the other end of the clamping jaw assembly is connected with an external optical fiber; the clamping jaw assembly comprises a clamping jaw and a shielding plate, a first positioning piece is arranged on the clamping jaw, a second positioning piece and a third positioning piece are correspondingly arranged on the shielding plate and the lens assembly respectively,and the first positioning piece penetrates through the second positioning piece and is inserted into the third positioning piece; and the lens assembly comprises a lens assembly body and a lens assembly connecting part which are connected with each other, a light through groove is formed in the lens assembly connecting part, a light through hole is formed in the shielding plate, and light path connection of the lens assembly and the clamping jaw assembly is achieved through the light through hole and the light through groove. According to the optical module provided by the invention, transmission of internal optical signals does not need an optical fiber ribbon, so that space is saved to a certain extent, and further development of the optical module is facilitated.

Owner:HISENSE BROADBAND MULTIMEDIA TECH

Trimming resistor and preparation method thereof

ActiveCN103094250AReduce openingNo additional process costsSemiconductor/solid-state device detailsSolid-state devicesChemical residueDielectric layer

The invention provides a trimming resistor comprising a semiconductor substrate, a dielectric layer arranged on the semiconductor substrate, a fuse trimming shape arranged on the dielectric layer through deposit of a fuse, and a passivation layer, wherein the fuse trimming shape comprises a fusing area and two ends, a trimming structure capable of changing current density is arranged in the fusing area, and the two ends of the fuse trimming shape are respectively provided with connecting pads. The passivation layer is formed on the fuse trimming shape and the dielectric layer, and provided with a trimming window corresponding to the trimming structure and pressing point windows respectively corresponding to the connecting pads. The invention further provides a preparation method of the trimming resistor. Due to the fact that the fuse trimming shape is provided with the trimming structure capable of changing the current density in the fusing area, the effective cross section area of the fuse on the trimming structure is small, the current density is large, the fusing position is fixed, the fusing area is small, and meanwhile an opening of the trimming window on the fuse is small so as to reduce reliability risks caused by metal residue, chemical residue and the like due to the fact that the trimming window on the trimming resistor is too large.

Owner:HANGZHOU SILAN INTEGRATED CIRCUIT

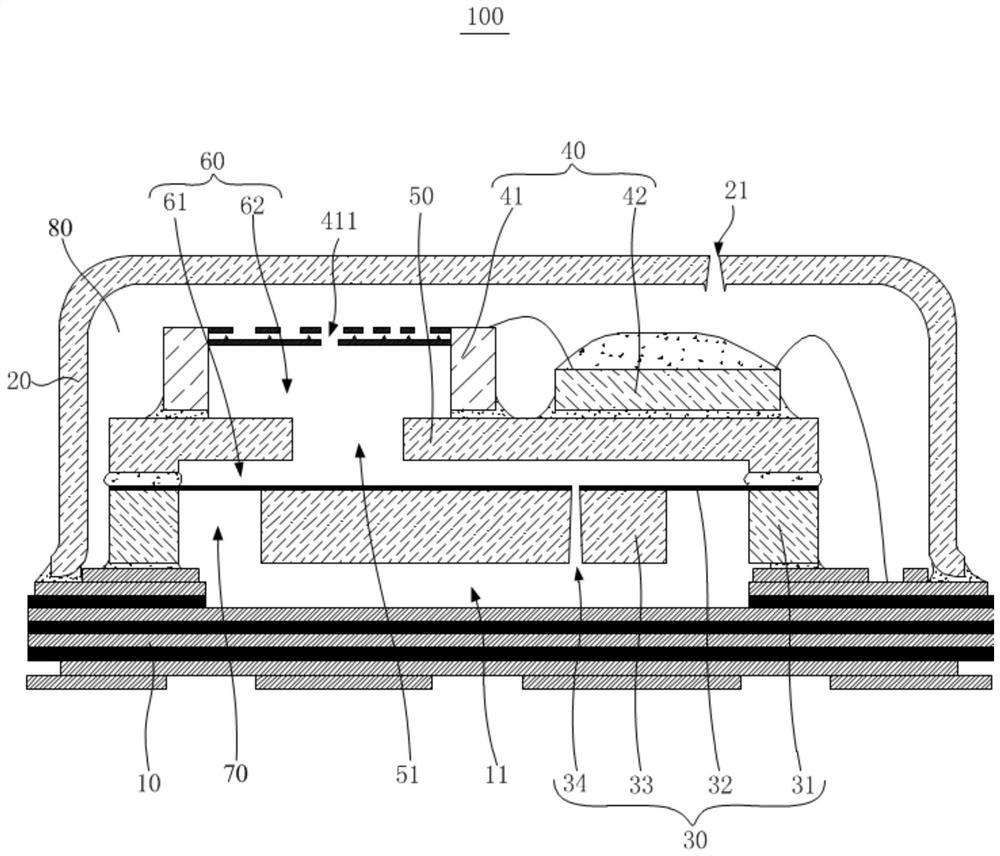

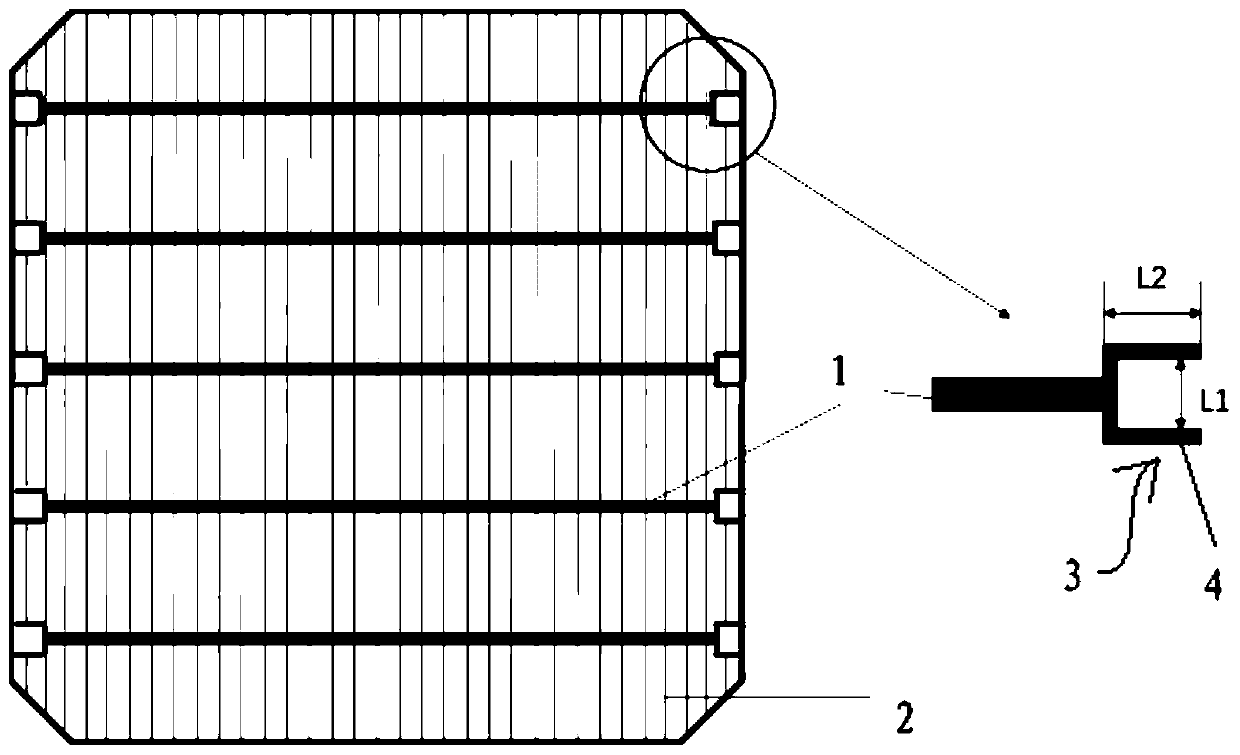

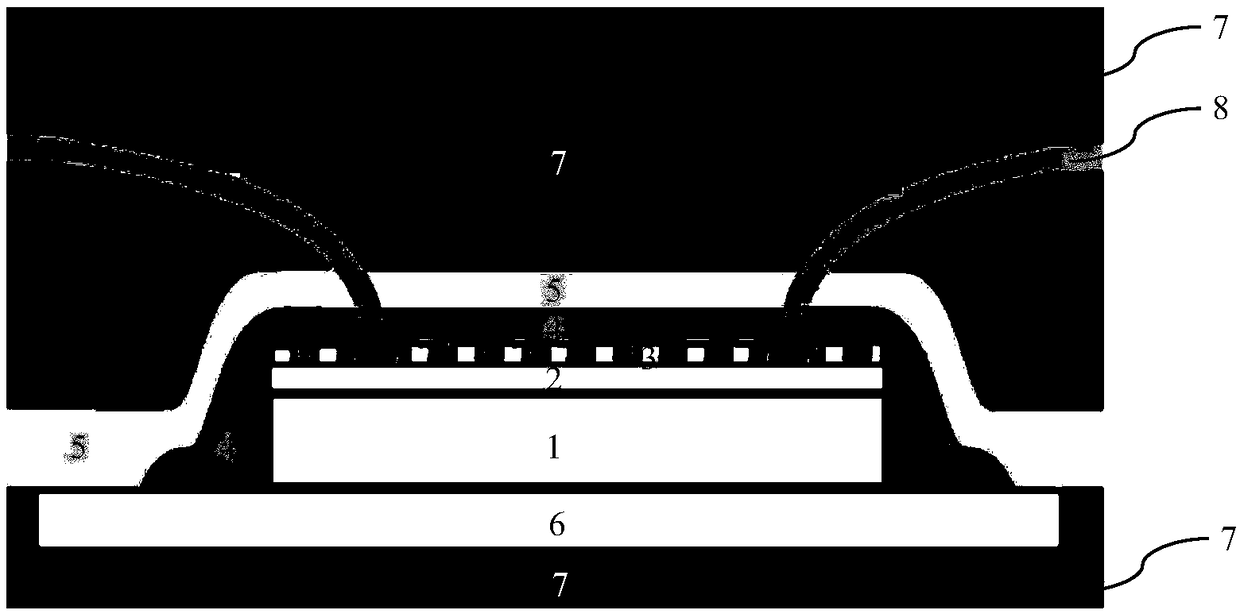

Vibration sensor and electronic equipment

PendingCN113447115AReduce the number of bonding positionsGuaranteed stabilitySubsonic/sonic/ultrasonic wave measurementUsing electrical meansChipsetMechanical engineering

The invention discloses a vibration sensor and electronic equipment, and the vibration sensor comprises a circuit board assembly, a housing, a vibration pickup assembly, a supporting shell and a chip assembly, and the housing covers one side of the circuit board assembly to form an installation space in a surrounding manner; the vibration pick-up assembly is arranged in the installation space and used for picking up external bone vibration to generate response vibration; the supporting shell is connected to the side, away from the circuit board assembly, of the vibration pickup assembly. The chip assembly is connected to the side, away from the circuit board assembly, of the supporting shell and electrically connected with the circuit board assembly. A conduction cavity is defined by the vibration pickup assembly, the supporting shell and the chip assembly, so that response vibration is transmitted to the chip assembly through the conduction cavity. According to the technical scheme, the structure of the vibration sensor is simplified, the machining difficulty and cost are reduced, and meanwhile the structural reliability of the vibration sensor is improved.

Owner:GOERTEK MICROELECTRONICS CO LTD

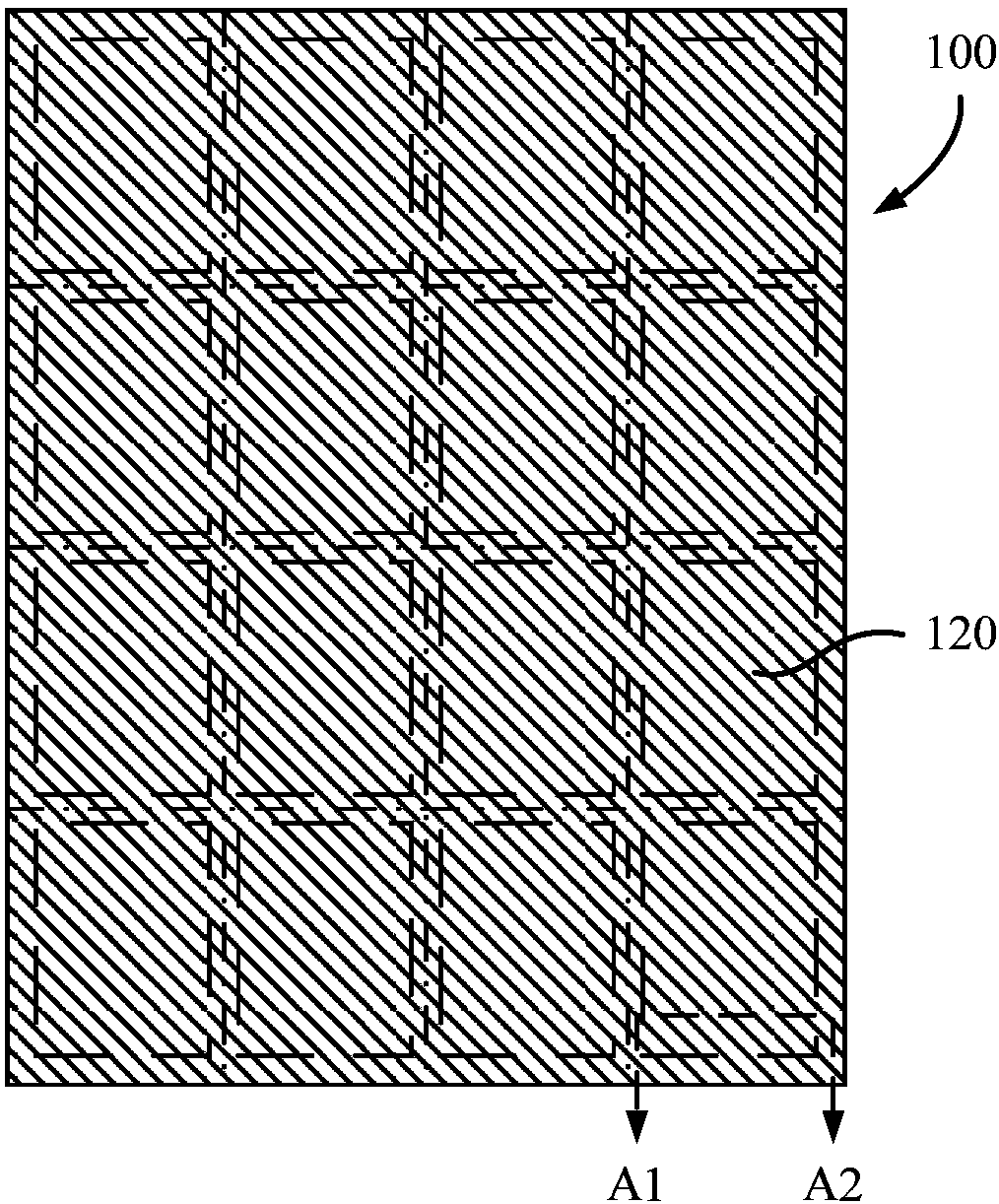

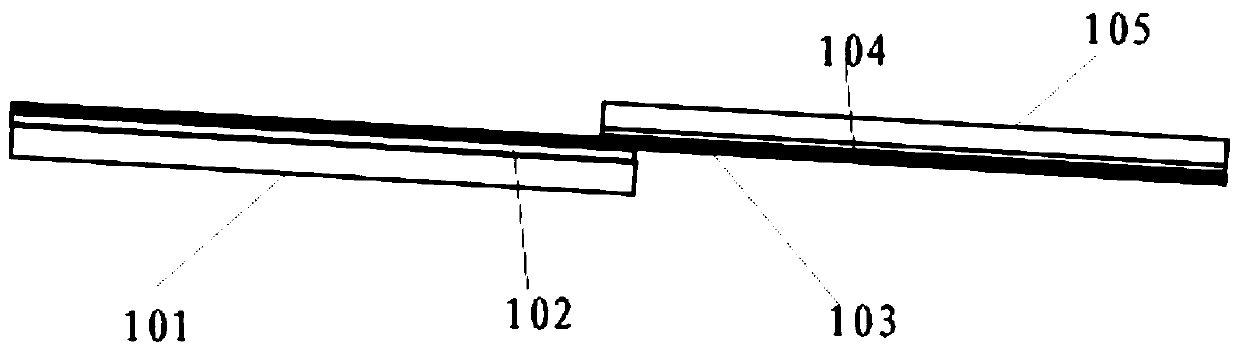

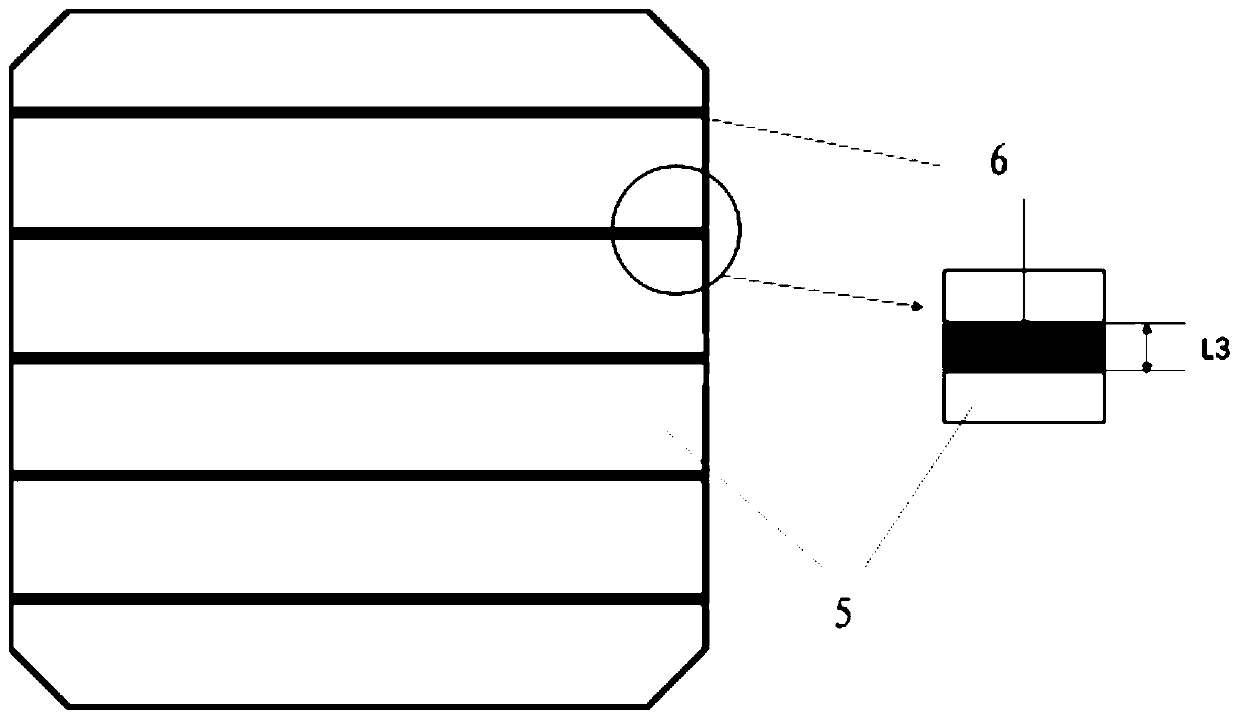

Solar cell, solar cell string and solar cell assembly

PendingCN110085696ALess intrusiveReduce Reliability RiskPhotovoltaic energy generationSemiconductor devicesEngineeringSolar cell

Owner:LONGI SOLAR TECH (TAIZHOU) CO LTD

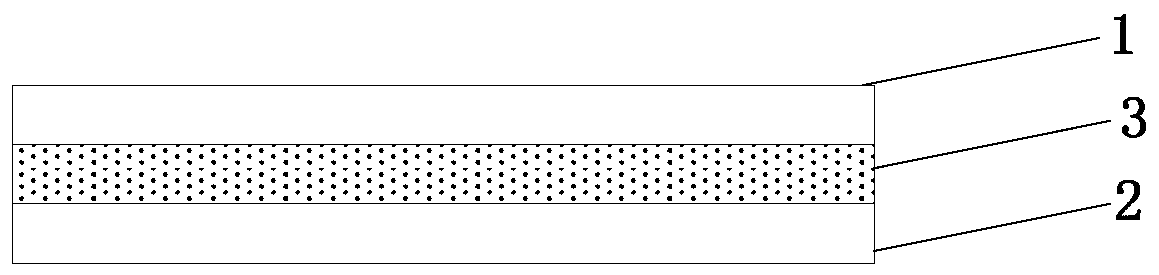

Touch screen and display equipment

PendingCN110794992AReduce Reliability RiskLower resistanceInput/output processes for data processingElectrical connectionEngineering

The invention provides a touch screen and display equipment. The touch screen comprises a substrate and a conducting layer, the conducti layer is arranged on the substrate and comprises a first conducting layer and a second conducting layer which are stacked up and down, and an insulating layer is clamped between the first conducting layer and the second conducting layer; wherein the first conducting layer comprises a first touch electrode and a first electrode lead, the first electrode lead comprises a first wiring part and a first lap joint part which are electrically connected, the second conducting layer comprises a second touch electrode, a second electrode lead and a first redundant electrode lead, and the second electrode lead comprises a second wiring part and a second binding partwhich are electrically connected; a plurality of conducting parts are arranged on the first lap joint part, and the first redundant electrode lead is indirectly conducted with the first lap joint part through climbing of the conduction parts, so that the resistance can be effectively reduced, and the reliability risk of the touch screen is further reduced.

Owner:SHENZHEN LAIBAO HI TECH

Temperature maintaining device and method for integrated circuit chip

ActiveCN109189116AControl working temperatureAvoid permanent failureTemperature control using electric meansTemperature controlHeat current

The invention discloses a temperature maintaining device for an integrated circuit chip. The temperature maintaining device comprises anon-chip heating resistor which is composed of metal circuits ofthe chip, an on-chip temperature detecting circuit used for detecting the inner temperature of the chip, and a heating control circuit controlling switching on and switching off of heating current ofthe on-chip heating resistor based on the temperature value detected by the on-chip temperature detecting circuit to achieve chip temperature control in an on-chip mode. The invention further discloses a temperature maintaining method of the integrated circuit chip. Temperature maintaining of the chip can be achieved, especially, the temperature of the chip can be maintained at the normal workingtemperature when the chip works in the low temperature environment, and therefore temporary failure or permanent failure of the integrated circuit of the chip can be prevented. The cost and power consumption can be reduced, device accuracy requirements can be greatly reduced, reliability risk can be lowered, a manufacturing process window can be improved, the service life of the chip can be prolonged, and the error rate can be reduced.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

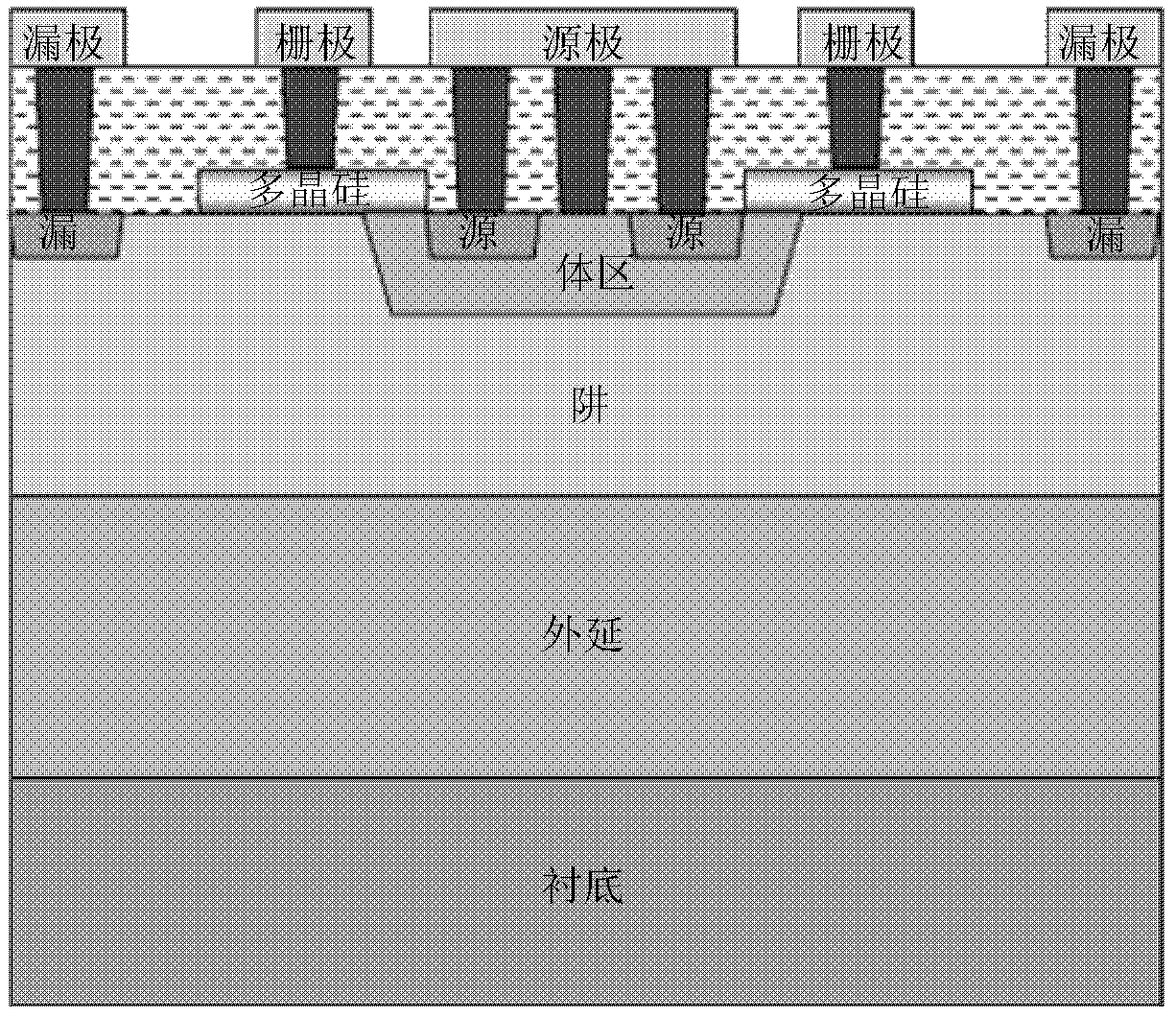

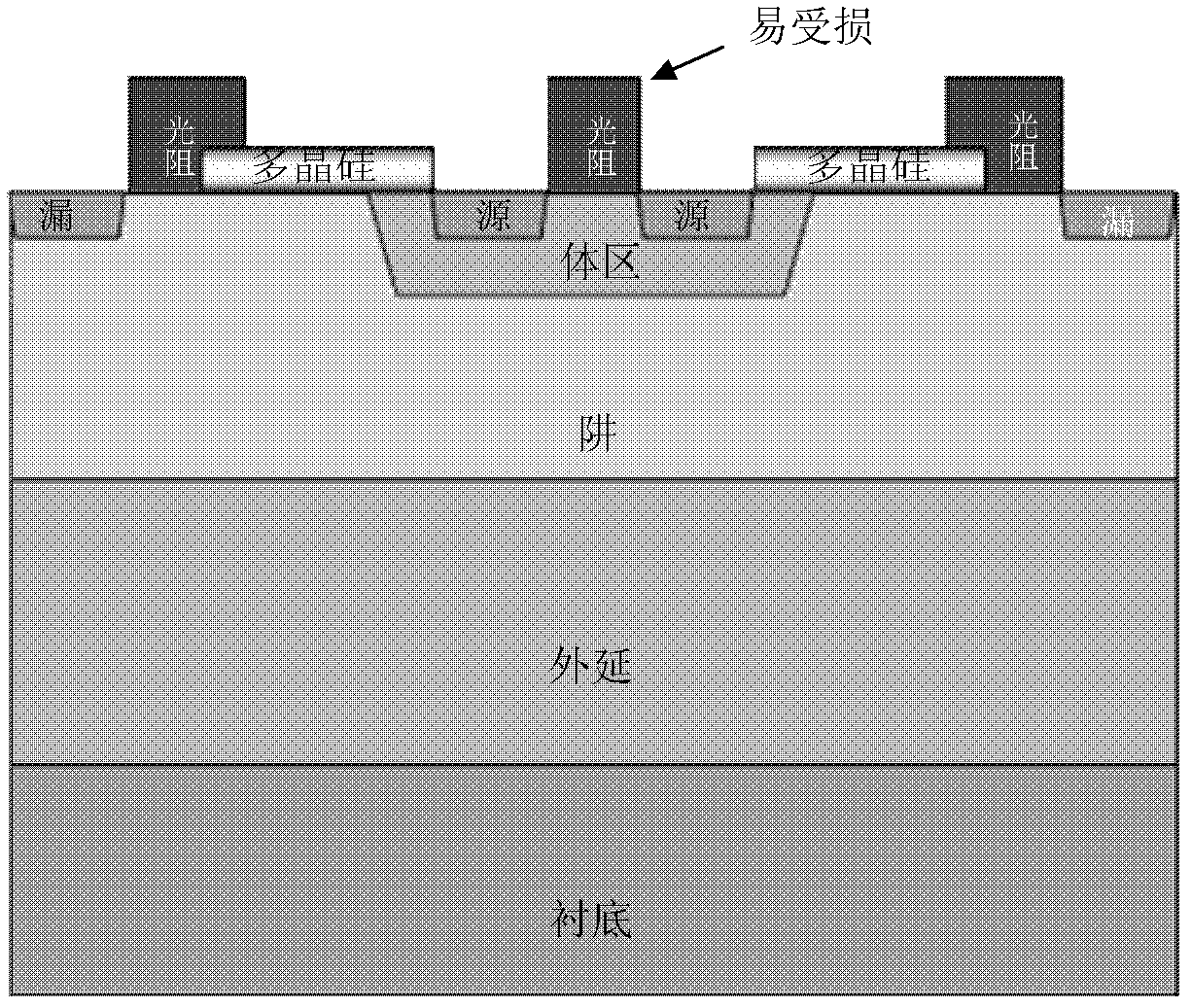

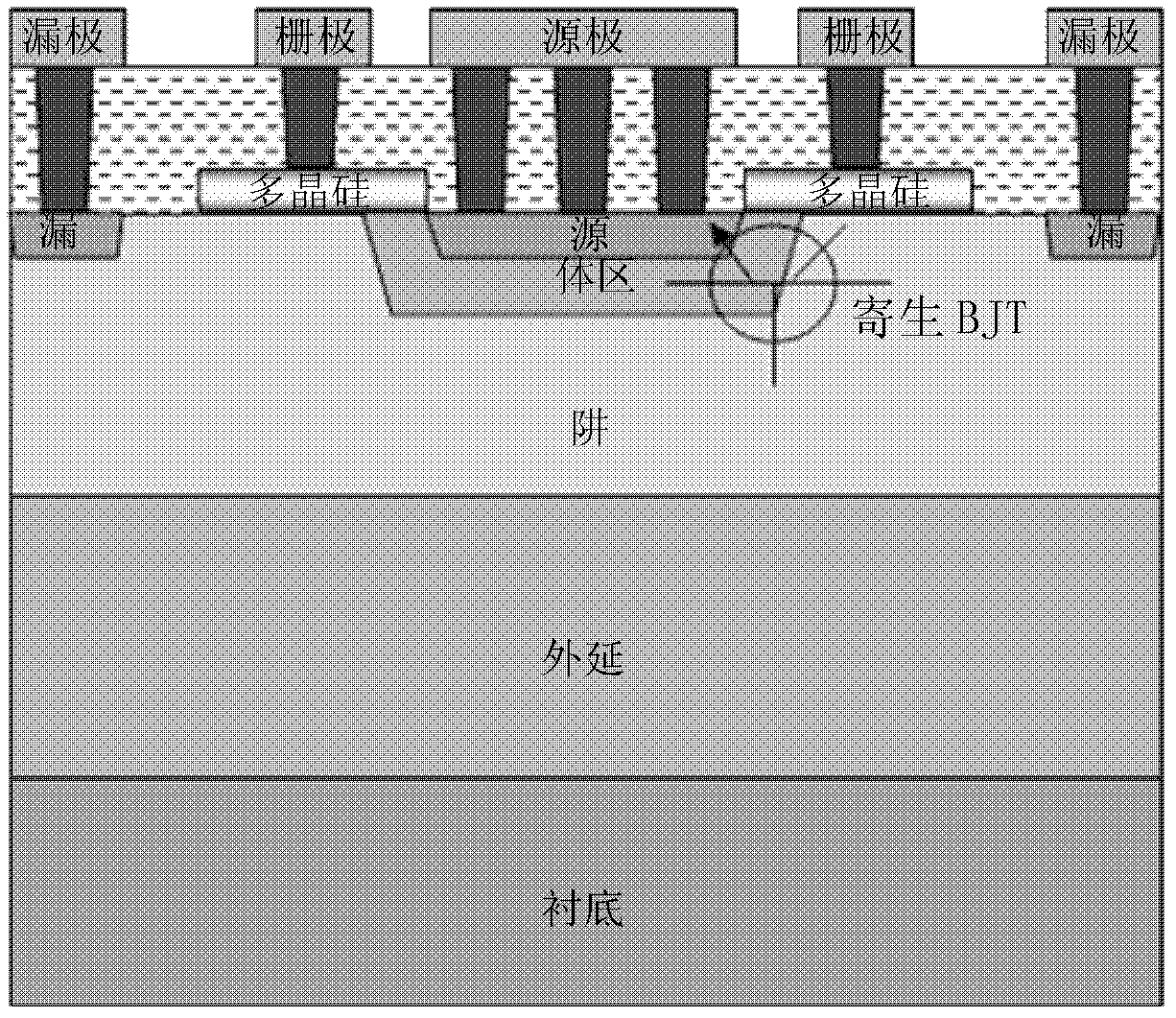

LDMOS (Laterally Diffused Metal Oxide Semiconductor) with selective shallow slot through hole and production method thereof

InactiveCN103177964AReduce design sizeReduce areaSemiconductor/solid-state device manufacturingSemiconductor devicesLDMOSEtching

The invention discloses a production method of an LDMOS (Laterally Diffused Metal Oxide Semiconductor) with a selective shallow slot through hole. The production method of an LDMOS with a selective shallow slot through hole comprises forming a basic structure, forming bottom layer interlamination film; forming a blocking layer; etching the blocking layer which is arranged in an area of the shallow slot through hole; forming top layer interlamination film; performing multi-step high selective etching to form a normal through hole in an area of the blocking layer and the shallow slot through hole of a connector area in an area without the blocking layer; and injecting doping source which has the same type with the connector area at the bottom of the shallow slot through hole after a basic structure is formed. The invention also discloses an LDMOS structure which is produced through the production method. The production method of the LDMOS with the selective shallow slot through hole has the advantages of effectively reducing design size of a source end and an area of a chip and improving reliability of a component due to the fact that different types of doping areas which are vertically distributed in a specified area of the LDMOS are connected with each other with the help of a selective shallow slot through hole technology.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

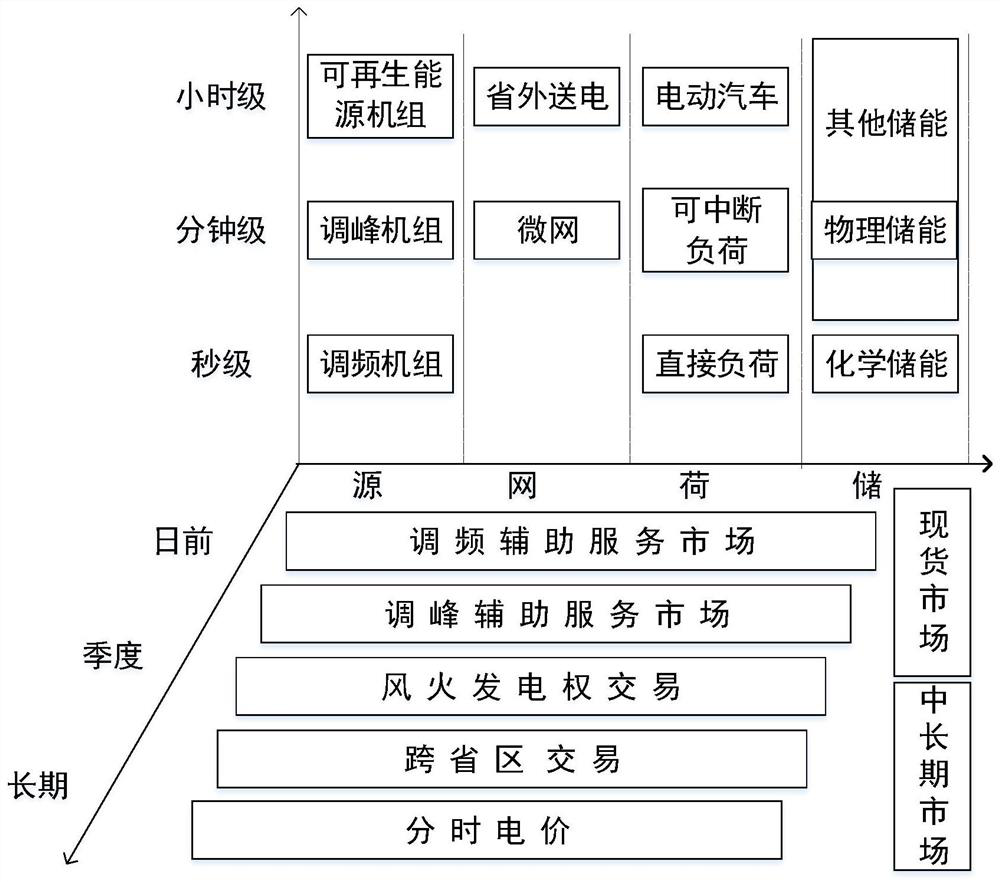

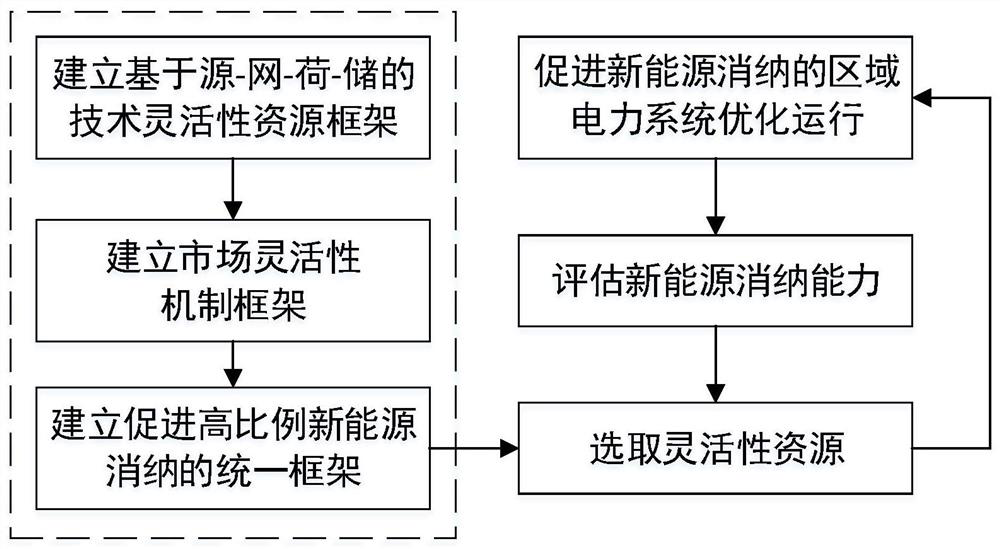

New energy consumption capability evaluation method based on technology and market flexibility unified framework

PendingCN112258064AHigh reliability requirementsReduce flexible scheduling costsForecastingTechnology managementNew energyProcess engineering

The invention discloses a new energy consumption capability evaluation method based on a technology and market flexibility unified framework. The method comprises the following steps: firstly, establishing a time scale-based technical flexibility resource framework of a power supply side, a net rack side, a load side and an energy storage side of a regional power system; secondly, establishing a market flexibility mechanism framework considering a spot market, a wind-fire power generation right transaction, a cross-provincial transaction and a peak regulation auxiliary service market; then comprehensively considering technical flexibility resources and a market flexibility mechanism, and establishing a power system flexibility unified framework for promoting new energy consumption; and finally, quantitatively evaluating the new energy consumption capacity through the new energy power abandoning rate by utilizing the framework, and guiding the regional power system to perform flexible resource selection according to an evaluation result, thereby continuously updating the iterative regional power system to optimize the operation.

Owner:STATE GRID GASU ELECTRIC POWER RES INST +2

Through hole filling manufacturing process of multilayer board

PendingCN114269071AGuaranteed flatnessSurface copper uniformity is improvedPrinted element electric connection formationGrindingCopper foil

The invention relates to a through hole filling manufacturing process of a multi-layer board. The through hole filling manufacturing process comprises the following steps of cutting and baking; in the inner layer circuit, the two inner copper foil layers are subjected to dry film pressing, exposure, development, etching and film stripping treatment, and manufacturing of the inner layer circuit is completed; two-sided pressing: respectively pressing an outer insulating layer and an outer copper foil layer on the two inner copper foil layers to form a four-layer plate; mechanical drilling is conducted, specifically, through holes used for interlayer communication are drilled in the four-layer plate through a drilling machine; pTH: depositing a layer of thin chemical copper on the inner wall of the through hole to realize in-hole conduction; a first outer layer line; filling holes and electroplating; performing grinding; plating copper for the second time; and performing second-time outer-layer circuit manufacturing to complete the manufacturing of the outer-layer circuit. According to the manufacturing process, the reliability of through hole copper plating is improved while the surface copper uniformity of a product is ensured, the pad blocking design of a blind hole is avoided, more design space is provided for customers, and the manufacturing cost is reduced.

Owner:JIANGSU PROVISION ELECTRONICS CO LTD

Electronic equipment

PendingCN113840025AGuaranteed experienceReduce Reliability RiskTelephone set constructionsEngineeringMechanical engineering

The invention discloses electronic equipment, and belongs to the technical field of electronic equipment. The electronic equipment comprises: a shell, wherein a sound inlet hole is formed in the shell, and the shell is provided with an inner cavity; and a microphone and a balance valve arranged in the shell. The microphone is communicated to the sound inlet hole through a first sound guide channel, the balance valve is communicated to the sound inlet hole through a second sound guide channel, and the balance valve is located at the joint of the inner cavity and the second sound guide channel; and the first sound guide channel is communicated with the second sound guide channel.

Owner:VIVO MOBILE COMM CO LTD

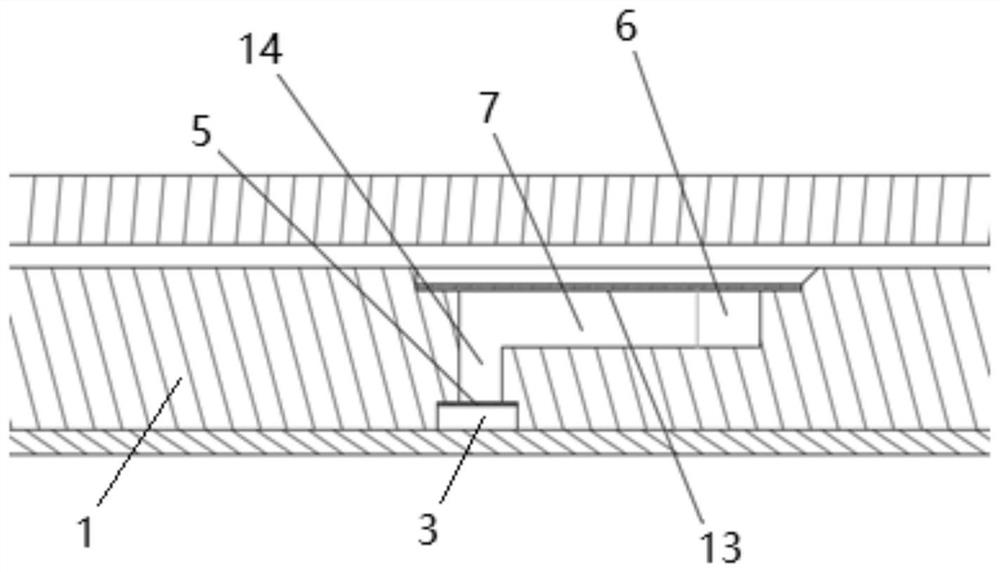

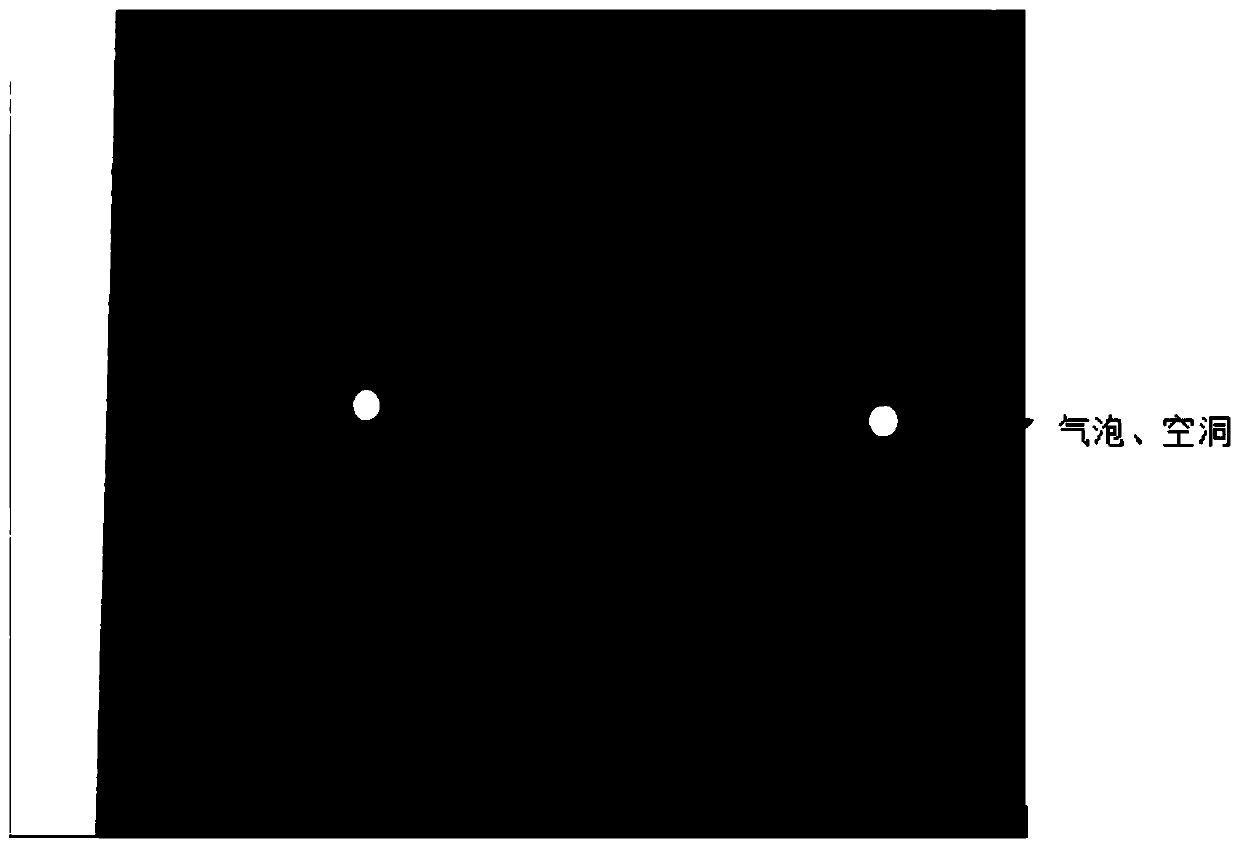

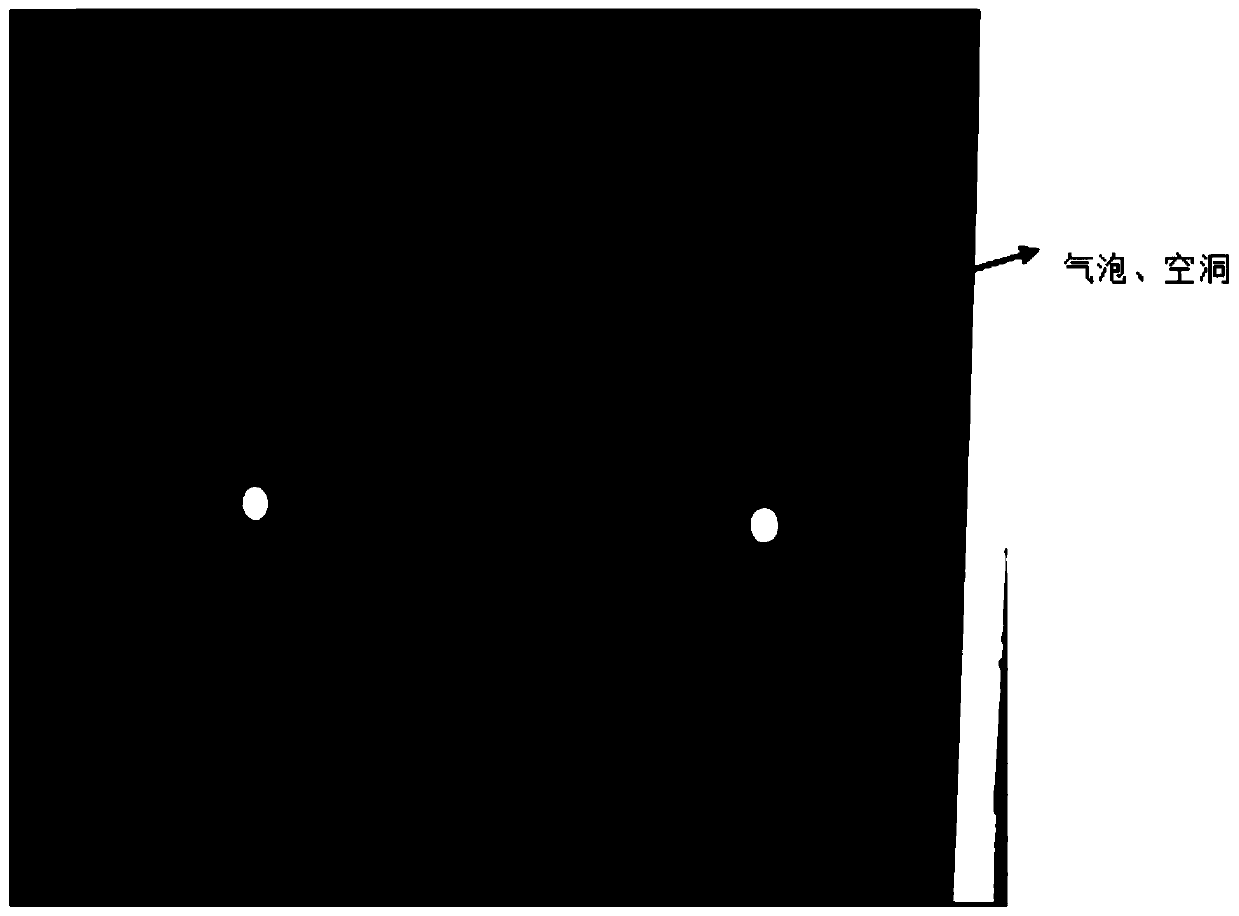

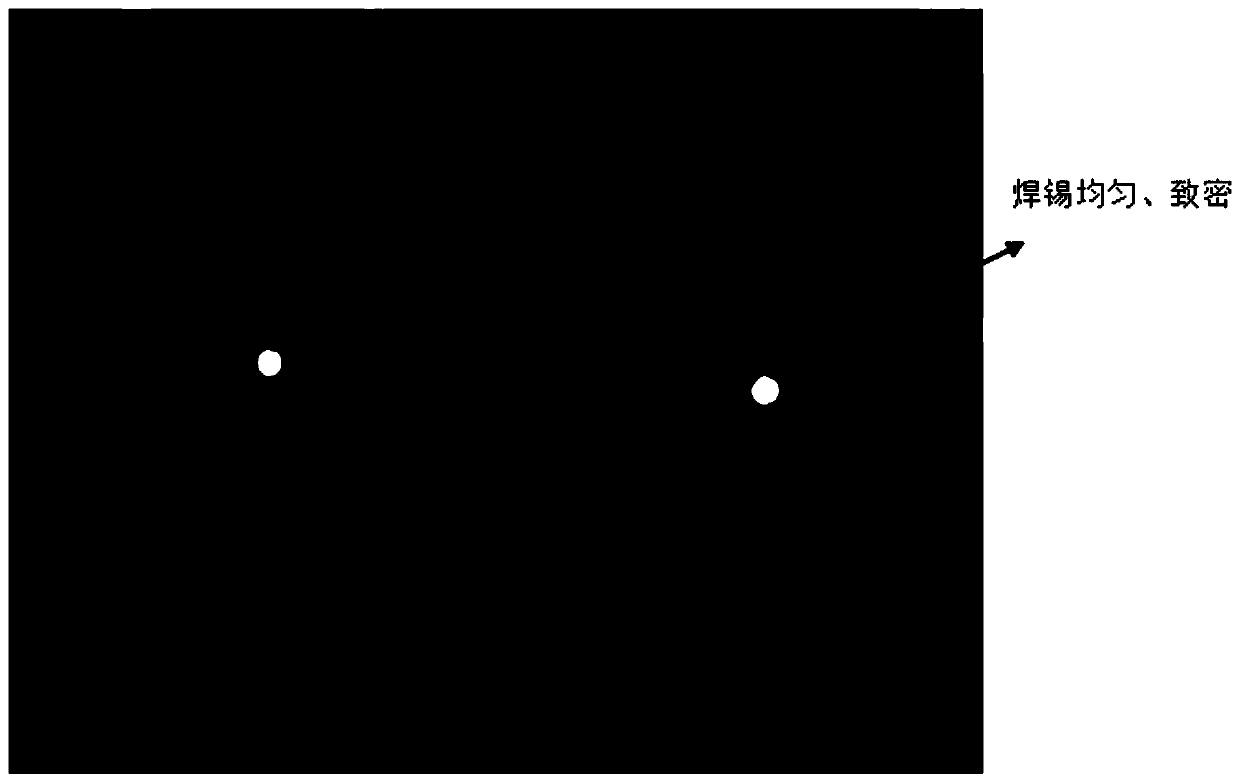

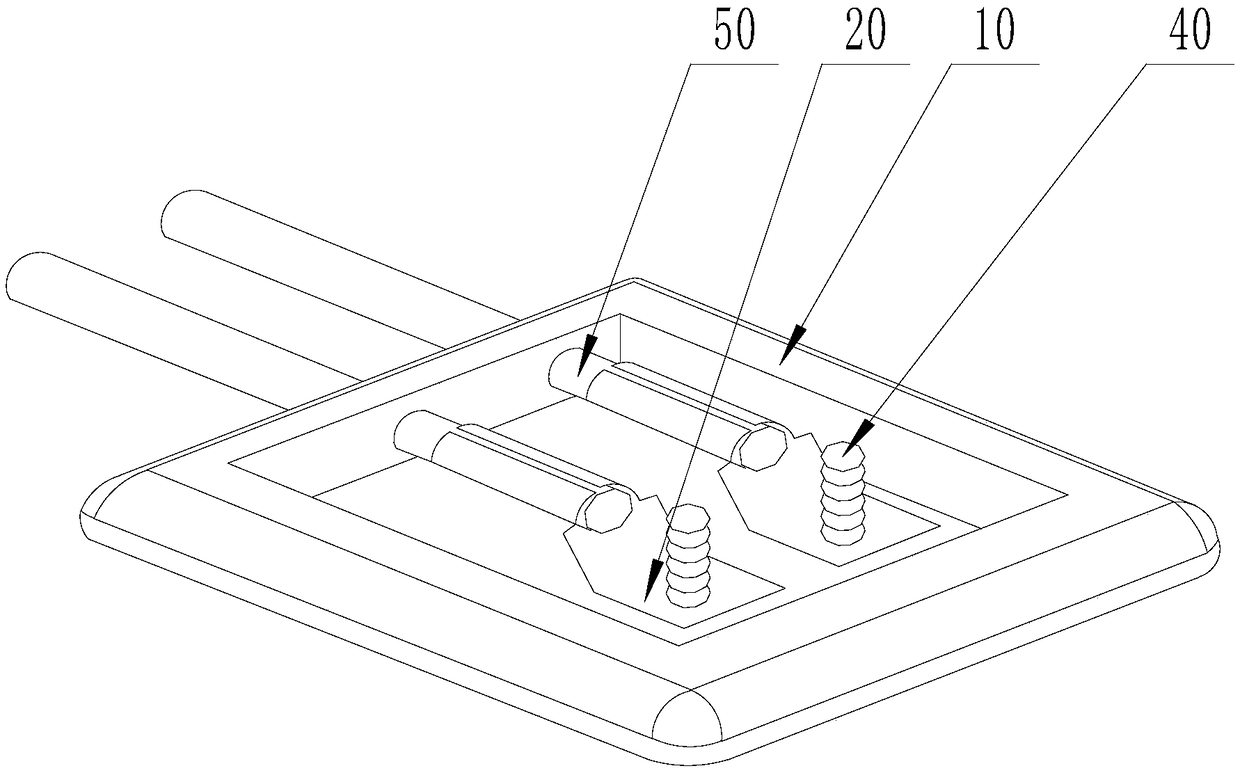

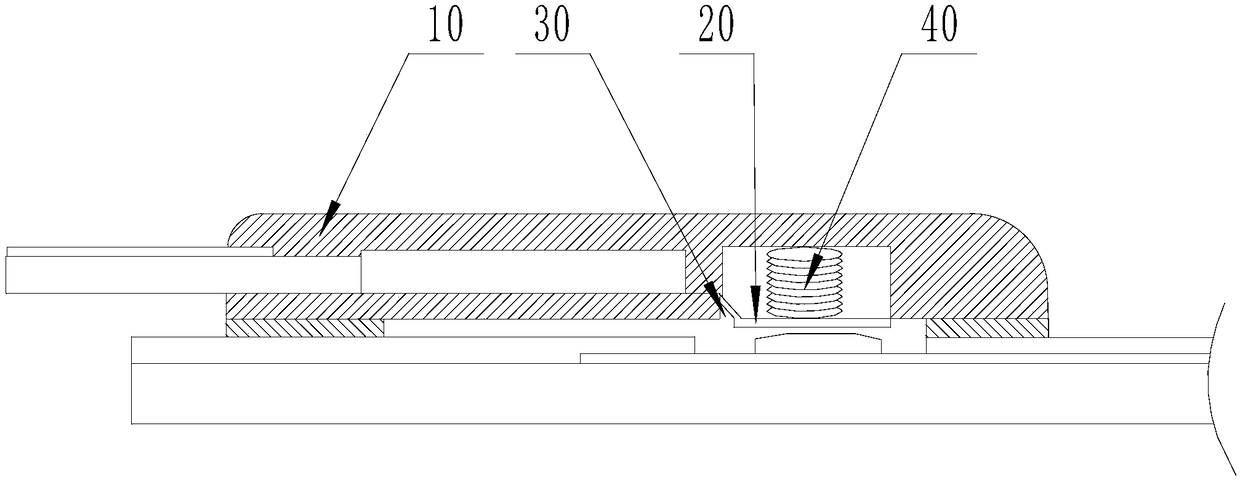

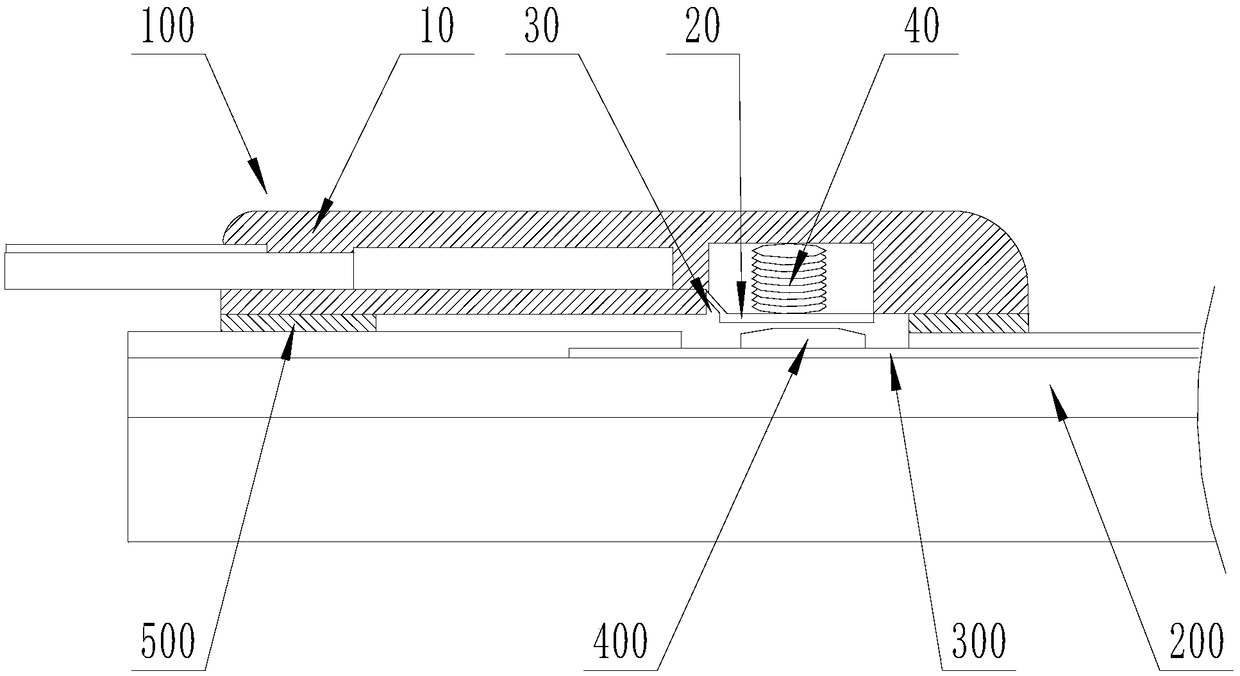

Process for reducing soldering hole rate of soldered printed board by adopting polytetrafluoroethylene block

InactiveCN110587053AEasy and fast to takeImprove high temperature resistanceSoldering apparatusMounting boards securingEngineeringThermal expansion

The invention discloses a process for reducing the soldering hole rate of a soldered printed board by adopting a polytetrafluoroethylene block. The process comprises the following steps of S1, manufacturing a soldering tin sheet corresponding to the printed board, placing the tin sheet in a shell firstly, then turning the printed board with a soldering flux coated to enable the front surface of the printed board to be upward, and feeding the printed board into the shell; S2, pressing the polytetrafluoroethylene block corresponding to the printed board on the printed board, covering the shell with a cover plate and fixing the cover plate with a screw; and S3, carrying out heating and welding treatment, wherein the polytetrafluoroethylene block is subjected to thermal expansion in the heating process to apply the pressing force to the printed board. The process has the beneficial effects that the pressing force is applied to the printed board by the polytetrafluoroethylene block which issubjected to thermal expansion in the heating process, and the heated and melted soldering tin is uniformly distributed under the action of the pressing force, so that the soldering hole rate of theprinted board is reduced, the performance and the reliability of the printed board are improved, the time for rework of product assembling is greatly saved, the soldering frequency is reduced, and theproduct reliability risk is reduced.

Owner:CHENGDU TIGER MICROWAVE TECH

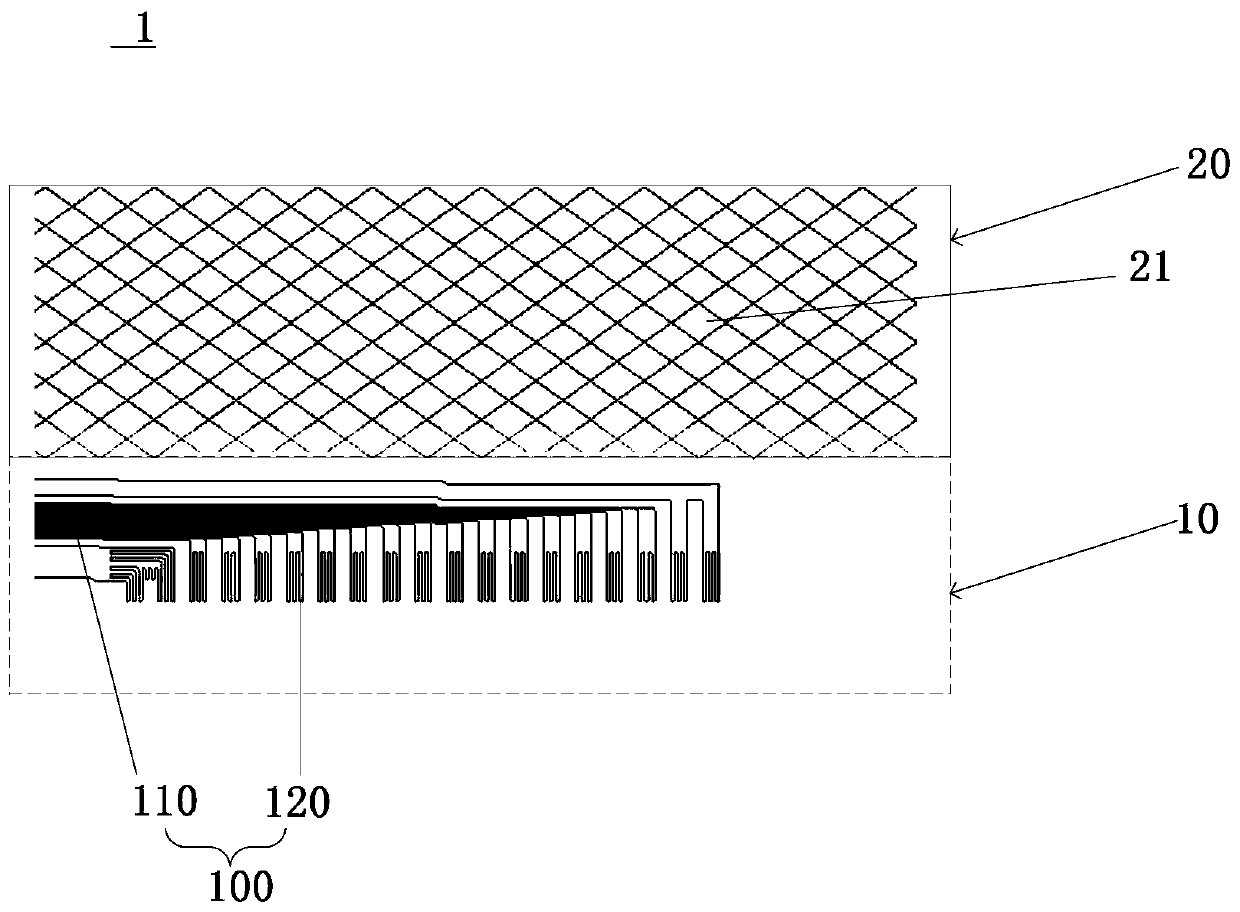

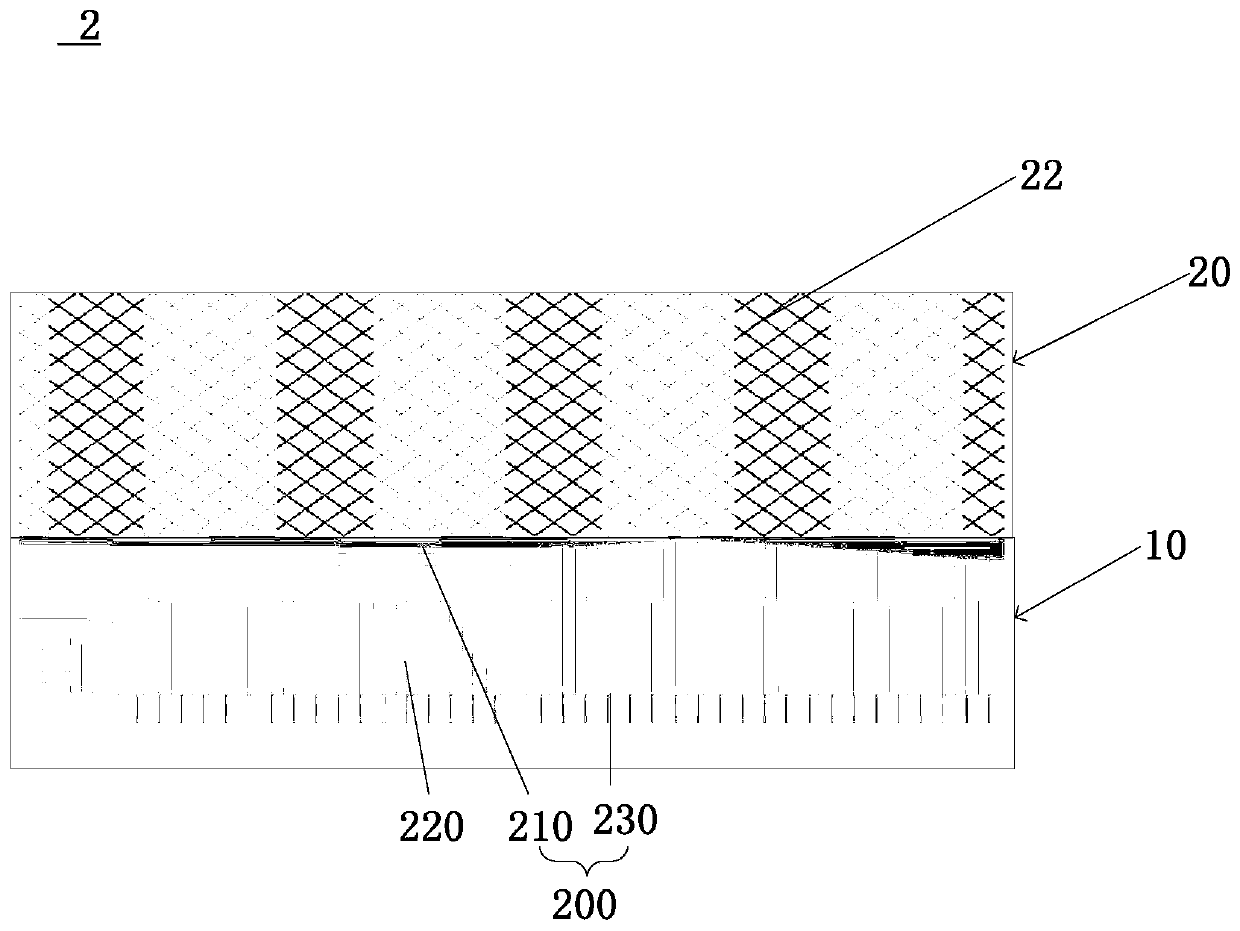

Loudspeaker unit and electronic terminal

ActiveCN111901715AImprove acoustic performanceImprove installation stabilityLoudspeaker transducer fixingLoudspeaker casing supportsEngineeringLoudspeaker

The invention discloses a loudspeaker unit and an electronic terminal. The loudspeaker unit comprises a shell assembly, a magnetic circuit system, a vibration system and a balance assembly, the balance assembly is arranged corresponding to a gap, the balance assembly comprises a centering support chip made of FPCB material, the centering support chip comprises an outer fixing part, an elastic support part and a bonding pad structure, and the outer fixing part is connected with the shell assembly; the elastic supporting part is connected with the outer fixing part, located in the gap and partially connected with a support, and the elastic supporting part elastically deforms along with vibration of the support. The bonding pad structure comprises a cantilever and a bonding pad which are arranged at an included angle, one end of the cantilever away from the bonding pad is connected with the elastic supporting part, the cantilever extends along the support, the bonding pad is fixedly connected with the diaphragm or the top wall of the support, and a lead of the voice coil is electrically connected with the bonding pad. According to the loudspeaker unit provided by the invention, the structure of a voice coil in the magnetic gap is arranged more freely, and the volume of a magnetic circuit system is effectively increased, so that the magnetic field intensity is higher, and the acoustic performance is better.

Owner:GOERTEK INC

Photovoltaic junction box, photovoltaic module and photovoltaic junction box installation method

PendingCN108768289AImprove sealingReduce Reliability RiskPhotovoltaicsPhotovoltaic energy generationAdhesiveSafety risk

The application relates to the technical field of photovoltaics, and particularly relates to a photovoltaic junction box, a photovoltaic module and a photovoltaic junction box installation method. Thephotovoltaic junction box comprises a box body and a connection terminal arranged in the box body; a connection through hole for enabling the connection terminal to be exposed outside is formed at aposition on the box body, where the connection terminal is positioned, so that when the photovoltaic junction box is installed, the connection terminal is in contact with a bus bar of the photovoltaicmodule at a to-be-installed position. According to the photovoltaic junction box provided by the application, a case that the box body is completely hollowed out at the joint of the connection terminal and the bus bar to completely expose the connection terminal is avoided, so that leakproofness of the photovoltaic junction box is improved and filling of a potting adhesive is avoided, thereby avoiding reduction of module reliability and existence of safety risks, which are caused by non-solidification of the potting adhesive, simplifying the installation process and improving installation efficiency.

Owner:MIASOLE EQUIP INTEGRATIONFUJIANCO LTD

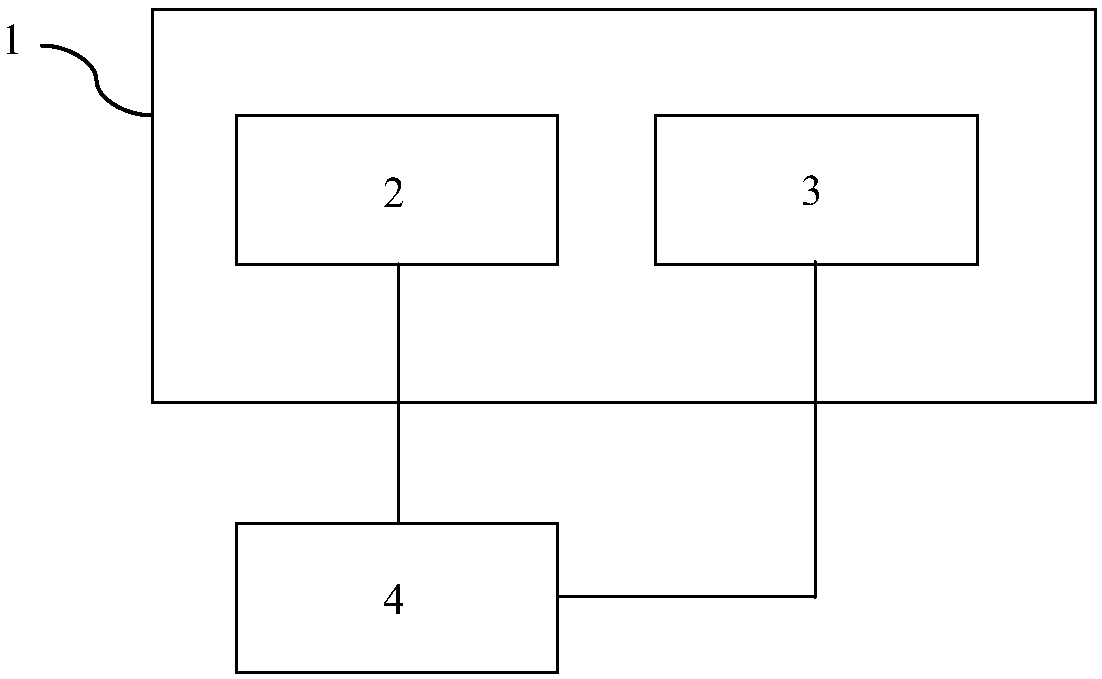

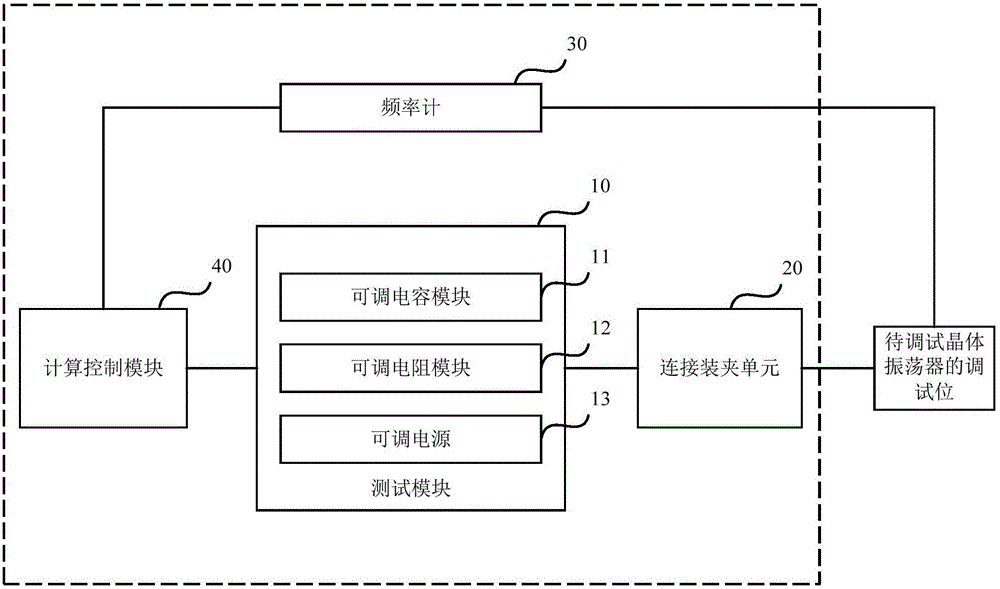

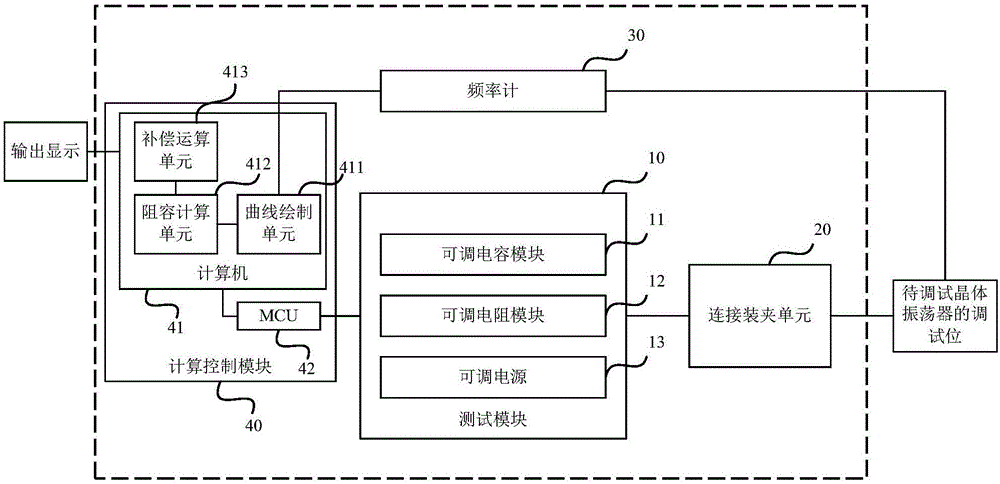

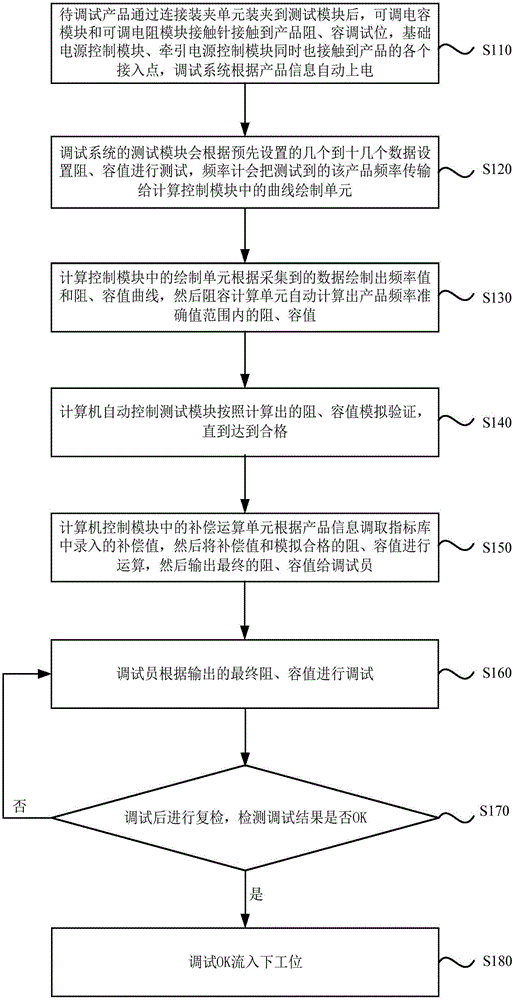

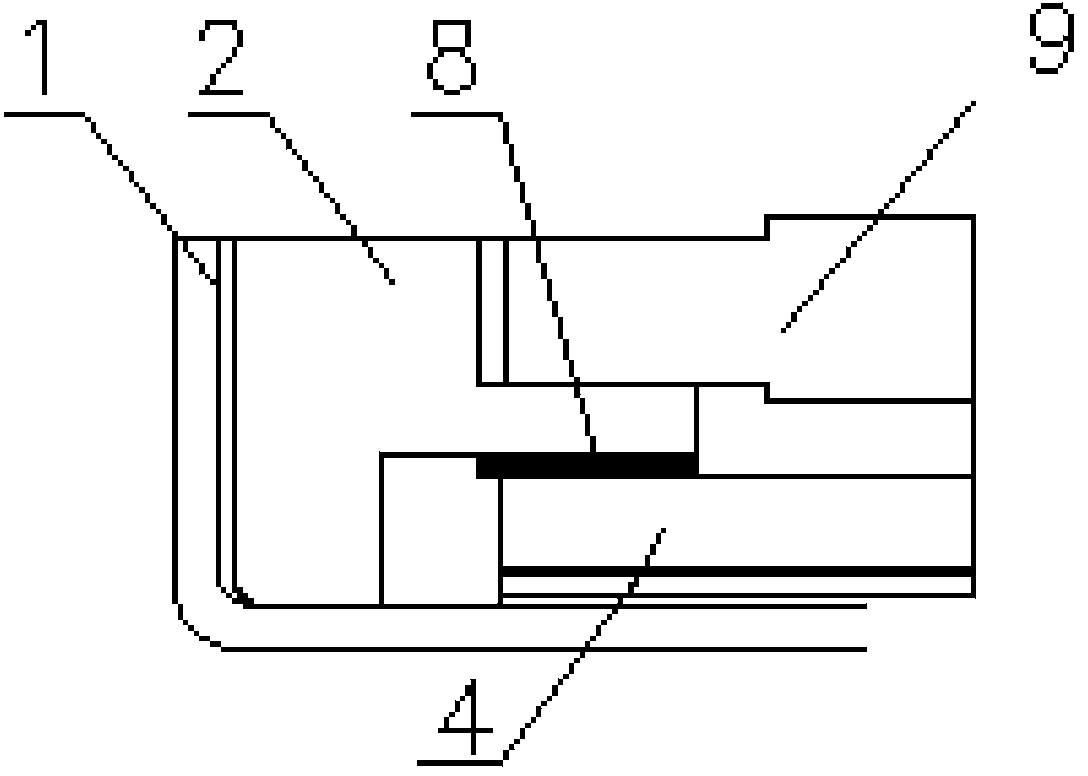

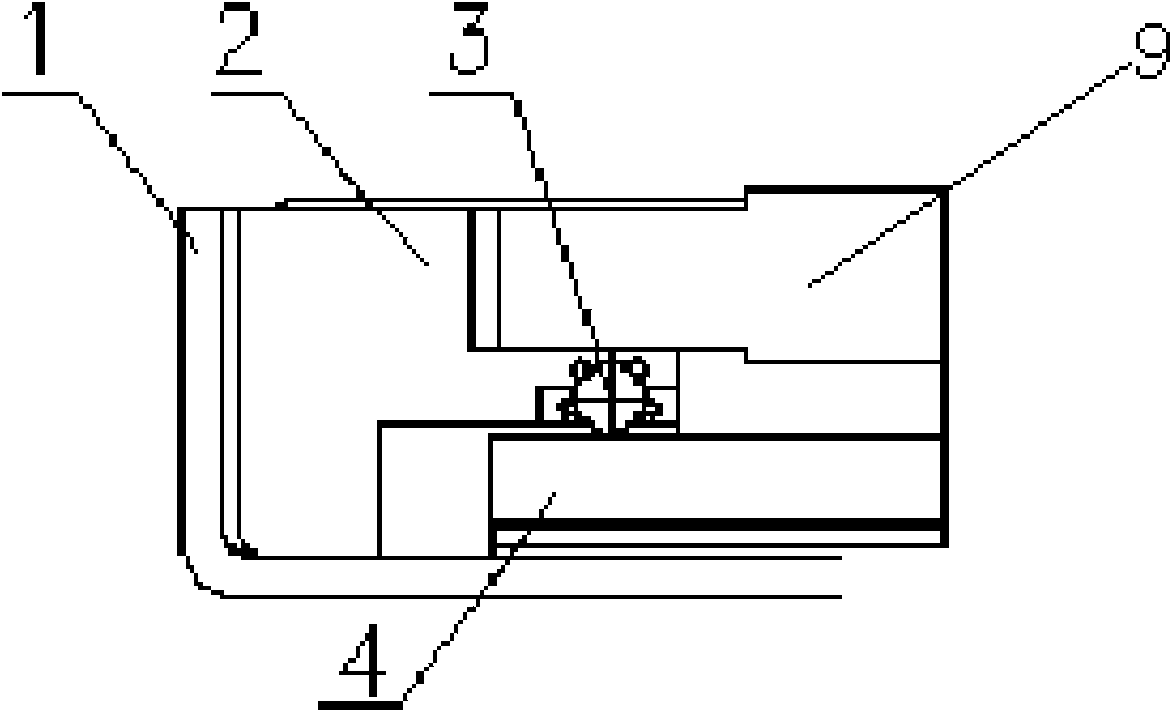

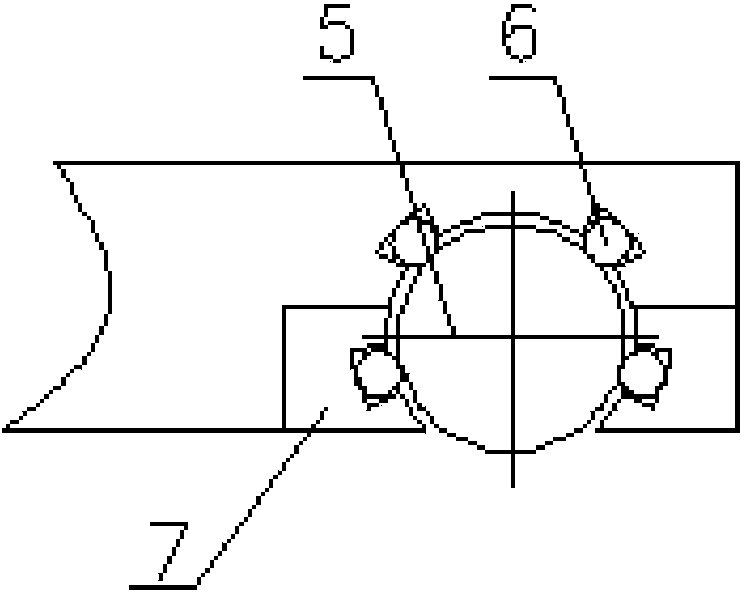

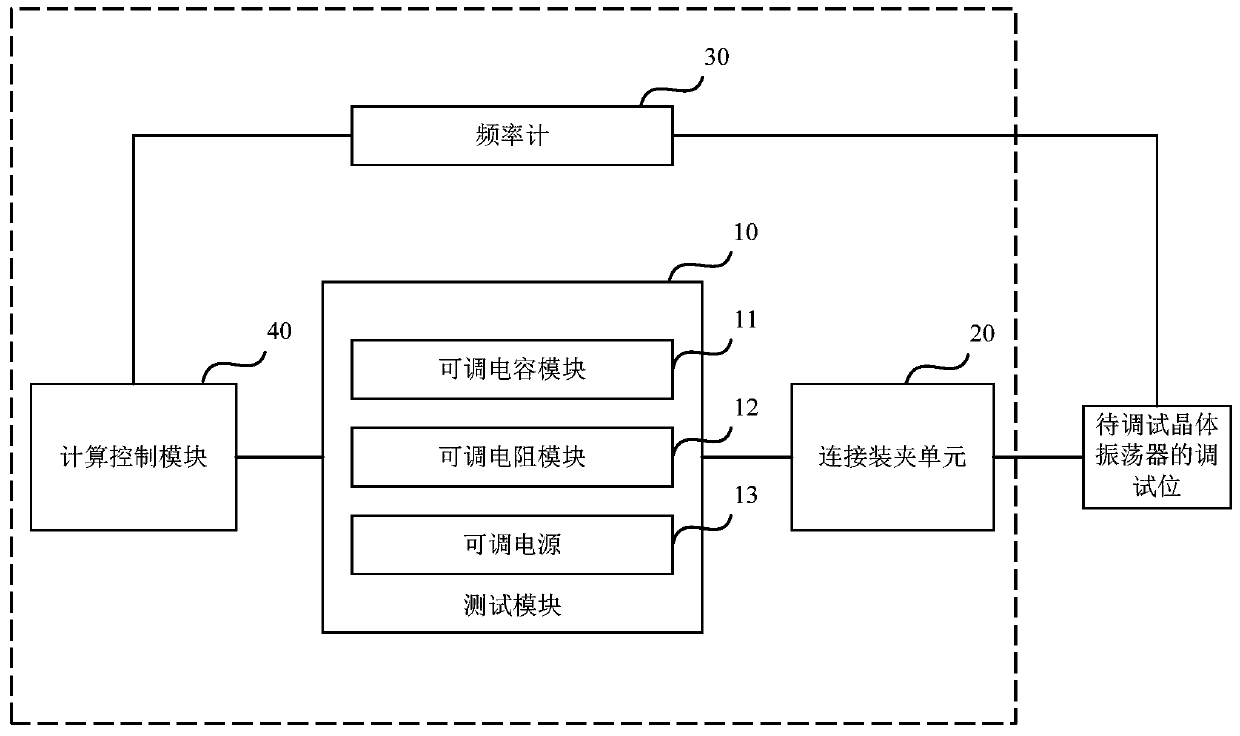

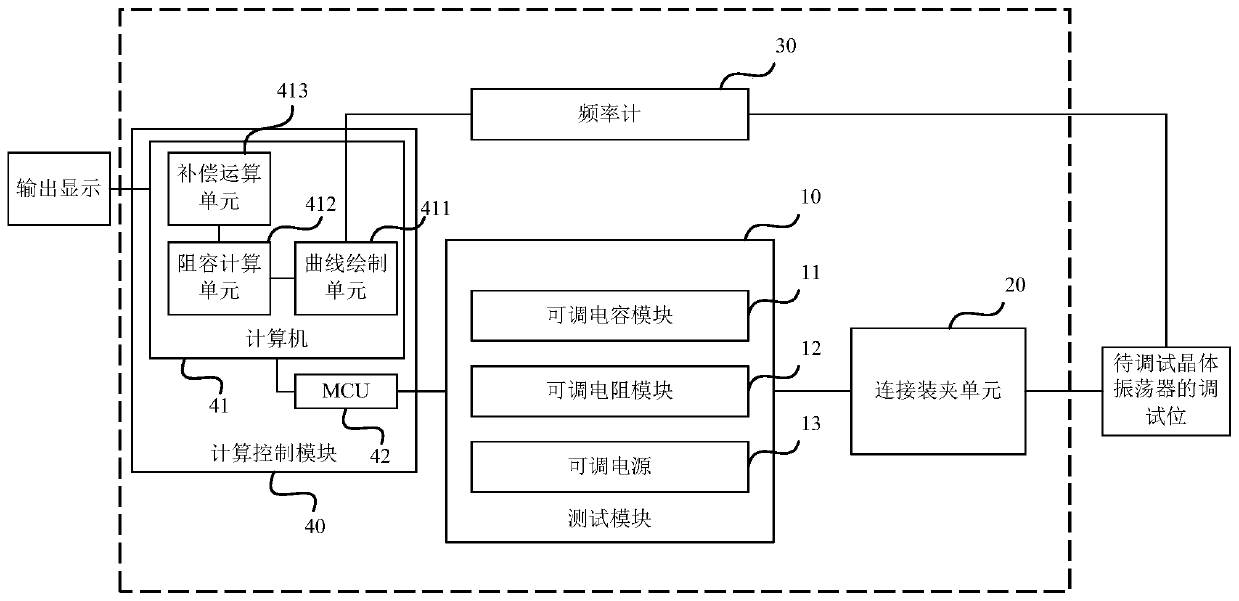

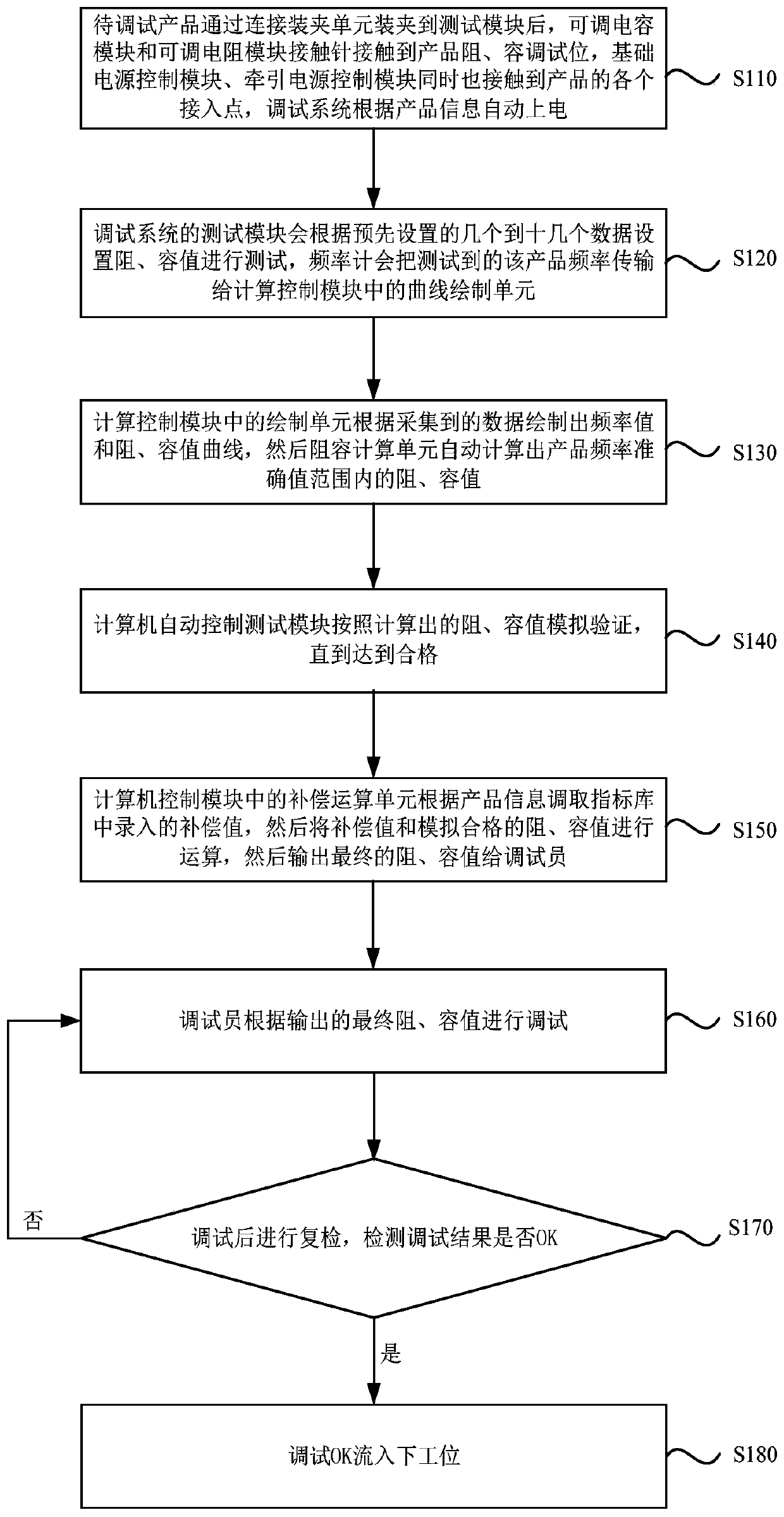

Crystal oscillator frequency debugging system

ActiveCN106685414AReduce Reliability RiskDebug accuratelyPulse automatic controlElectrical resistance and conductanceCapacitance

The invention discloses a crystal oscillator frequency debugging system. The system includes: a test module which includes an adjustable capacitance module, an adjustable resistance module and an adjustable power supply; a connection clamping unit which has an input end and an output end, wherein the input end is in separate connection to the output ends of the adjustable capacitance module, the adjustable resistance module and the adjustable power supply, and the output end is intended for connecting a debugging bit of a to-be-debugged crystal oscillator; a frequency meter which is intended for connecting the to-be-debugged crystal oscillator and reading frequencies; a computing control module which is connected to a control end of the test module and the frequency meter and is intended for separately outputting capacitance control parameters, resistance control parameters and power control parameters to the adjustable capacitance module, the adjustable resistance module and the adjustable power supply so as to form required capacitance, resistance and power value which are to be loaded to the debugging bit of the to-be-debugged crystal oscillator, reading the frequency of the to-be-debugged crystal oscillator and adjusting the capacitance control parameters. According to the invention, the crystal oscillator frequency debugging system optimizes production procedures and increases production efficiency.

Owner:GUANGDONG DAPU TELECOM TECH CO LTD

A high-reliability edge pulse generation circuit for intelligent power modules

ActiveCN105007062BReduce transmission delayGuaranteed normal outputElectric pulse generator circuitsMOSFETControl signal

The invention relates to a high-reliability edge pulse generation circuit for an intelligent power module, which is based on a brand-new circuit design architecture and can be applied to high-side control signals with any pulse width, no matter whether the input signal is a normal pulse width, a narrow pulse, or even a super pulse width. The narrow pulse can ensure the normal output of the reset RESET pulse signal, which fundamentally solves the problem that the high-side output signal cannot be reset caused by the narrow pulse input signal, reduces the reliability risk of high-side and low-side MOSFET straight-through, and effectively guarantees all Apply the stability of the work of each module in the intelligent power module; not only that, the high-reliability edge pulse generation circuit designed by the present invention has a simple structure, which solves the limitation of the traditional edge pulse generation circuit on the input pulse width, thereby saving signal transmission. The multi-stage noise filter circuit in the path reduces the transmission delay of the signal and improves the working switching frequency.

Owner:豪威模拟集成电路(北京)有限公司

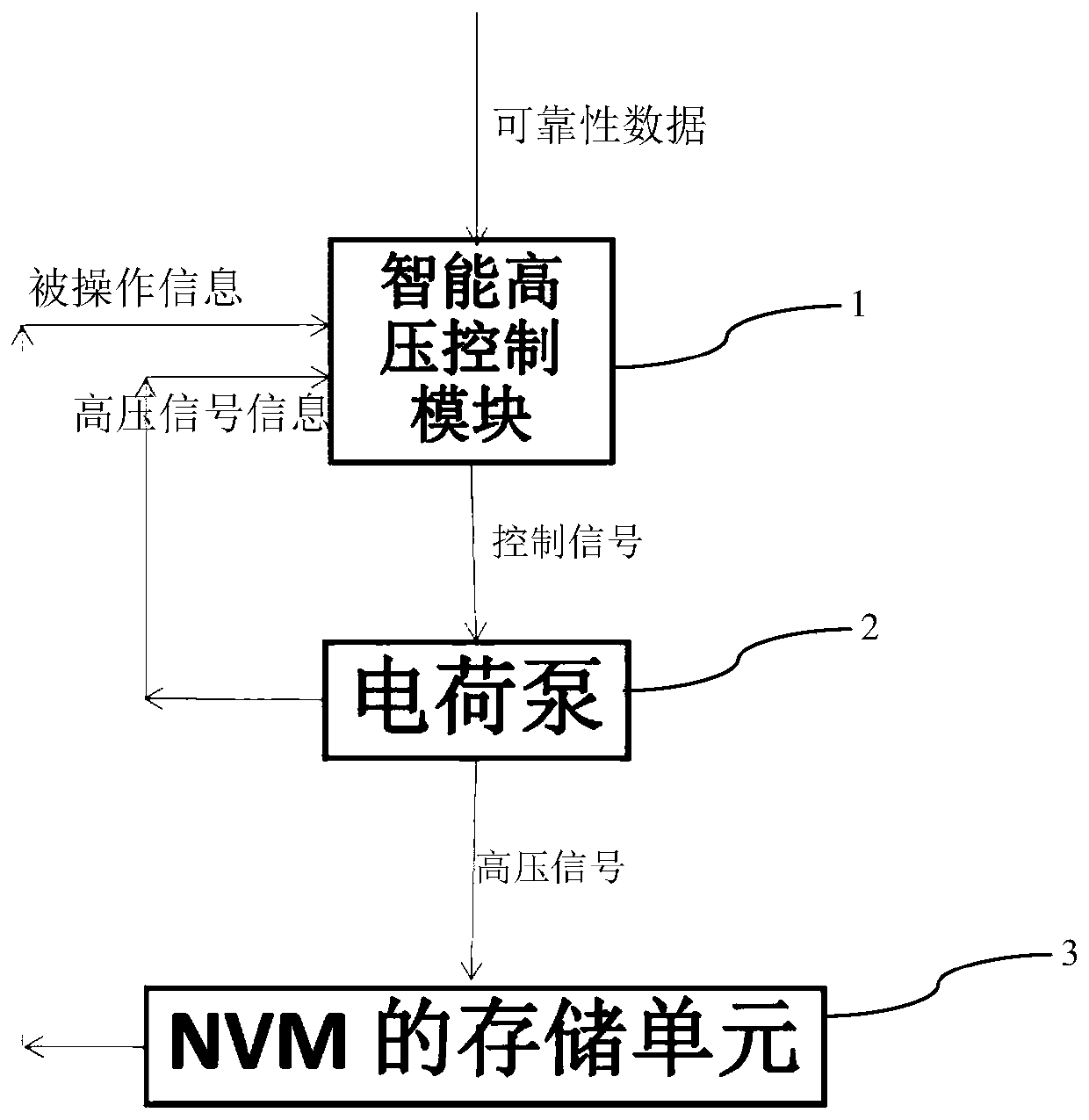

NVM reliability improving device and method

InactiveCN109872758AReduce sizeReduced variation in electrical characteristicsInput/output to record carriersRead-only memoriesControl signalComputer module

The invention discloses a reliability improving device of an NVM. The system comprises an intelligent high-voltage control module which outputs a control signal to a charge pump and controls the magnitude of a high-voltage signal output by the charge pump, the high-voltage signal is provided for each storage unit of an NVM and realizes high-voltage operation on the storage units, and operated information and high-voltage signal information of the storage units are input into the intelligent high-voltage control module; Reliability data of the storage unit are formed on the reliability test platform. When high-voltage operation is carried out, the intelligent high-voltage control module provides a corresponding control signal to the charge pump according to the operated information and thehigh-voltage signal information corresponding to the storage unit and the requirements of the reliability data and provides a corresponding high-voltage signal to realize high-voltage operation. The invention further discloses a reliability improving method of the NVM. The reliability of the NVM can be improved, the service life of a chip of the NVM is prolonged, and the error rate is reduced.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

Loudspeaker monomer and electronic terminal

ActiveCN111901714BImprove acoustic performanceReduce stress distributionLoudspeaker transducer fixingLoudspeaker casing supportsStructural engineeringLoudspeaker

Owner:GOERTEK INC

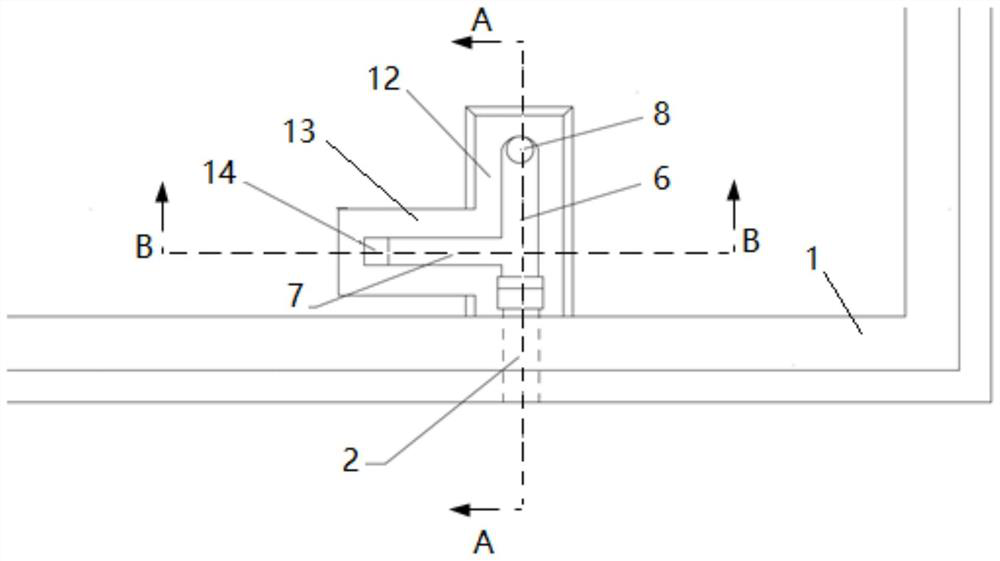

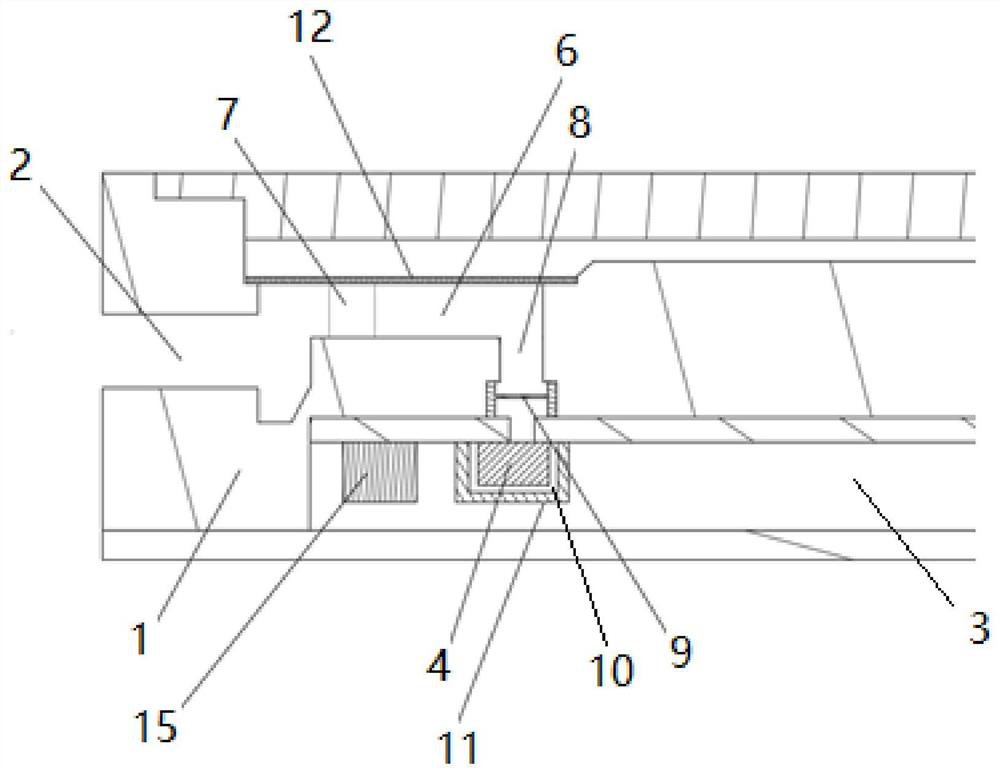

Light guide plate compressing structure and backlight module

The invention relates to the technical field of displays, in particular to a light guide plate compressing structure and a backlight module. The light guide plate compressing structure comprises a plastic frame, a rolling component and a compressing member, a protruding portion of the plastic frame is positioned between a display screen panel and a light guide plate, the lower portion of the protruding portion is provided with a deboss matched with the rolling component, the rolling component is positioned in the deboss and compressed by the compressing member arranged in the protruding portion, and the bottom of the rolling component is extended out of the protruding portion and contacts with the light guide plate to slightly press on the light guide plate. When the light guide plate expands in a high-temperature high-pressure experiment, the bottom of the rolling component and the light guide plate are in rolling friction, and the light guide plate moves and extends horizontally and does not deform due to expanding and being limited, so that reliability risk of the light guide plate is lowered.

Owner:HEFEI XINSHENG OPTOELECTRONICS TECH CO LTD +1

A crystal oscillator frequency debugging system

ActiveCN106685414BReduce Reliability RiskDebug accuratelyPulse automatic controlCapacitanceEngineering

The invention discloses a crystal oscillator frequency debugging system. The system includes: a test module which includes an adjustable capacitance module, an adjustable resistance module and an adjustable power supply; a connection clamping unit which has an input end and an output end, wherein the input end is in separate connection to the output ends of the adjustable capacitance module, the adjustable resistance module and the adjustable power supply, and the output end is intended for connecting a debugging bit of a to-be-debugged crystal oscillator; a frequency meter which is intended for connecting the to-be-debugged crystal oscillator and reading frequencies; a computing control module which is connected to a control end of the test module and the frequency meter and is intended for separately outputting capacitance control parameters, resistance control parameters and power control parameters to the adjustable capacitance module, the adjustable resistance module and the adjustable power supply so as to form required capacitance, resistance and power value which are to be loaded to the debugging bit of the to-be-debugged crystal oscillator, reading the frequency of the to-be-debugged crystal oscillator and adjusting the capacitance control parameters. According to the invention, the crystal oscillator frequency debugging system optimizes production procedures and increases production efficiency.

Owner:GUANGDONG DAPU TELECOM TECH CO LTD

Optical fingerprint identification module and forming method thereof

PendingCN112215046AReduce Reliability RiskReduce thicknessPrint image acquisitionMatching and classificationHigh densityPrinted circuit board

The invention provides an optical fingerprint identification module and a forming method thereof. The optical fingerprint identification module comprises an image sensor chip and a printed circuit board, the image sensor chip is located in the hollow area of the printed circuit board in a suspended mode and is electrically connected to the printed circuit board only through a metal wire. The overall thickness of the optical fingerprint recognition module is smaller than the thickness of an existing module, the optical fingerprint recognition module can be suitable for a portable electronic device, the height of the module is reduced while the imaging effect is guaranteed, and high integration and high density of electronic devices are achieved.

Owner:GALAXYCORE SHANGHAI

Integrated circuit chip packaging structure and manufacturing method thereof

ActiveCN109360814AExtended operating temperature rangeAvoid failureSemiconductor/solid-state device detailsSolid-state devicesWorking temperatureEngineering

The invention discloses an integrated circuit chip packaging structure. An integrated circuit on a chip comprises a temperature sensitive circuit, the failure probability of the temperature sensitivecircuit is increased when working temperature is reduced, the packaging structure comprises a heat conduction layer and a heat insulating layer, the heat conduction layer completely wraps the front and the side surface of the temperature sensitive circuit, the heat insulating layer is formed on the surface of the heat conduction layer and wraps the heat conduction layer, the heat conduction layerforms a structure, the temperatures of various positions of areas wrapped by the heat conduction layer are uniformed by the structure, the heat insulating layer forms a structure, the structure for preventing areas wrapped by the heat insulating layer from cooling, so that the temperatures of the areas wrapped by the heat insulating layer are kept by the structure, and lower temperature end of a working temperature range of the chip can be widened. The invention further discloses a manufacturing method of the integrated circuit chip packaging structure. According to the structure, heat loss ofthe chip can be reduced, and customer loss caused by abnormity of an integrated circuit at excessively low temperature is avoided.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP