LDMOS (Laterally Diffused Metal Oxide Semiconductor) with selective shallow slot through hole and production method thereof

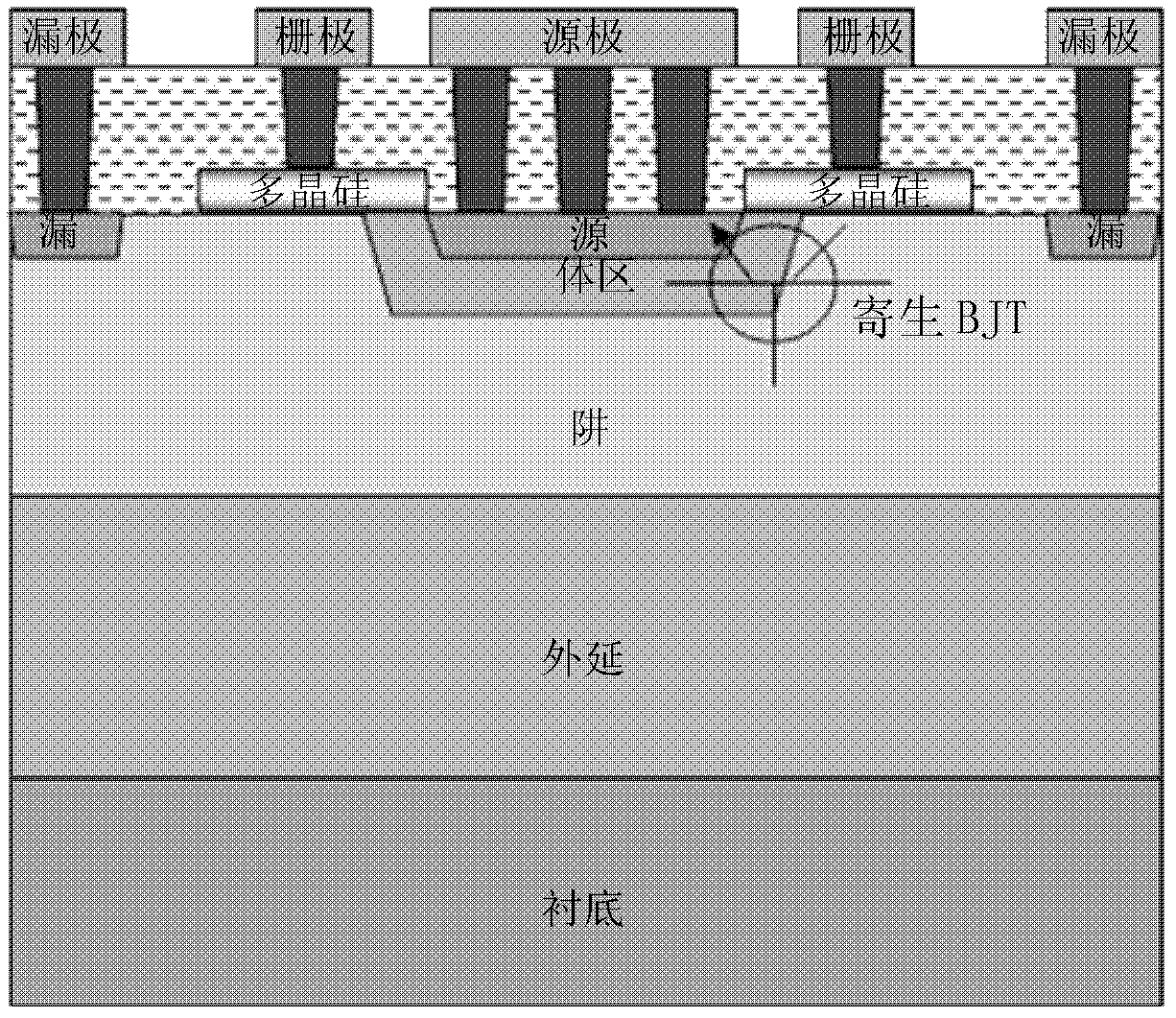

A selective, shallow trench technology, applied in the structure and preparation of LDMOS, can solve the problems of easy damage, lower reliability of LDMOS, lower reverse breakdown voltage of LDMOS, etc., achieve large process window, reduce design size and The effect of chip area and reliability risk reduction

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0026] In order to have a more specific understanding of the technical content, characteristics and effects of the present invention, now in conjunction with the illustrated embodiment, the details are as follows:

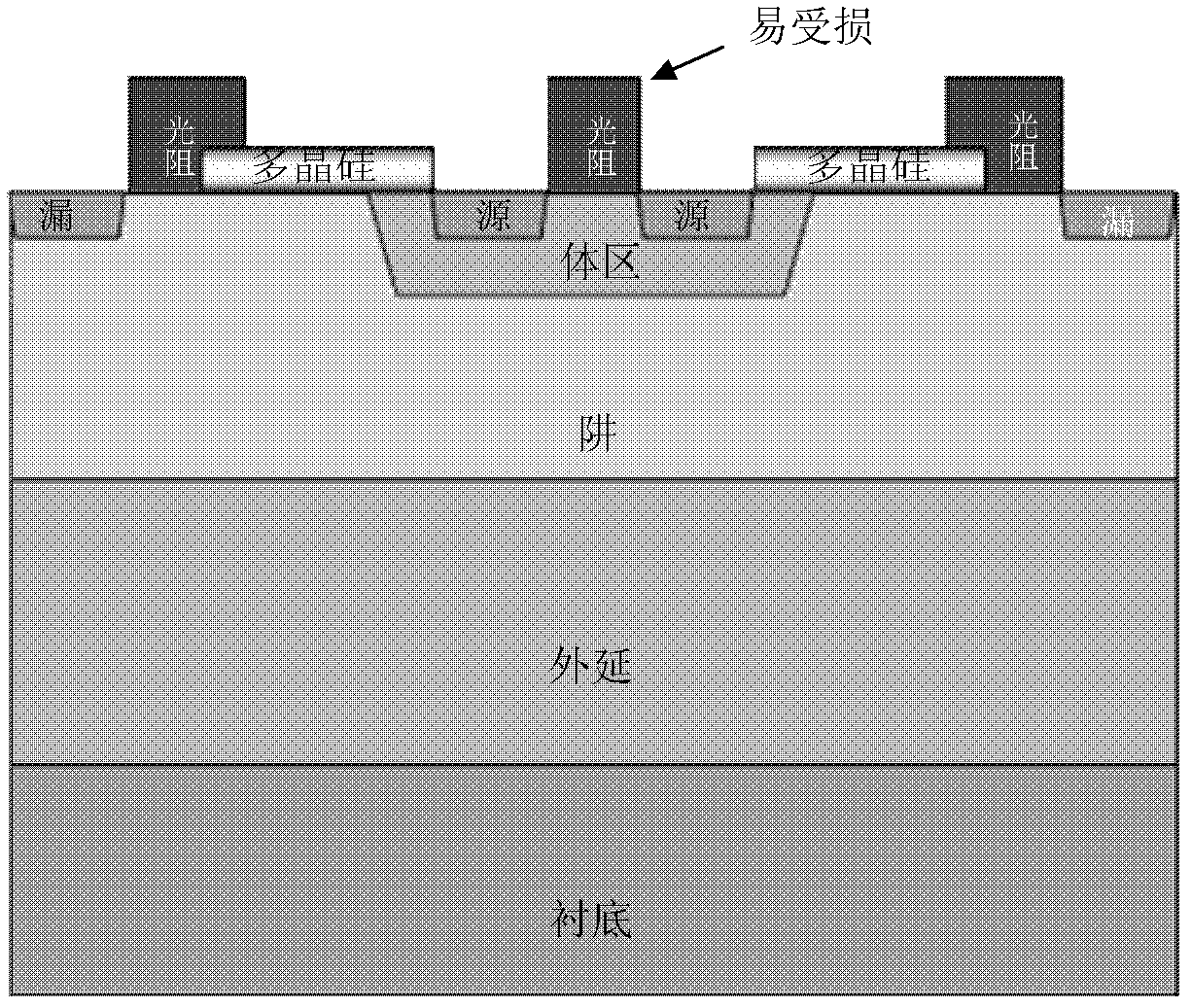

[0027] The selective shallow trench via technology uses different etching rates for different materials to form shallow trench vias in specific areas while forming normal vias in other areas. In this embodiment, the selective shallow trench via technology is applied, and the LDMOS with selective shallow trench via is developed according to the following preparation process:

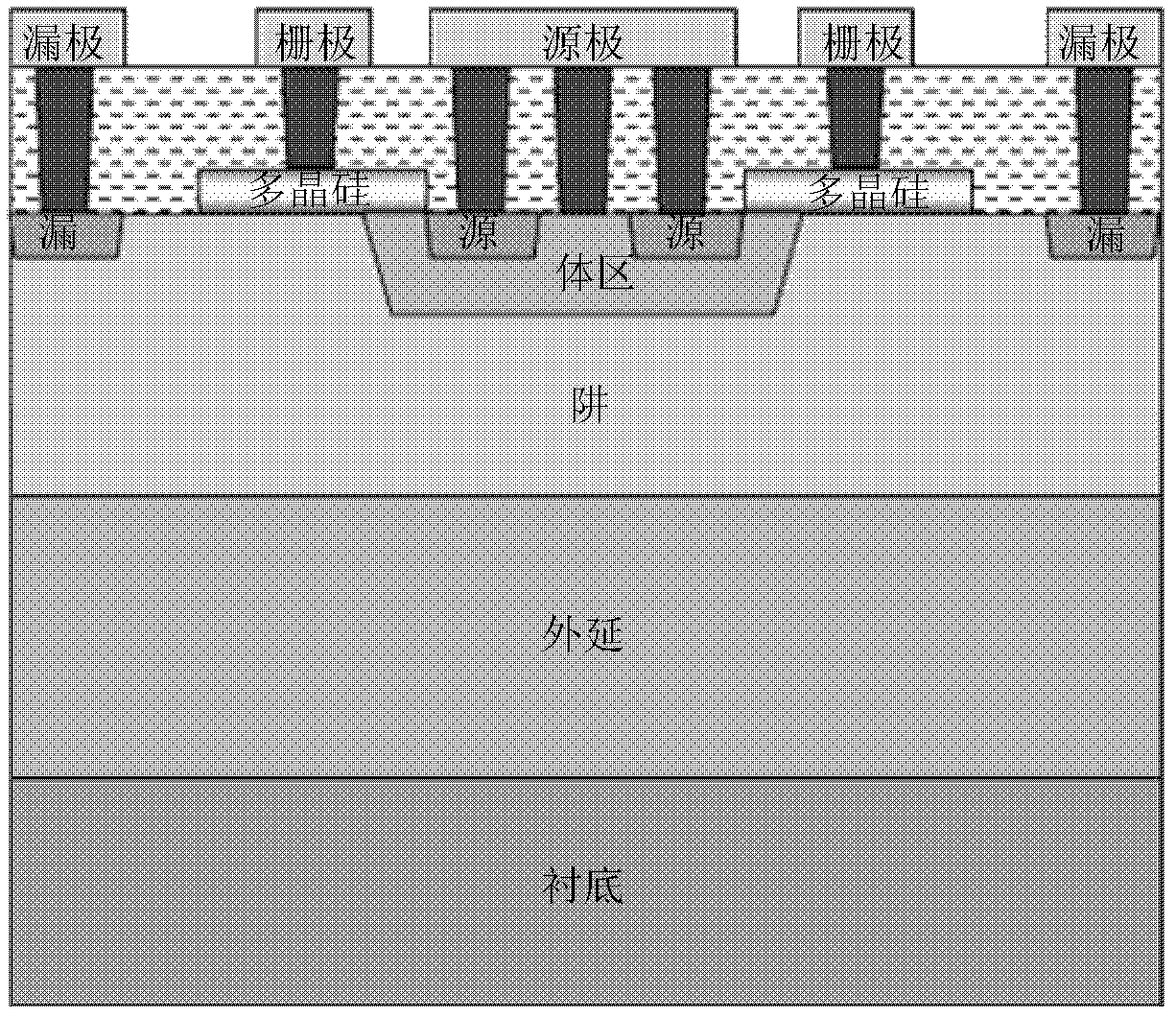

[0028] Step 1, grow an epitaxial layer on a silicon substrate, make a well on the epitaxial layer, deposit a layer of polysilicon, etch to form a gate, and then form a body region, a source region, and a drain region (no need to define homotype doping with the body region region), complete the front-end preparation process of LDMOS semiconductor, and form the basic structure of LDMOS, such as ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More