Wafer-level packaging method and packaging structure thereof

A wafer-level packaging and wafer technology, which is applied in the manufacture of electrical components, electrical solid-state devices, semiconductor/solid-state devices, etc., can solve the problems of low density of input and output ports, large packaging volume, and poor reliability, so as to improve production capacity, The effect of small package size and thin package thickness

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0036] Specific embodiments of the present invention will be described in detail below in conjunction with the accompanying drawings.

[0037] In one embodiment of the wafer level packaging method involved in the present invention, it comprises the following steps:

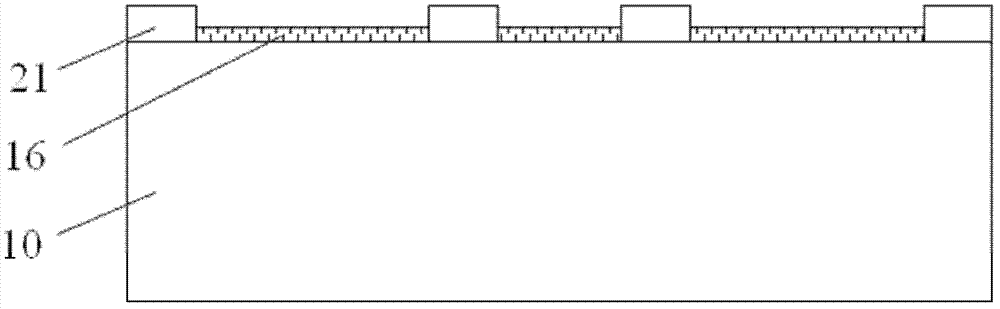

[0038] First, a wafer 10 comprising chip units (not shown) is provided; see figure 1 , perform the first bumping process (Bumping) and the second passivation treatment on the front side of the wafer; the first bumping process can use known methods in the industry such as electroplating, sputtering, or chemical replacement, and copper, The first bump 21 of materials such as nickel, antimony, gold or tin is grown on the front of the wafer; and the secondary passivation treatment generally involves growing a secondary passivation layer 16 on the front of the wafer, wherein the secondary passivation layer 16 can be polyimide film etc.;

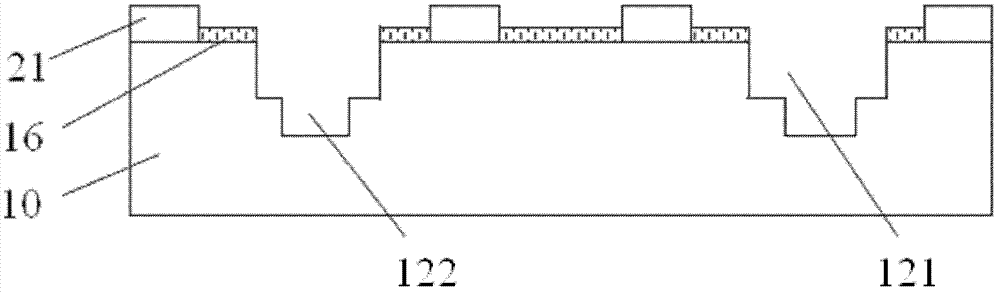

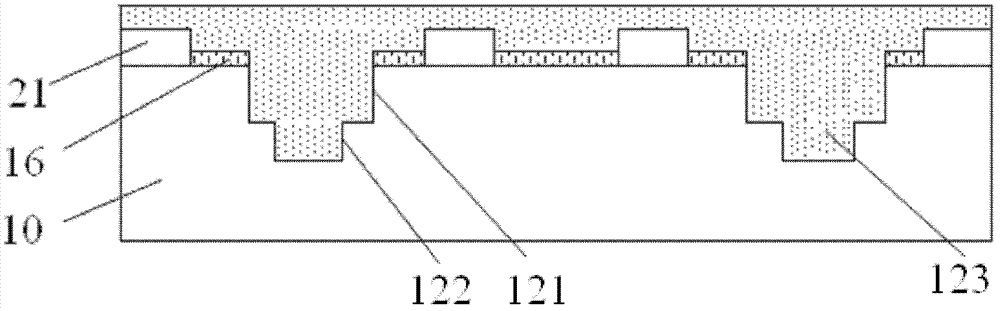

[0039] Please see figure 2 , perform two grooves between adjacent bumps of ad...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More