Hafnium-oxynitride-based low-power consumption resistive random access memory and preparation method for same

A technology of resistive memory and hafnium oxynitride, which is applied in the field of microelectronics, can solve the problems of large reset current and power consumption, and achieve the effects of reducing reset current, reducing power consumption and increasing resistance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

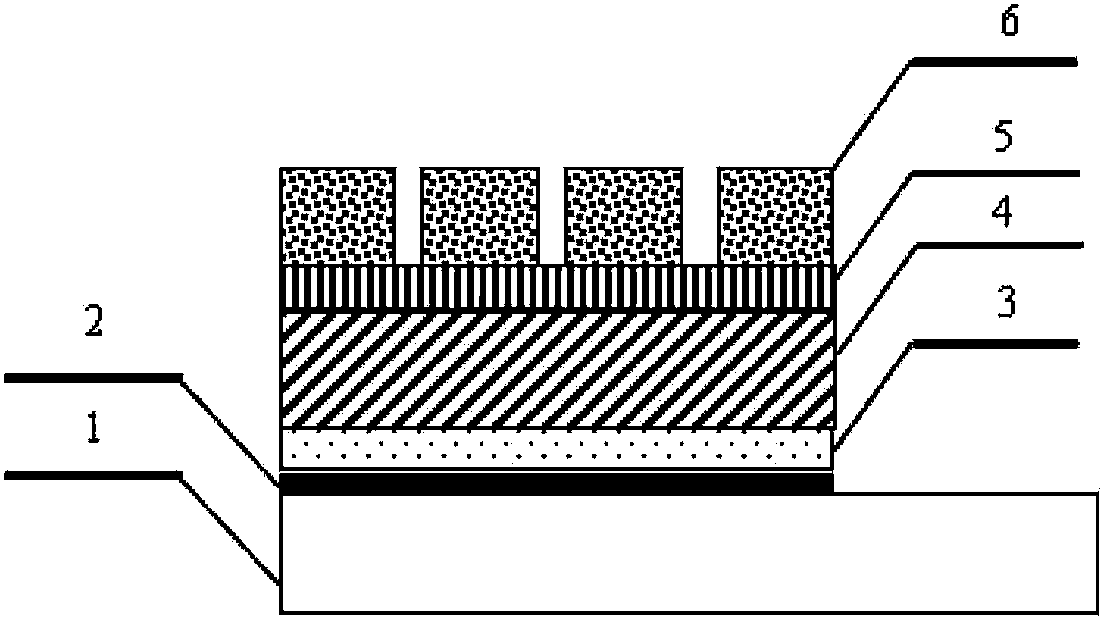

[0030] A low-power resistive memory based on hafnium oxynitride, its structure is as follows figure 1 As shown, by silicon oxide substrate 1, 5nm thick Ti adhesion layer 2, 100nm thick Pt as the lower electrode 3, 50nm thick hafnium oxynitride 4, 10nm thick metal hafnium thin film 5 and 100nm thick Pt as The upper electrode 6 constitutes.

[0031] The preparation method of the resistive memory, the steps are as follows:

[0032] 1) The silicon oxide wafer is used as the substrate, and the silicon oxide wafer is SiO on the surface after the silicon is oxidized. 2 Oxide silicon wafer;

[0033] 2) Prepare a 5nm thick Ti adhesion layer on a silicon oxide wafer by ion beam sputtering;

[0034] 3) Deposit 100nm thick Pt as the bottom electrode by electron beam evaporation process;

[0035] 4) A 50nm-thick hafnium oxynitride film was prepared on the lower electrode by reactive magnetron sputtering. The sputtering process conditions were: metal hafnium target sputtering target wit...

Embodiment 2

[0042] A low-power resistive memory based on hafnium oxynitride and its preparation method, its structure is as follows figure 1 As shown, a silicon oxide substrate 1, a 5nm thick Ti adhesion layer 2, a 100nm thick TiN as the lower electrode 3, a 50nm thick hafnium oxynitride 4, a 10nm thick metal hafnium thin film 5 and a 100nm thick TiN It is formed as the upper electrode 6 .

[0043] The preparation method of the resistive memory, the steps are as follows:

[0044] 1) The silicon oxide wafer is used as the substrate, and the silicon oxide wafer is SiO on the surface after the silicon is oxidized. 2 Oxide silicon wafer;

[0045] 2) Prepare a 10nm-thick Ti adhesion layer on the silicon oxide wafer by ion beam sputtering;

[0046] 3) A 100nm-thick TiN lower electrode was deposited on the Ti adhesion layer by DC reactive magnetron sputtering. The sputtering process: the target intercept was 6.5cm, and the background vacuum was 5×10 -4 Pa, the working pressure is 0.5Pa, the sp...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More