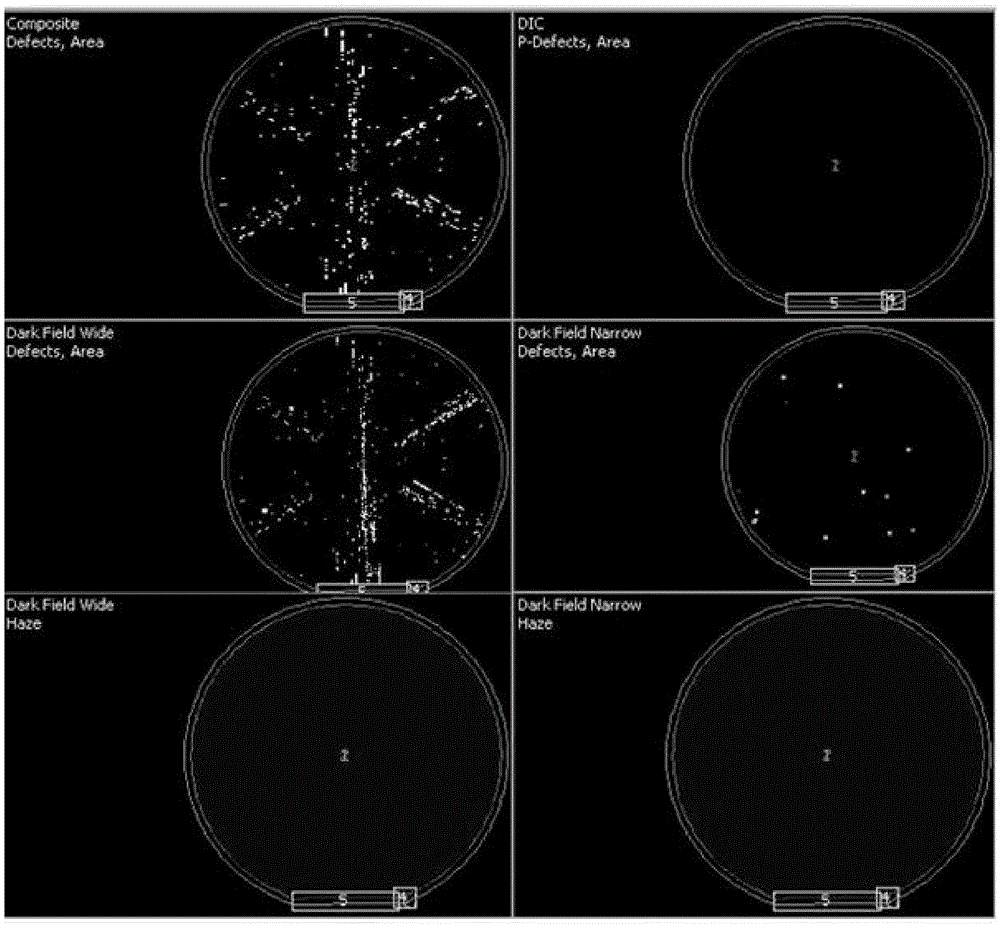

Preparation method of p-layer silicon epitaxial wafer on p++ substrate

A technology of silicon epitaxial wafers and substrates, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve problems such as drastic changes, increased leakage current, device failure, etc., to increase the uniformity of resistivity , increase control costs, and alleviate the effects of lattice changes

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0041] (1) Use P+ / Boron single-sided polishing sheet, resistivity 0.004~0.0075Ω·cm, thickness 525±15μm, silicon wafer diameter 125±0.2mm, back LTO back seal, edge removal width ≤1mm;

[0042] (2) HCl in-situ polishing is performed at 1100°C, the HCl flow rate is 5slm / 10min, and the removal amount on the surface of the silicon wafer is 0.3 microns;

[0043] (3) Purge: use H 2 Purge the reaction chamber for 8 minutes, and discharge the impurities generated after the surface of the silicon wafer is polished out of the chamber, H 2 The flow rate is 140slm / 10min;

[0044] (4) Double-layer epitaxial growth: using high-purity SiHCl 3 Deposition and growth of resistivity graded layer, growth rate 0.40μm / min, growth temperature 1070°C, resistivity gradient layer thickness 1.4μm; then growth resistivity doped layer, growth temperature 1070°C, growth rate controlled at 0.8μm / min.

Embodiment 2

[0046] (1) Use P+ / Boron single-sided polishing sheet, resistivity 0.004~0.0075Ω·cm, thickness 525±15μm, silicon wafer diameter 125±0.2mm, back LTO back seal, edge removal width ≤1mm;

[0047] (2) HCl in-situ polishing is performed at 1130°C, the HCl flow rate is 5slm / 10min, and the removal amount on the surface of the silicon wafer is 0.4 microns;

[0048] (3) Purge: use H 2 Purge the reaction chamber for 10 minutes, and discharge the impurities generated after the surface of the silicon wafer is polished out of the chamber, H 2 The flow rate is 130slm / 10min;

[0049] (4) Double-layer epitaxial growth: using high-purity SiHCl3 Deposition and growth of the resistivity graded layer, the growth rate is 0.38μm / min, the growth temperature is 1080°C, the thickness of the resistivity gradient layer is 1.5μm; then the resistivity doped layer is grown, the growth temperature is 1100°C, and the growth rate is controlled at 1.0μm / min.

Embodiment 3

[0051] (1) Use P+ / Boron single-sided polished sheet, resistivity 0.004~0.0075Ω·cm, thickness 525±15μm, silicon wafer diameter 125±0.2mm, back LTO back seal, edge removal width ≤1mm;

[0052] (2) HCl in-situ polishing is performed at 1120°C, the HCl flow rate is 5slm / 10min, and the removal amount on the surface of the silicon wafer is 0.3 microns;

[0053] (3) Purge: use H 2 Purge the reaction chamber for 11 minutes, and discharge the impurities generated after the surface of the silicon wafer is polished out of the chamber, H 2 The flow rate is 170slm / 10min;

[0054] (4) Double-layer epitaxial growth: using high-purity SiHCl 3 Deposition and growth of the resistivity gradient layer, the growth rate is 0.42μm / min, the growth temperature is 1100°C, the thickness of the resistivity gradient layer is 1.3μm; then the resistivity doped layer is grown, the growth temperature is 1080°C, and the growth rate is controlled at 0.9μm / min.

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More