Linear equalizer

A linear equalizer, inverter technology, applied in baseband system components, shaping networks in transmitter/receiver, etc., can solve the skin effect and transmission medium impedance discontinuity, dielectric loss, bandwidth limitation, etc. problem, to achieve the effect of increasing bandwidth, reducing common mode interference, and improving equalization performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

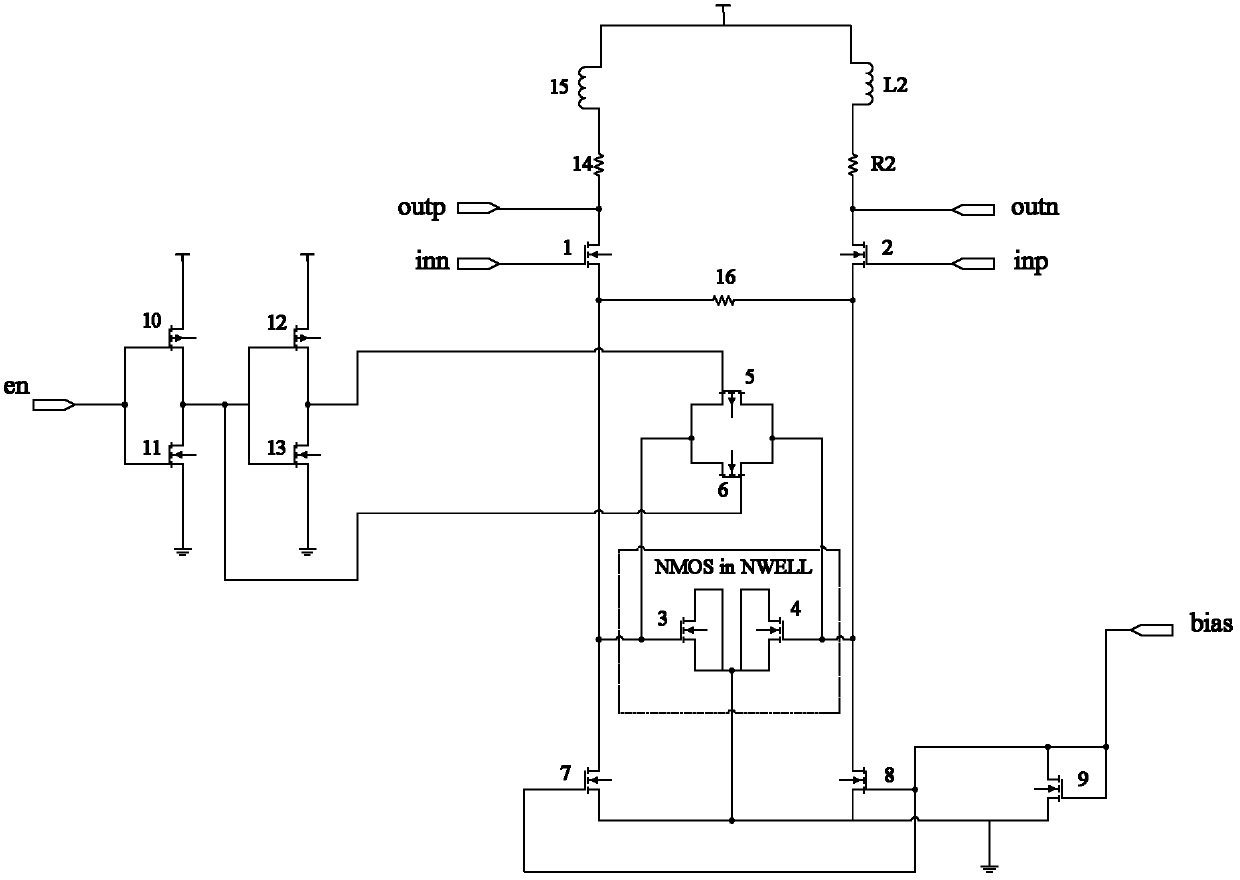

[0023] Such as figure 2 Shown is a schematic structural diagram of a linear equalizer according to an embodiment of the present invention. The linear equalizer of the embodiment of the present invention includes:

[0024] A differential input pair is composed of a first MOS transistor 1 and a second MOS transistor 2, and both the first MOS transistor 1 and the second MOS transistor 2 are NMOS transistors. The gates of the first MOS transistor 1 and the second MOS transistor 2 are respectively input terminals of a pair of differential input signals inn and inp, and the drains of the first MOS transistor 1 and the second MOS transistor 2 are respectively a pair of The output terminals of the differential output signals outn and outp, the sources of the first MOS transistor 1 and the second MOS transistor 2 are respectively connected to a current source.

[0025] A first resistor 14 and a first inductor 15 are connected in series between the drain of the first MOS transistor 1...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More