Method for manufacturing grid side wall of ONO structure

A gate sidewall and manufacturing method technology, applied in semiconductor/solid-state device manufacturing, gaseous chemical plating, coating and other directions, can solve the thickness uniformity difference of semiconductor substrate thickness uniformity, unsatisfactory step coverage, Affect the performance of semiconductor devices and other issues, and achieve the effect of high step coverage, good intra-chip uniformity and inter-chip uniformity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

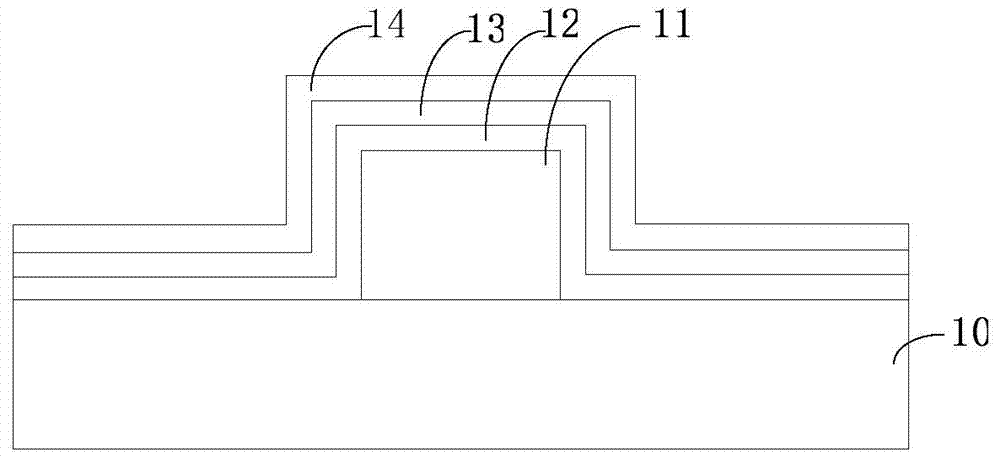

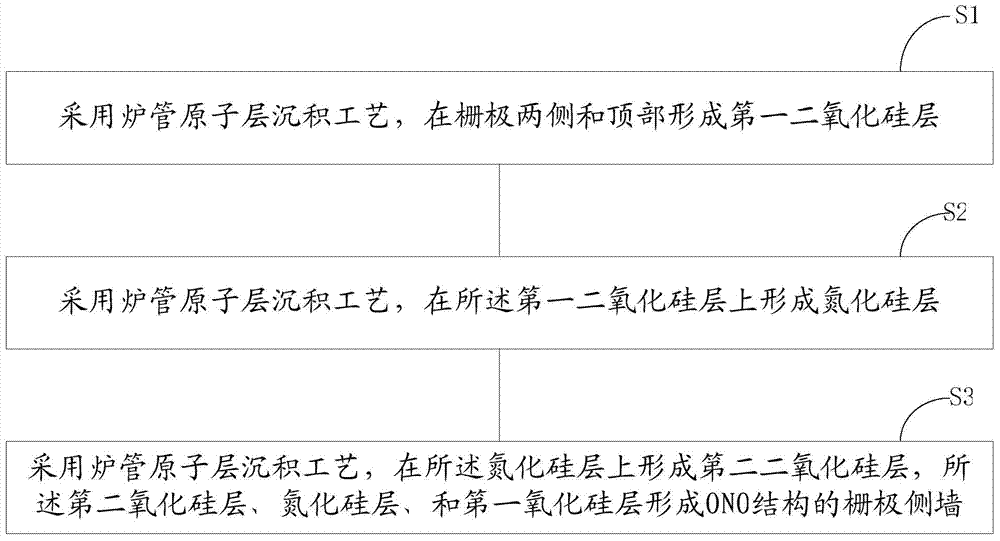

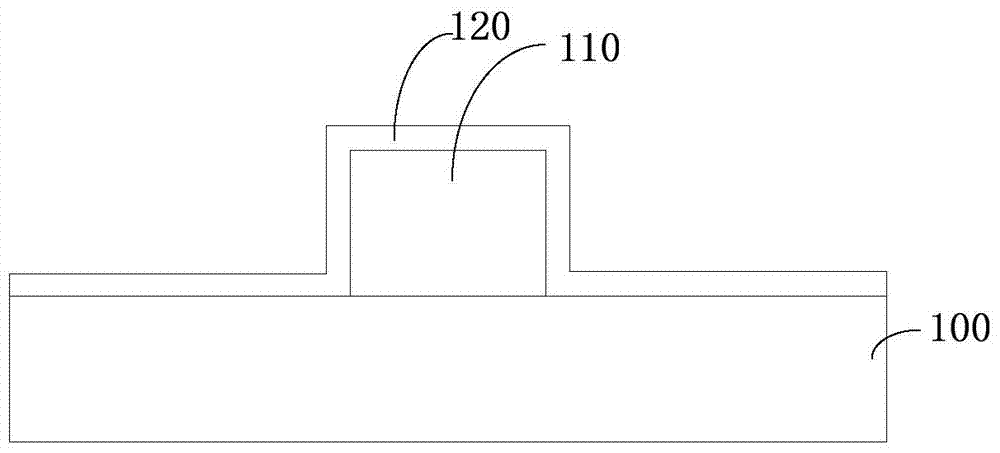

[0028] In the prior art, the first silicon oxide layer and the second silicon oxide layer are made by the furnace tube TEOS process or the furnace tube high-temperature thermal oxidation process, and the silicon nitride process is made by the furnace tube DCS NH3 process. The uniformity of the process is not high, and the step coverage is not good. In order to solve the above problems, the present invention proposes a method for manufacturing the gate sidewall structure of the ONO structure. Please refer to figure 2 The schematic flow chart of the manufacturing method of the gate sidewall of the ONO structure shown in the prior art, the method includes:

[0029] Step S1, using a furnace tube atomic layer deposition process to form a first silicon dioxide layer on both sides and top of the gate;

[0030] Step S2, using a furnace tube atomic layer deposition process to form a silicon nitride layer on the first silicon dioxide layer;

[0031] Step S3, using a furnace tube atomi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More