Method for manufacturing junction barrier schottky diode through selective oxidation of silicon

A junction barrier Schottky and selective oxidation technology, which is applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve the problem of reducing forward current, reducing the function and efficiency of forward conduction current, and the area of conduction current Smaller and other problems, to achieve the effect of compensating area, improving function and efficiency, and increasing conductive area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0028] A method for manufacturing a junction barrier Schottky diode using a silicon selective oxidation technique, comprising a crystal generating step and a packaging step, wherein the crystal generating step includes:

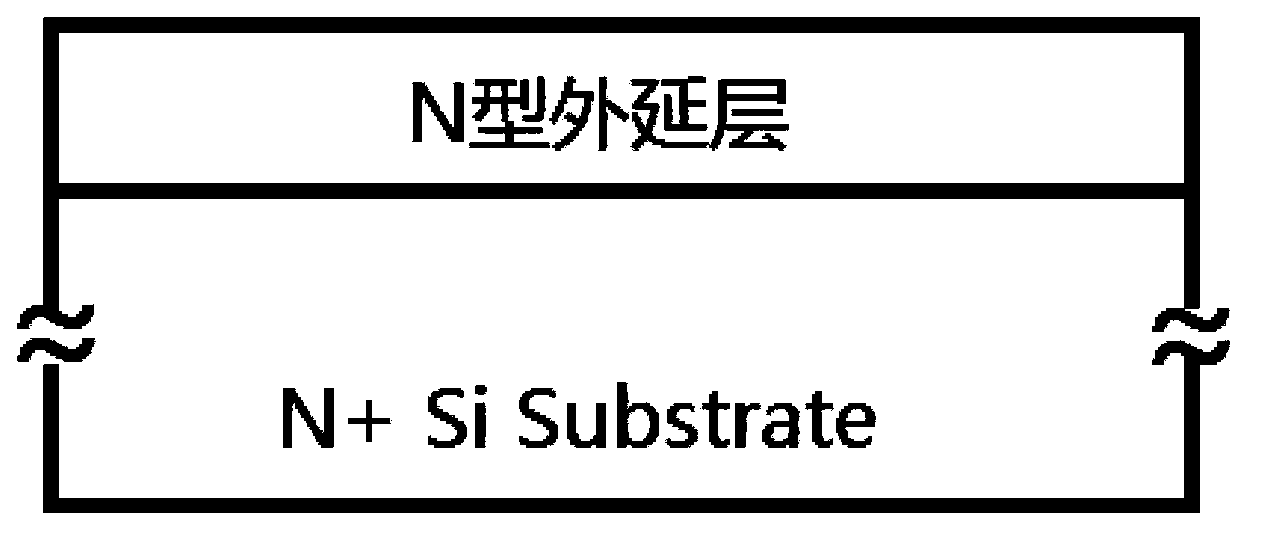

[0029] (1) An N-type silicon epitaxial layer is covered on the N+ type silicon wafer substrate. like figure 1 shown.

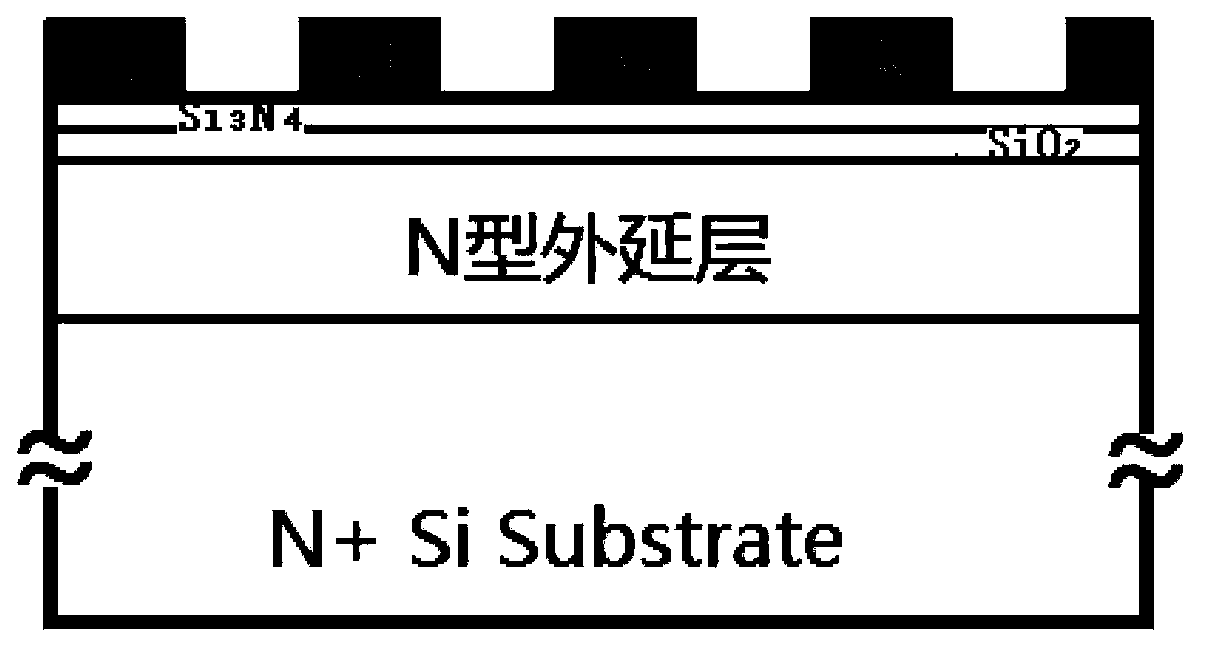

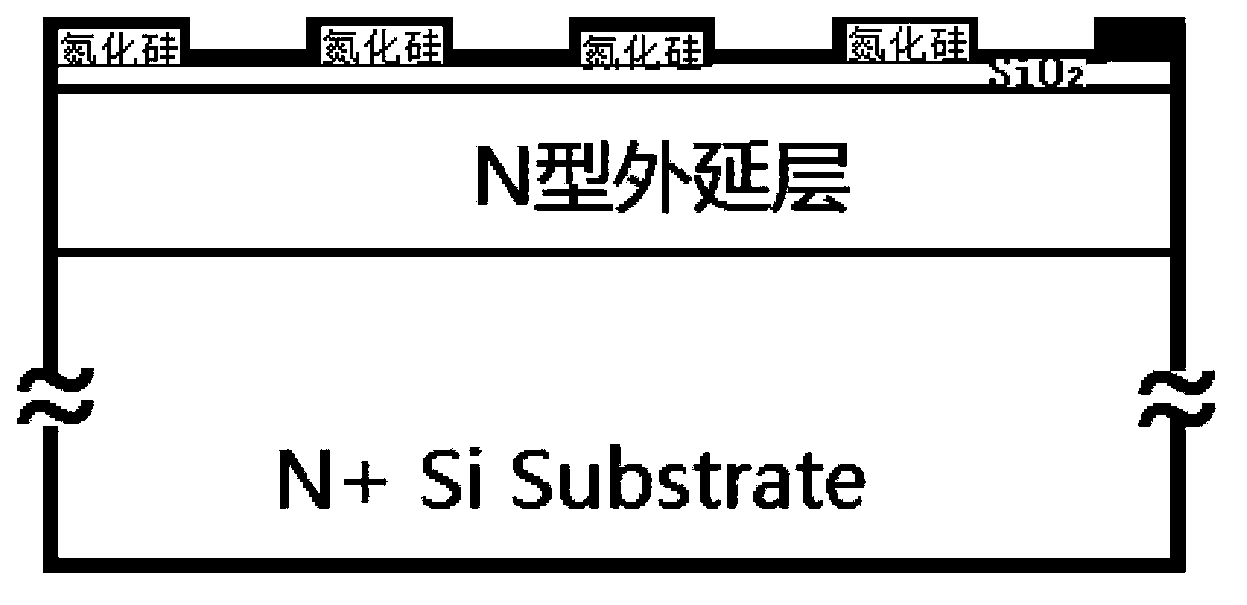

[0030] (2) A thin layer of silicon oxide is first grown on the N-type silicon epitaxial layer, and a layer of silicon nitride is deposited on it; and the thickness of silicon oxide is smaller than that of silicon nitride. In this embodiment, the silicon oxide is SiO 2 , its thickness is about 300 Angstroms; the silicon nitride is Si 3 N 4 , and its thickness is about 2000 Angstroms.

[0031] (3) A plurality of block photoresist regions are formed on the surface of the silicon nitride layer by photolithography, and these block photoresist regions are independently distributed and cover the surface of the silicon nitride layer. like fi...

Embodiment 2

[0043] In Embodiment 2, the N-type and P-type of Embodiment 1 can be exchanged to obtain a barrier junction Schottky diode with P+ type substrate, P-type epitaxial layer and N-type ion implantation, such as Figure 10 shown. which is

[0044]A method for manufacturing a junction barrier Schottky diode using a silicon selective oxidation technique, comprising a crystal generating step and a packaging step, wherein the crystal generating step includes:

[0045] (1) Cover a P-type silicon epitaxial layer on the P+ type silicon wafer substrate; figure 1 shown.

[0046] (2) A thin layer of silicon oxide is first grown on the P-type silicon epitaxial layer, and then a layer of silicon nitride is deposited on it; and the thickness of silicon oxide is smaller than that of silicon nitride. In this embodiment, the silicon oxide is SiO 2 , its thickness is about 300A; the silicon nitride is Si 3 N 4 , and its thickness is about 2000A. The above 1A=10 -4 u.

[0047] (3) A plural...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More