How to make a mos transistor

A technology of a MOS transistor and a manufacturing method, which is applied to the manufacturing field of MOS transistors, can solve problems such as poor performance of PMOS transistors, and achieve the effects of easy removal steps and improved performance.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

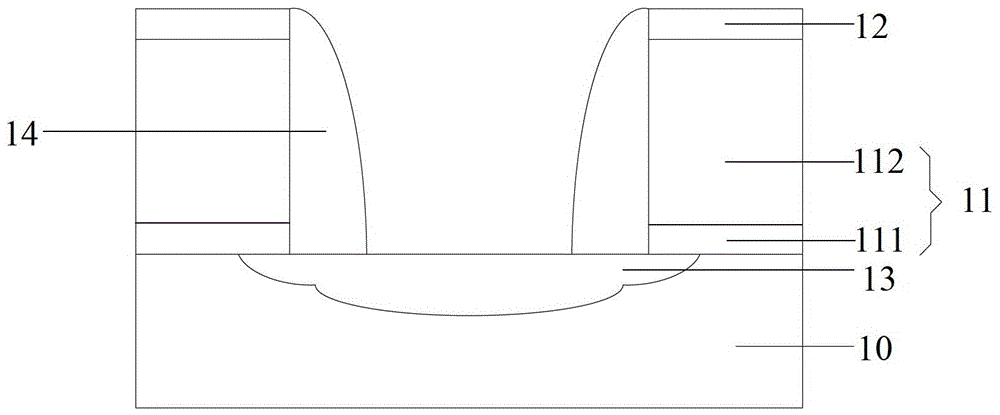

[0040] After research, the inventor found that the reasons for the poor performance of PMOS transistors are:

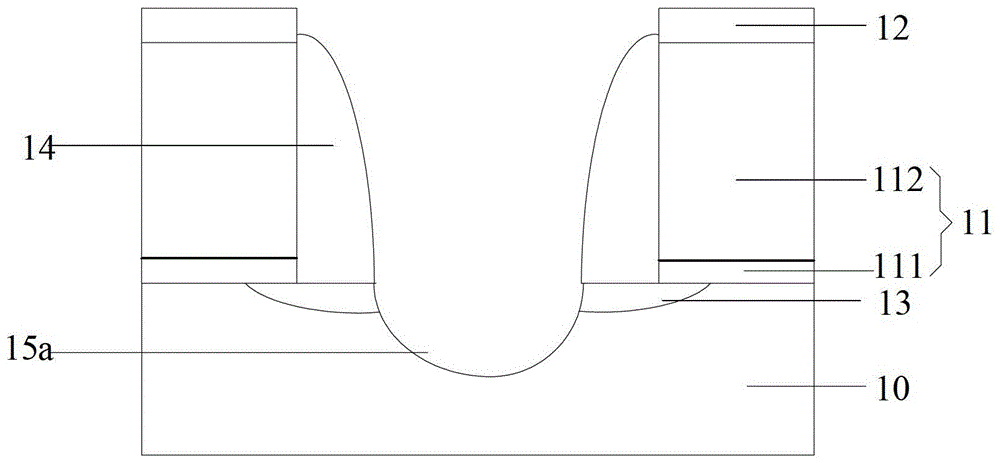

[0041] Please refer to figure 2 The method for forming the sigma-shaped groove includes: using the dummy gate structure 11 and the sidewall 14 as a mask, etching the substrate 10 to form bowl-shaped grooves 15 a in the substrate 10 on both sides of the dummy gate structure 11 . The bowl-shaped groove 15a is formed by using anisotropic dry etching to form rectangular grooves in the substrate 10 on both sides of the dummy gate structure 11, and then using isotropic dry etching to etch the formed grooves. The above-mentioned rectangular groove forms a bowl-shaped groove 15a. The aforementioned anisotropic dry etching and isotropic dry etching cause the first damage to the sidewall 14 , so that the height of the sidewall 14 decreases.

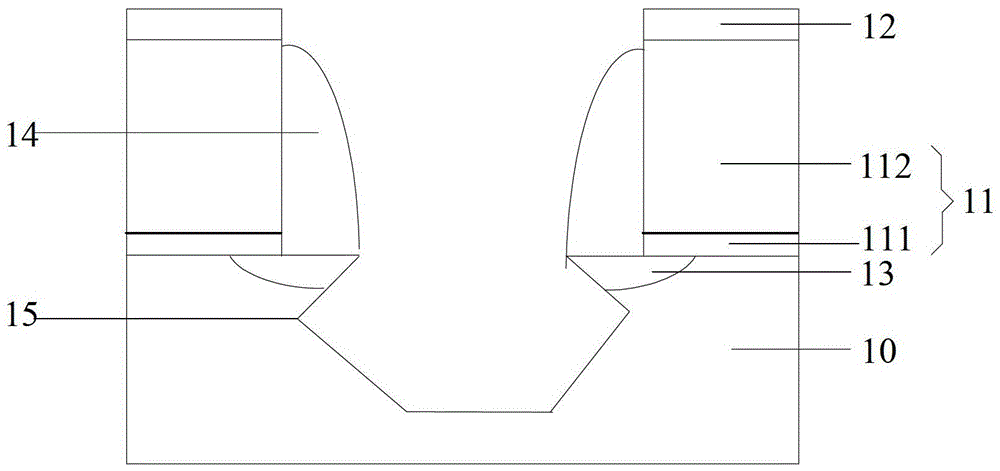

[0042] Please continue to refer figure 2 and image 3 , the bowl-shaped groove 15a is exposed to TMAH (Tetramethyl Ammonium Hydroxi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More