High-performance gating vernier type time digital converter

A time-to-digital converter technology, applied in the field of high-performance gated vernier time-to-digital converters, can solve problems such as τ reduction, comparator false triggering, and boosting, etc., and achieves improved measurement range, improved locking speed, and large measurement range. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0037] The present invention will be described in further detail below in conjunction with the accompanying drawings and embodiments.

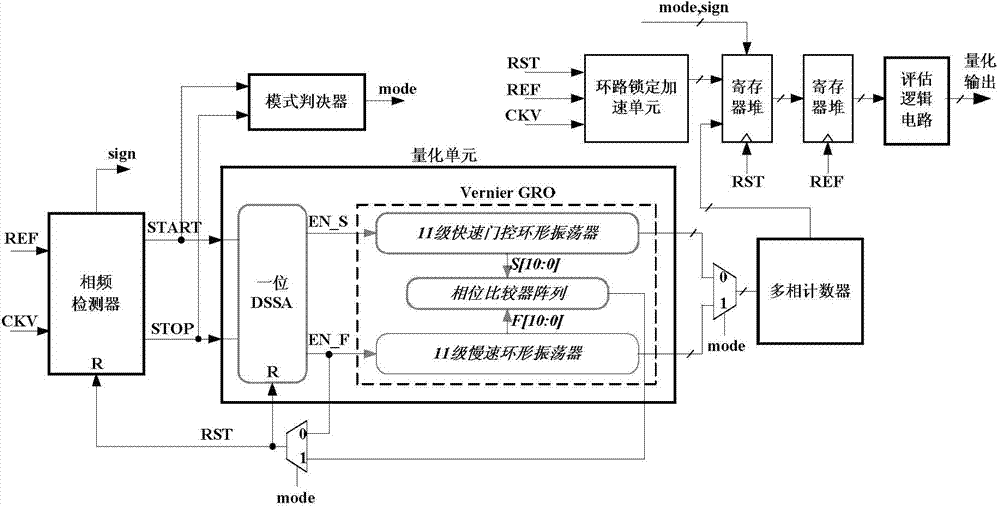

[0038] The main performance index calculation of the gated vernier type time-to-digital converter among the present invention is as follows:

[0039] ① resolution. use τ 1 and τ 2 Represent the delay value of each delay unit in the fast ring oscillation and slow ring oscillation respectively, and the resolution of the coarse quantization mode is determined by τ 1 Determined, the resolution of the fine quantization mode is determined by the delay difference Δt of the two delay units delay Decide.

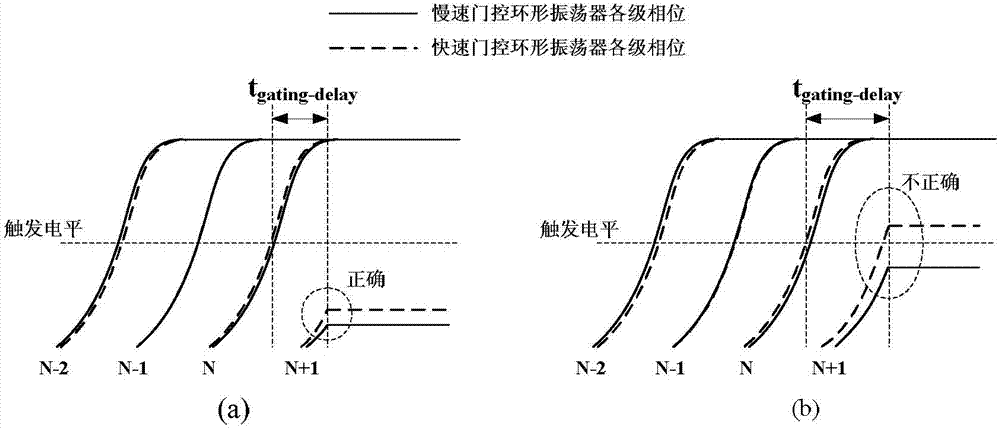

[0040] ②Measurement Range (Measurement Range) t MR . The main factor affecting the measurement range in the fine quantization mode is the oscillation period T of the fast ring oscillation GRO , delay unit τ 2 , Δt delay , reference clock period T REF , and the sum of delay values of PFD, DSSA and reset circuit t sum , its calculation for...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com