Integrated circuit chip with level shift LDMOS embedded in junction terminal and manufacturing method thereof

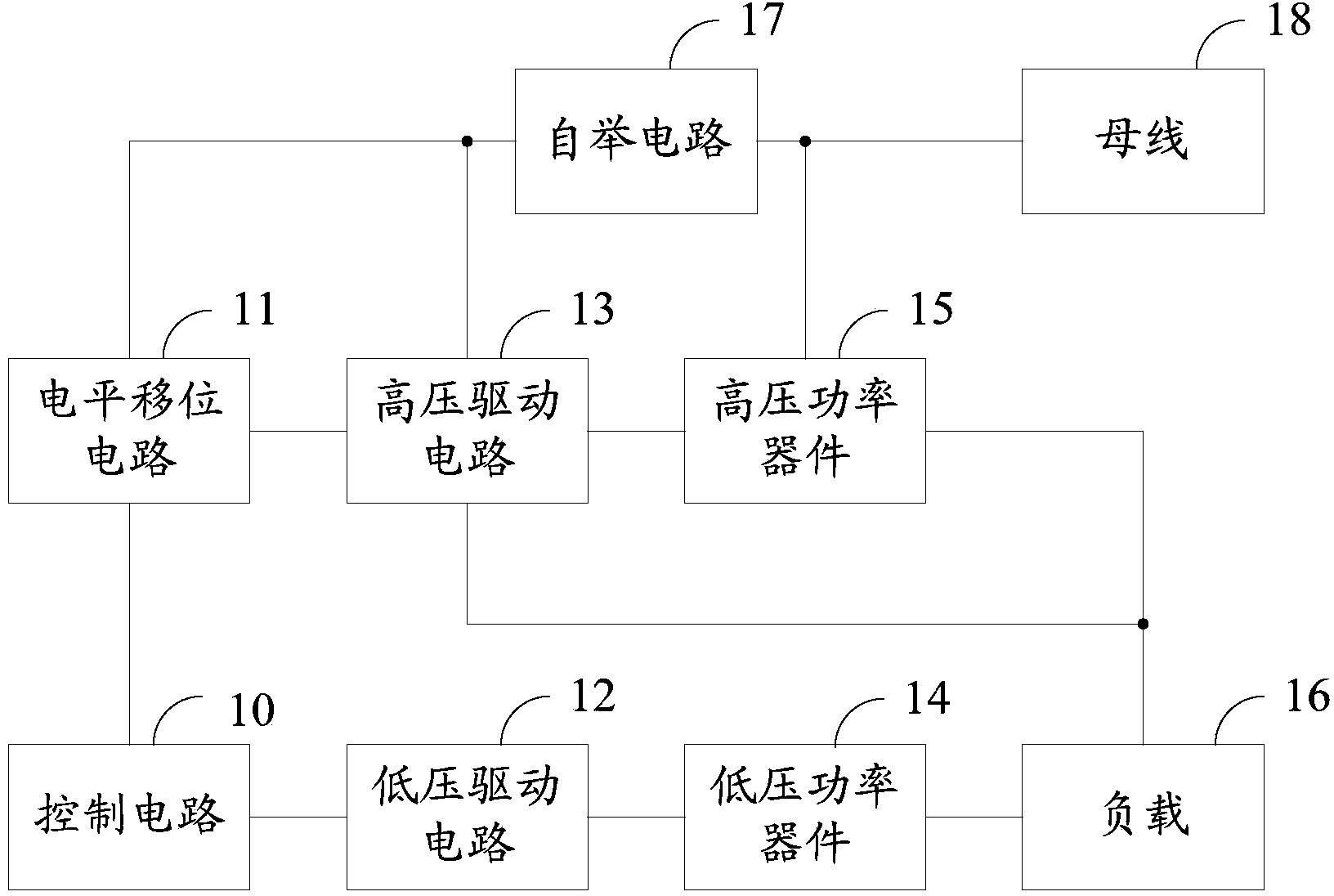

A level shift, integrated circuit technology, applied in circuits, semiconductor/solid-state device manufacturing, electrical components, etc., can solve problems such as reduced reliability and reduced device withstand voltage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

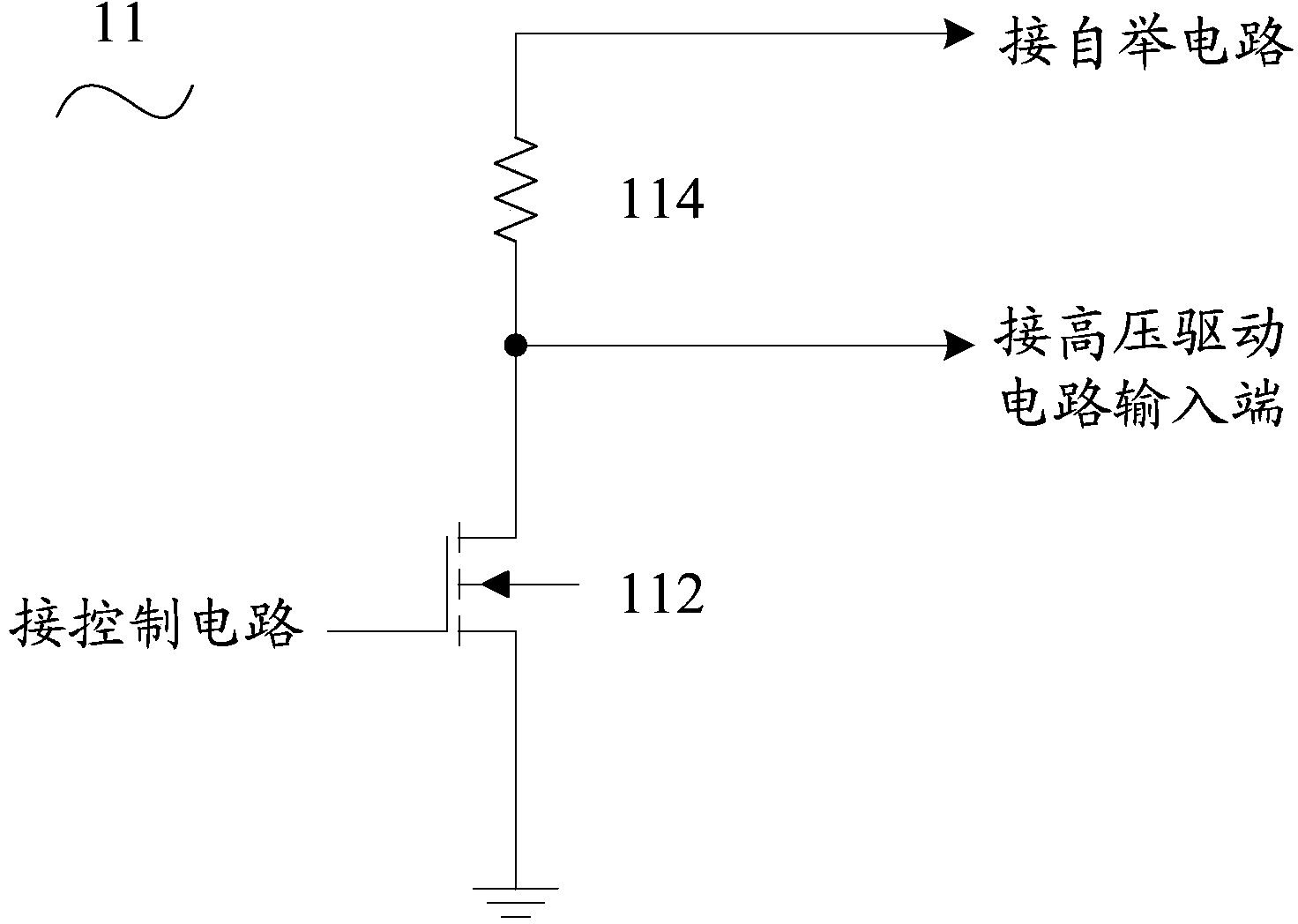

Method used

Image

Examples

Embodiment 1

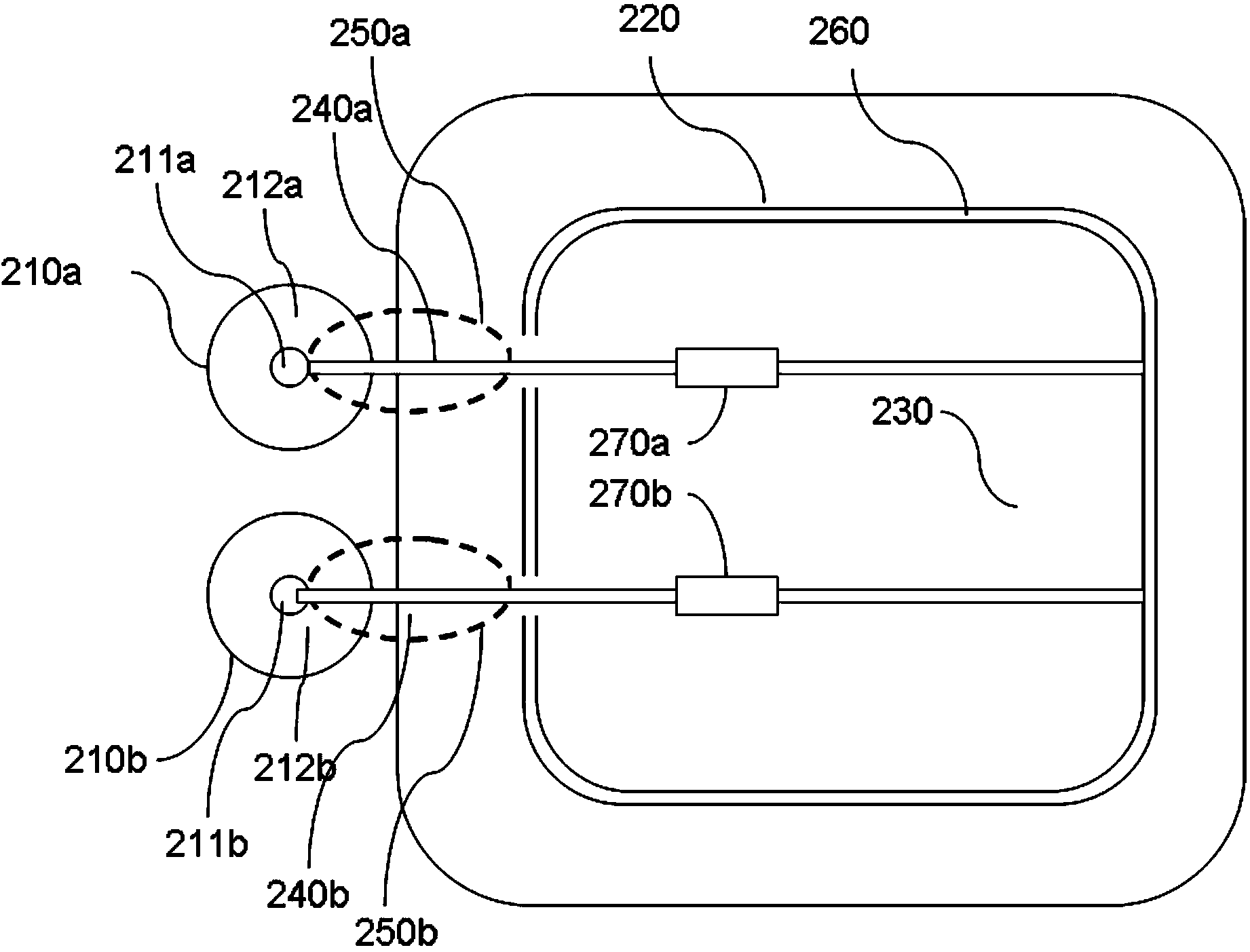

[0042] Figure 5 is an example along Figure 4 The cross-sectional view of the A-B line in the middle includes the P-type substrate 500, the N-type buried layer region in the P-type substrate 500, the P-type depletion region 503a in the P-type substrate 500, the P-type buried layer 503b, and the P-type substrate P-type epitaxial layer 504 on 500, N-type drift region 505a in P-type epitaxial layer 504, shifted N-well 506a, high-basin N-well 506b, high-basin P-well 507c, and displacement on P-type depletion region 503a The isolated P well 507b on the P well 507a and the P-type buried layer 503b shifts the P-type body region 511 (P+ type in this embodiment) and the N-type source region 510a (N+ type in this embodiment) in the P well 507a. type), the N-type drain region 510b (N+ in this embodiment) in the displaced N well 506a, and the bootstrap N region 510c (N+ in this embodiment) in the high-basin N well 506b.

[0043] Specifically, the aforementioned N-type buried layer regi...

Embodiment 2

[0078] Figure 7 It is the second edge of the embodiment Figure 4 The cross-sectional view of the A-B line in the middle includes the P-type substrate 700, the N-type buried layer region in the P-type substrate 700, the P-type depletion region 703a in the P-type substrate 700, the P-type buried layer 703b, and the P-type substrate P-type epitaxial layer 704 on 700, N-type drift region 705a, N-type region 705b, N-type region 705c, high-basin N well 706b, shifted N-well 706a, high-basin P well 707c, The shifted P well 707a on the P-type depletion region 703a, the isolated P well 707b on the P-type buried layer 703b, the shifted P-type body region 711 and the N-type source region 710a in the P-well 707a, and the shifted N-well 706a N-type drain region 710b inside, bootstrap N region 710c in high basin N well 706b, isolation structures 708a, 708b, 708c and 708d, first polysilicon field plate 709, dielectric layer 712, first metal field plate 713a , the second metal field plate ...

Embodiment 3

[0082] Figure 9 is the embodiment of three along Figure 4 The cross-sectional view of the A-B line in the middle includes the P-type substrate 900, the N-type buried layer region in the P-type substrate 900 (specifically including the deep buried layer 901a and the shallow buried layer 902a of the terminal N-type buried layer, and the high-basin N-type buried layer Deep buried layer 901b and shallow buried layer 902b), P-type depletion region 903a, P-type buried layer 903b in P-type substrate 900, P-type epitaxial layer 904 on P-type substrate 900, P-type epitaxial layer 904 N-type drift region 905a, N-type region 905b, N-type region 905c, high-basin N-well 906b, shifted N-well 906a, high-basin P-well 907c, shifted P-well 907a on P-type depletion region 903a, The isolated P well 907b on the P-type buried layer 903b, the P-type body region 911 and the N-type source region 910a in the shifted P-well 907a, the N-type drain region 910b in the shifted N-well 906a, and the high-b...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More