Semiconductor structure and forming method thereof

A semiconductor and conductor technology, applied in the field of ultra-large-scale integrated circuit manufacturing, can solve problems such as complex processes, and achieve the effects of large process window, process compatibility, and low process cost.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

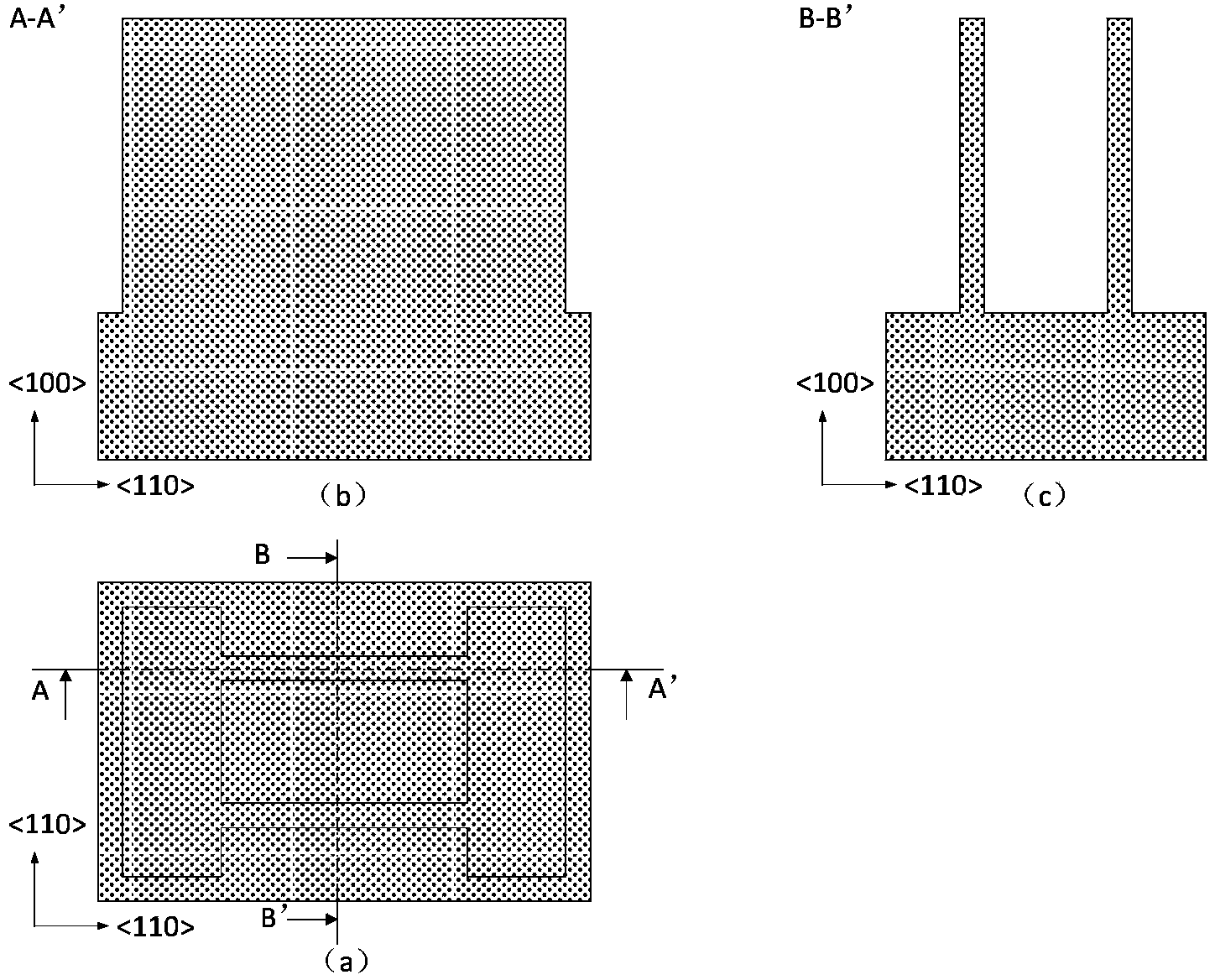

[0068] A two-layer circular nanowire structure with a diameter of about 10 nm can be achieved according to the following steps:

[0069] 1) Thermal growth on (111) bulk silicon substrate SiO 2 As a stress buffer layer between the hard mask and the silicon substrate;

[0070] 2) LPCVD Si 3 N 4 as an etch hard mask;

[0071] 3) Define Fin and the source and drain regions connected to both ends of Fin on the hard mask by photolithography, wherein the width of the Fin structure is 20nm, the length is 300nm, and the length direction and the sidewall crystal direction are both along ;

[0072] 4) Transfer the pattern to the hard mask by anisotropic etching to expose the silicon substrate;

[0073] 5) Transfer the pattern on the hard mask to the silicon substrate by anisotropic etching to form Fin and the source and drain regions connected to both ends of Fin, wherein the height of the Fin structure is The width is 20nm, the length is 300nm, and the length direction and sid...

Embodiment 2

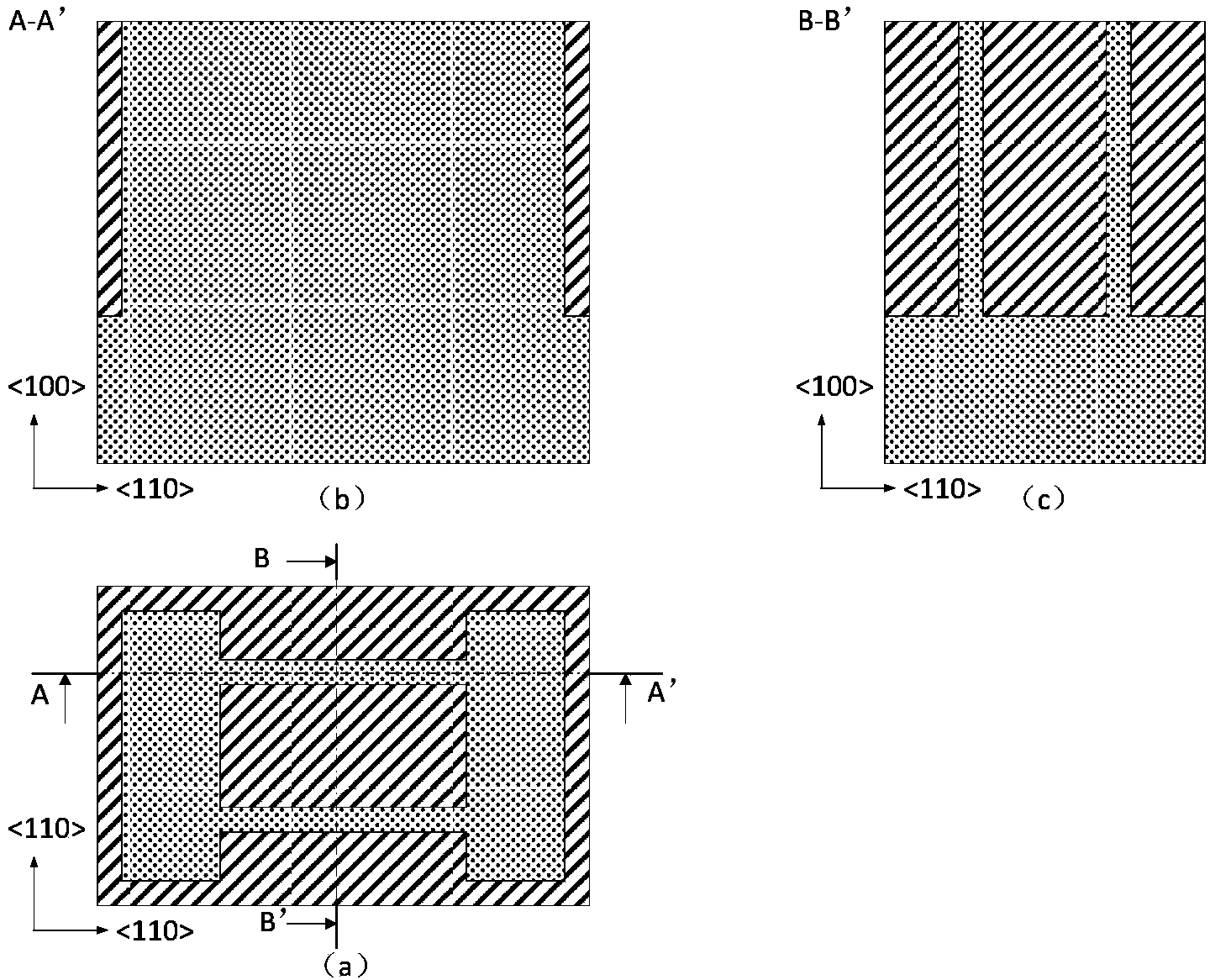

[0097] A two-layer square nanowire structure with a diameter of about 5 nm can be achieved according to the following steps:

[0098] 1) Thermal growth on (100) bulk silicon substrate SiO 2 As a stress buffer layer between the hard mask and the silicon substrate;

[0099] 2) LPCVD Si 3 N 4 as an etch hard mask;

[0100] 3) Define Fin and the source and drain regions connected to both ends of Fin on the hard mask by photolithography. The width of the Fin structure is 10nm, the length is 300nm, the length direction is along , and the sidewall crystal directions are all along ;

[0101] 4) Transfer the pattern to the hard mask by anisotropic etching to expose the silicon substrate;

[0102] 5) Transfer the pattern on the hard mask to the silicon substrate by anisotropic etching to form Fin and the source and drain regions connected to both ends of Fin, wherein the height of the Fin structure is The width is 10nm, the length is 300nm, the length direction is along , and ...

Embodiment 3

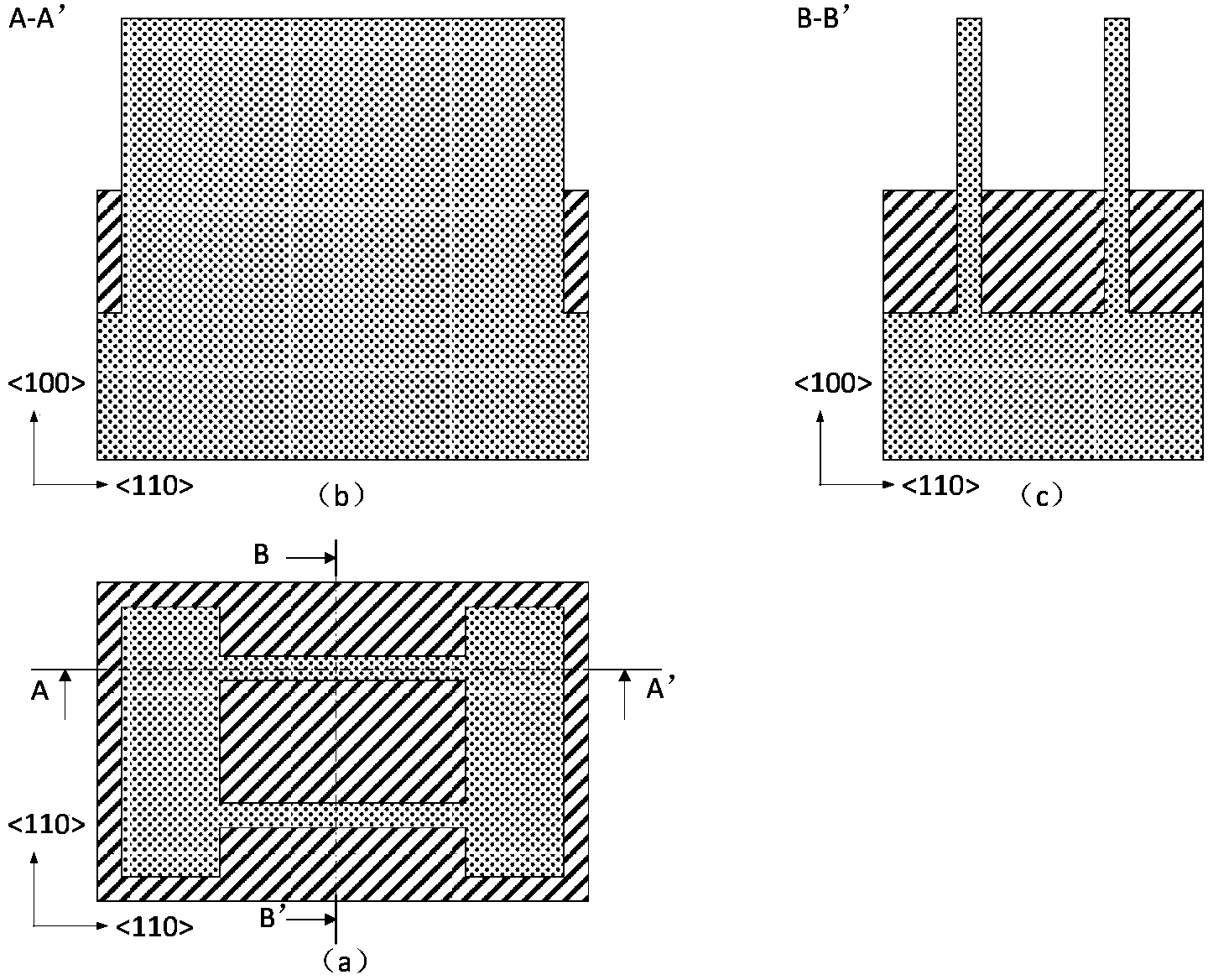

[0125] A three-layer nanowire structure with a diameter of about 10 nm was prepared.

[0126] 1) Thermal growth on (110) bulk silicon substrate SiO 2 As a stress buffer layer between the etched hard mask and the silicon substrate;

[0127] 2) LPCVD Si 3 N 4 as an etch hard mask for silicon;

[0128] 3) Define Fin and the source and drain regions connected to both ends of Fin by photolithography, wherein the width of the Fin structure is 30 nanometers, the length is 300 nanometers, the length direction is along the crystal direction, and the side wall is along the crystal direction;

[0129] 4) Transfer the pattern to the hard mask by anisotropic etching to expose the silicon substrate;

[0130] 5) Transfer the pattern on the hard mask to the silicon substrate by anisotropic etching to form Fin and the source and drain regions connected to both ends of Fin, wherein the height of the Fin structure is The width is 30 nanometers, the length is 300 nanometers, the lengt...

PUM

| Property | Measurement | Unit |

|---|---|---|

| width | aaaaa | aaaaa |

| length | aaaaa | aaaaa |

| width | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More