Patents

Literature

47results about How to "Uniform cross-sectional shape" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

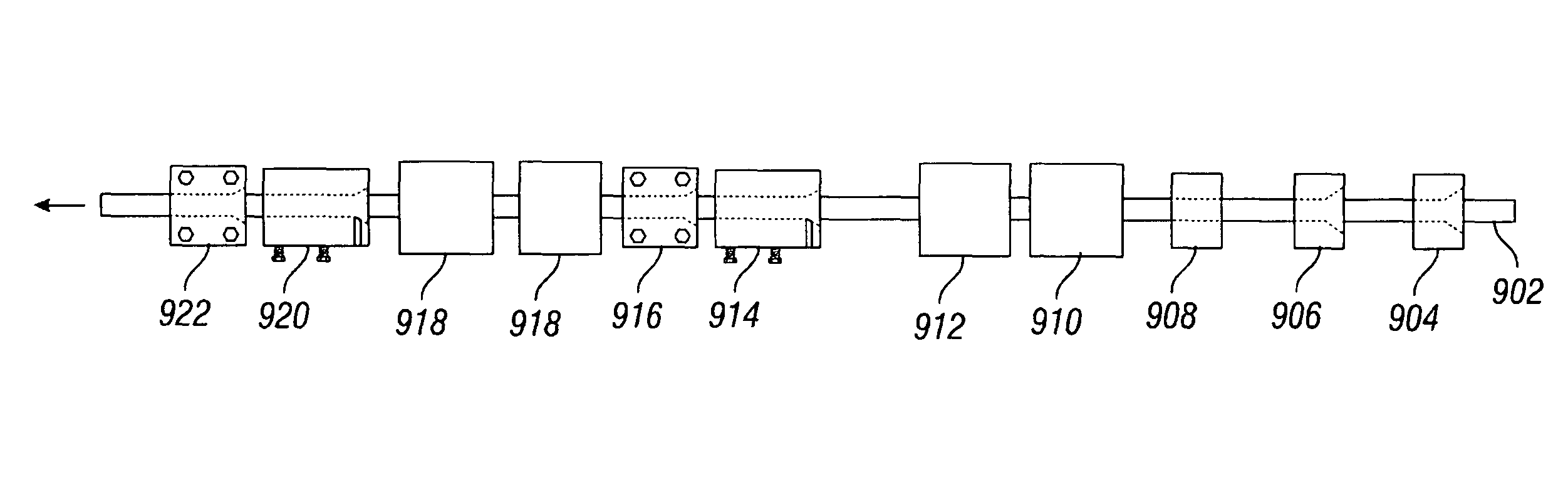

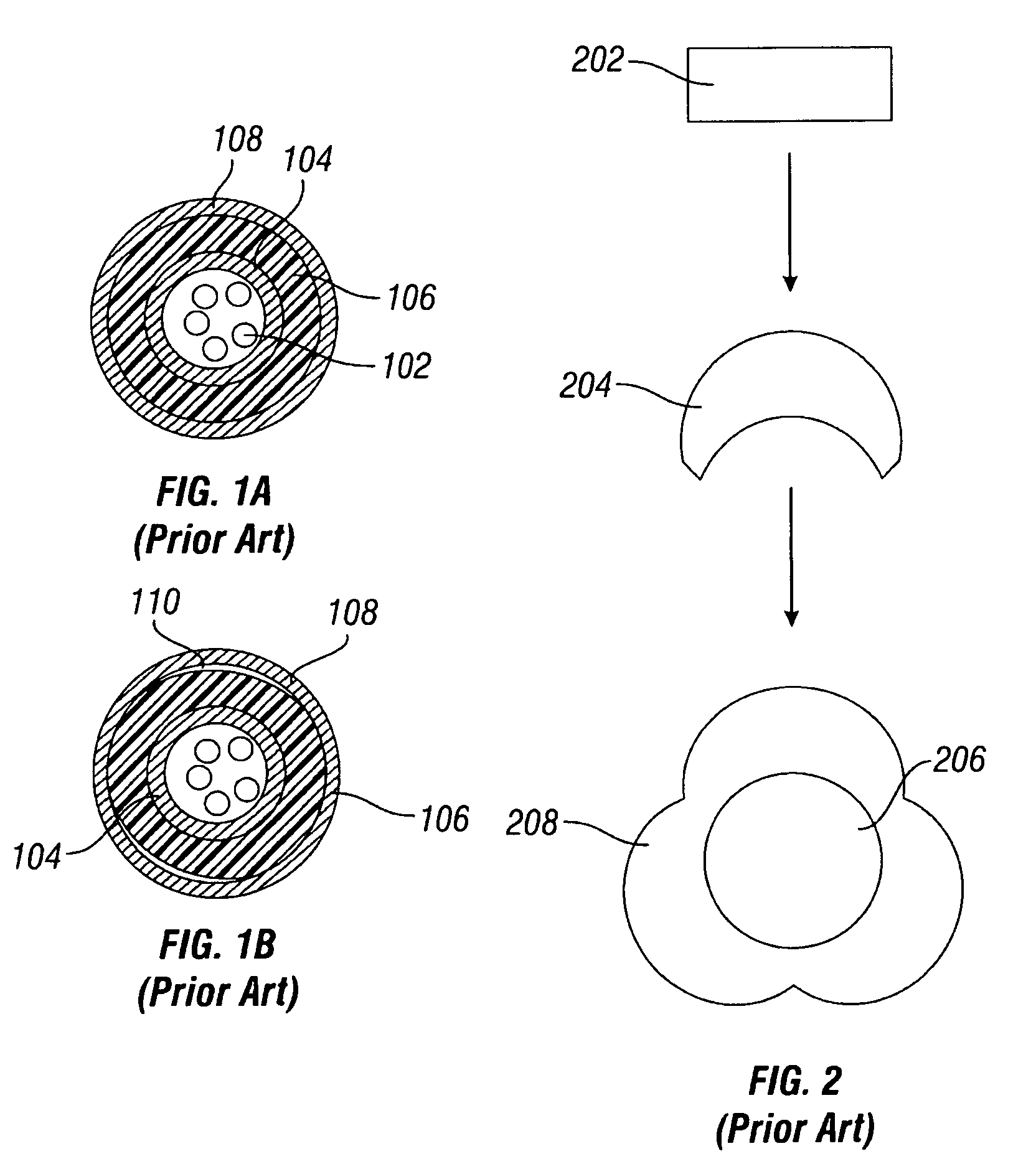

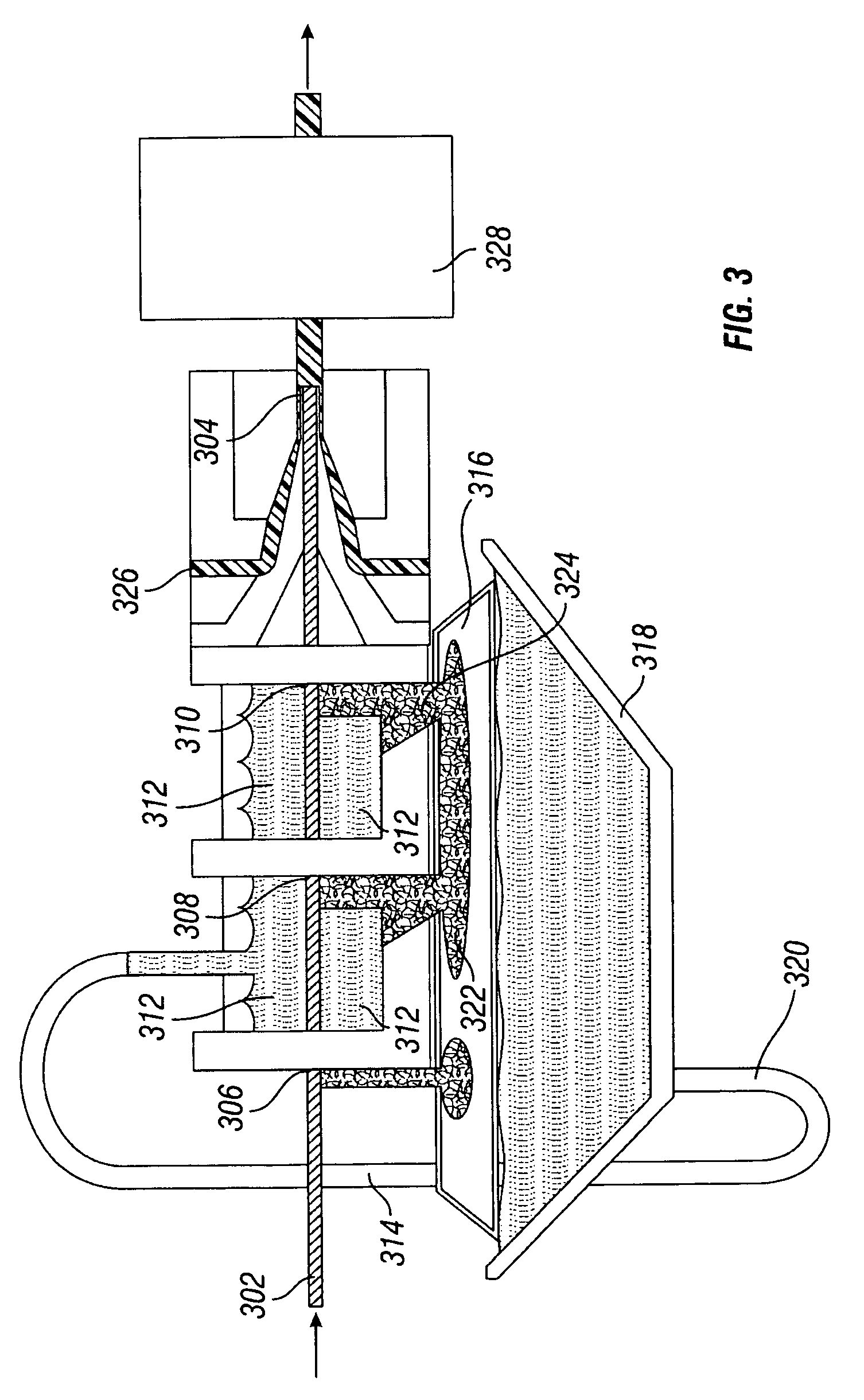

Methods of manufacturing composite slickline cables

ActiveUS20060260739A1Minimizing variation in diameterUniform circular cross-sectional shapeLamination ancillary operationsLaminationComposite strengthElectrical conductor

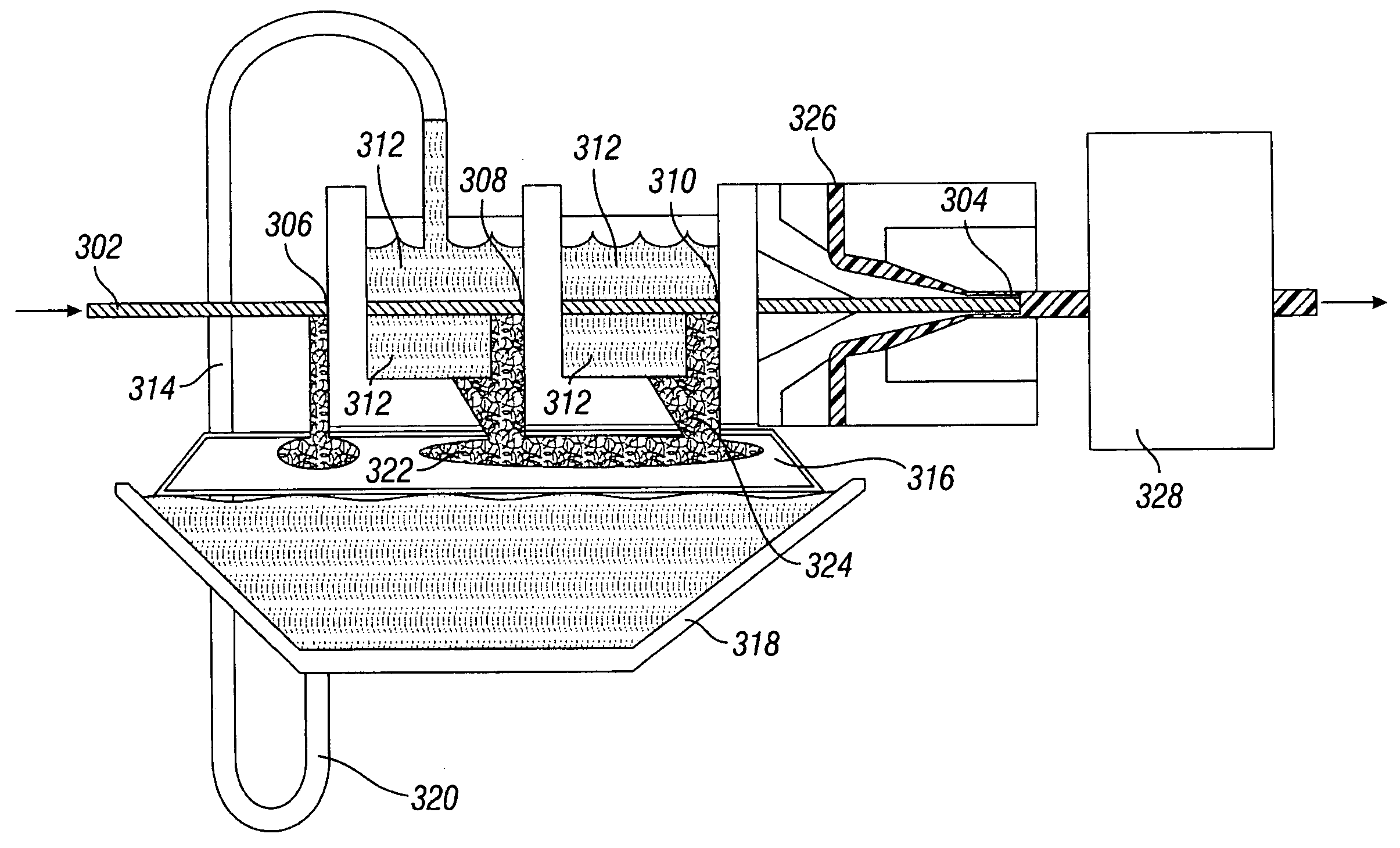

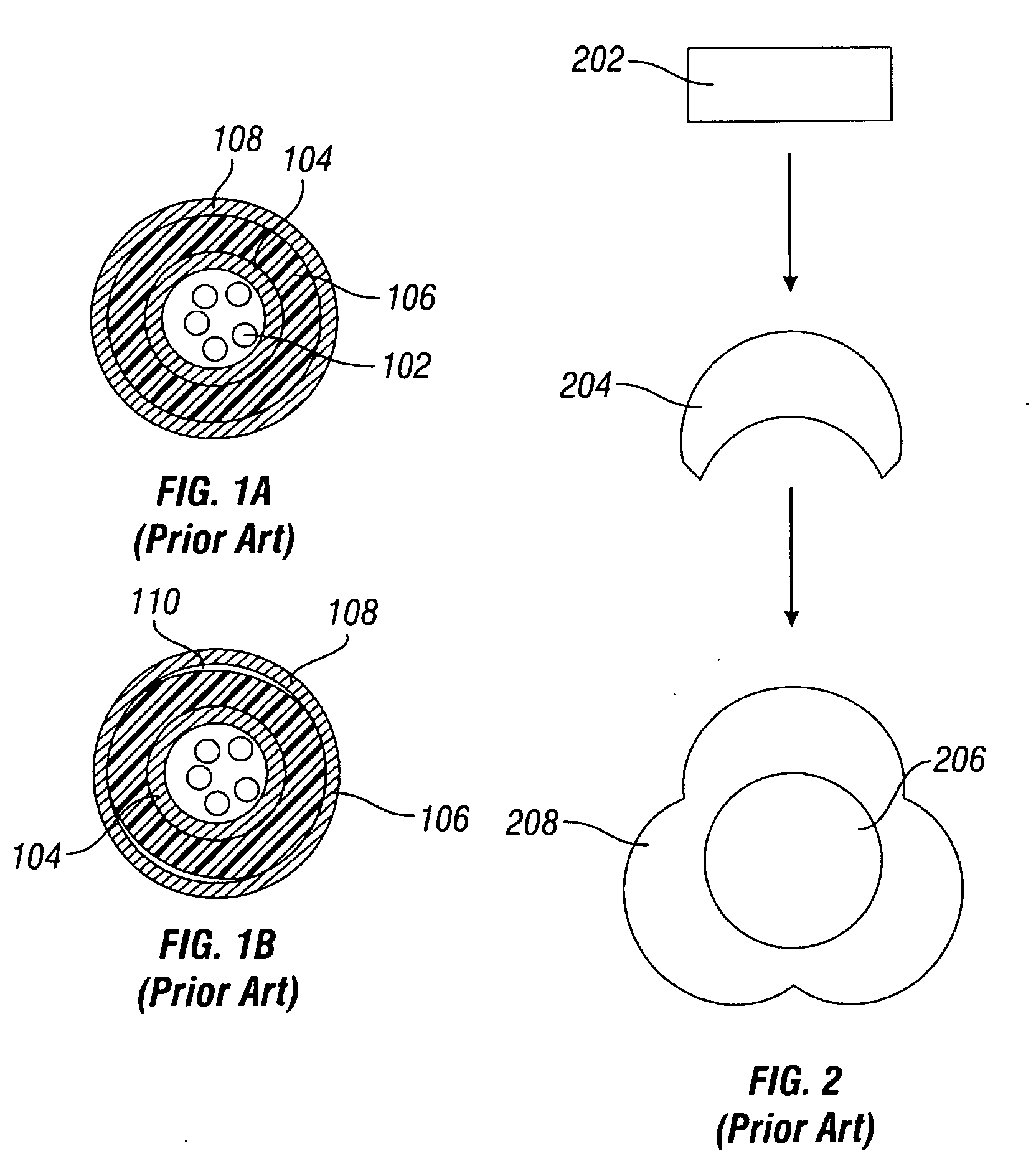

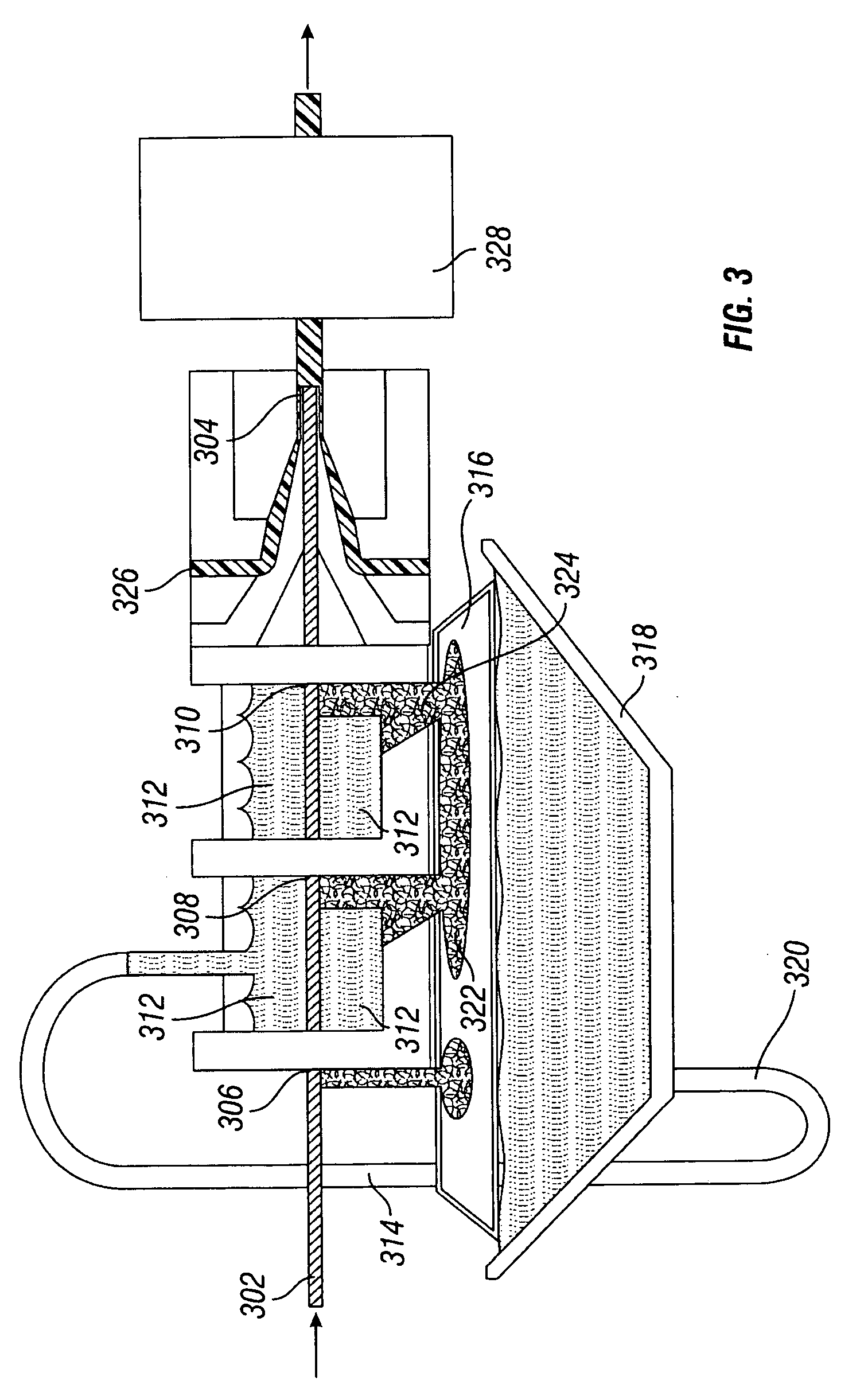

Disclosed are wellbore electric cables, and methods of manufacturing such cables, and in one aspect, methods of manufacturing wireline composite slickline cables. Some embodiments are methods which include preparing a slickline cable by providing an inner metallic tube containing at least one conductor (such as an optical fiber), disposing an epoxy / fiber composite strength layer substantially upon the outer periphery of the inner metallic tube, and exposing the combination of the inner metallic tube and composite strength layer to at least one technique for minimizing the variation in diameter and providing a substantially uniform circular cross-sectional shape of the combination. Further, an outer metallic tube is draw around the combination of the composite strength member and the inner metallic tube, to form a wellbore slickline. Cables prepared using such methods are also disclosed.

Owner:SCHLUMBERGER TECH CORP

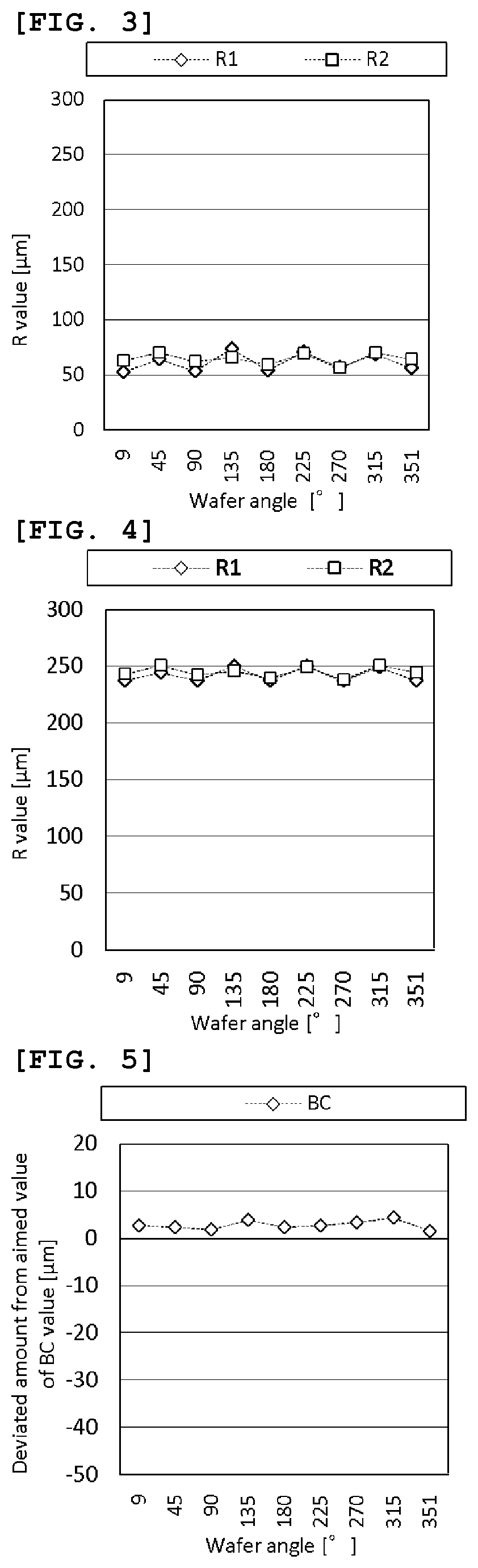

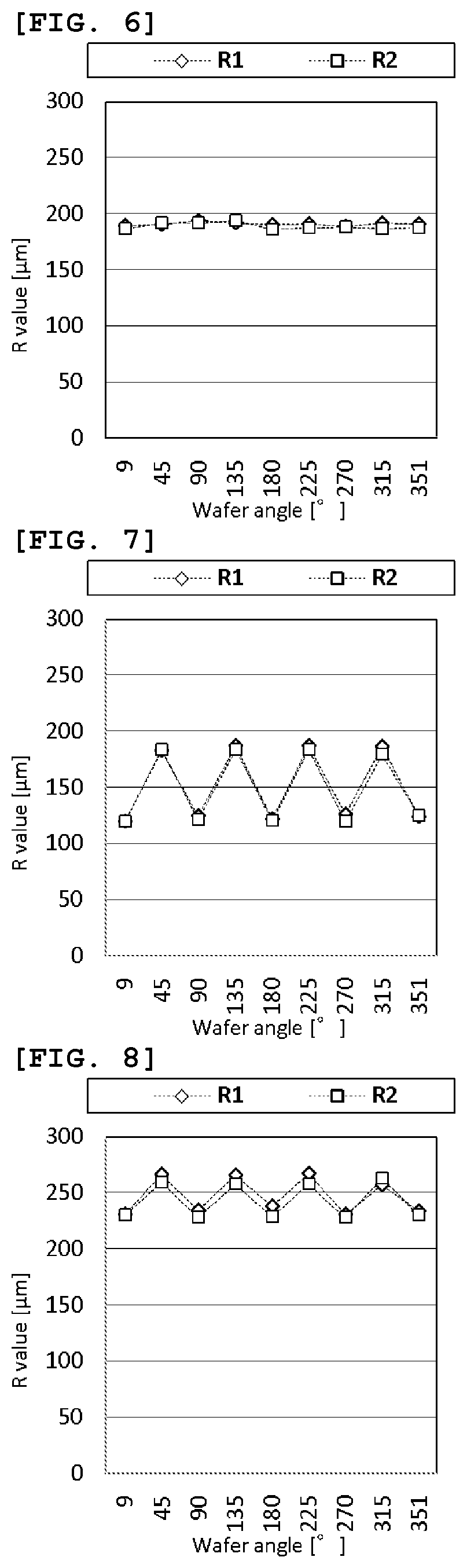

Method of machining semiconductor wafer-use polishing pad and semiconductor wafer-use polishing pad

InactiveUS20040266326A1Easily and accurately formedInner surfacePigmenting treatmentOther chemical processesWater insolubleSurface roughness

A processing method of a polishing pad for semiconductor wafer capable of forming a groove, a concave portion, a through hole and the like having a small surface roughness of the inner surface of the groove and the like of 20 mum or less, a high dimensional accuracy and a uniform cross-sectional shape, and a polishing pad for semiconductor wafer. In the processing method, a surface of a polishing pad including a water-insoluble matrix containing a crosslinked polymer and a water-soluble particle dispersed in the water-insoluble matrix is processed by cutting and the like. Additionally, when a groove and the like are formed, it is preferable that a polishing pad is placed on one surface side of a machining table having a sucking hole, the pad is fixed on the one surface side of the machining table by vacuuming sucking it from the other surface of the machining table, and then a groove and the like are formed.

Owner:JSR CORPORATIOON

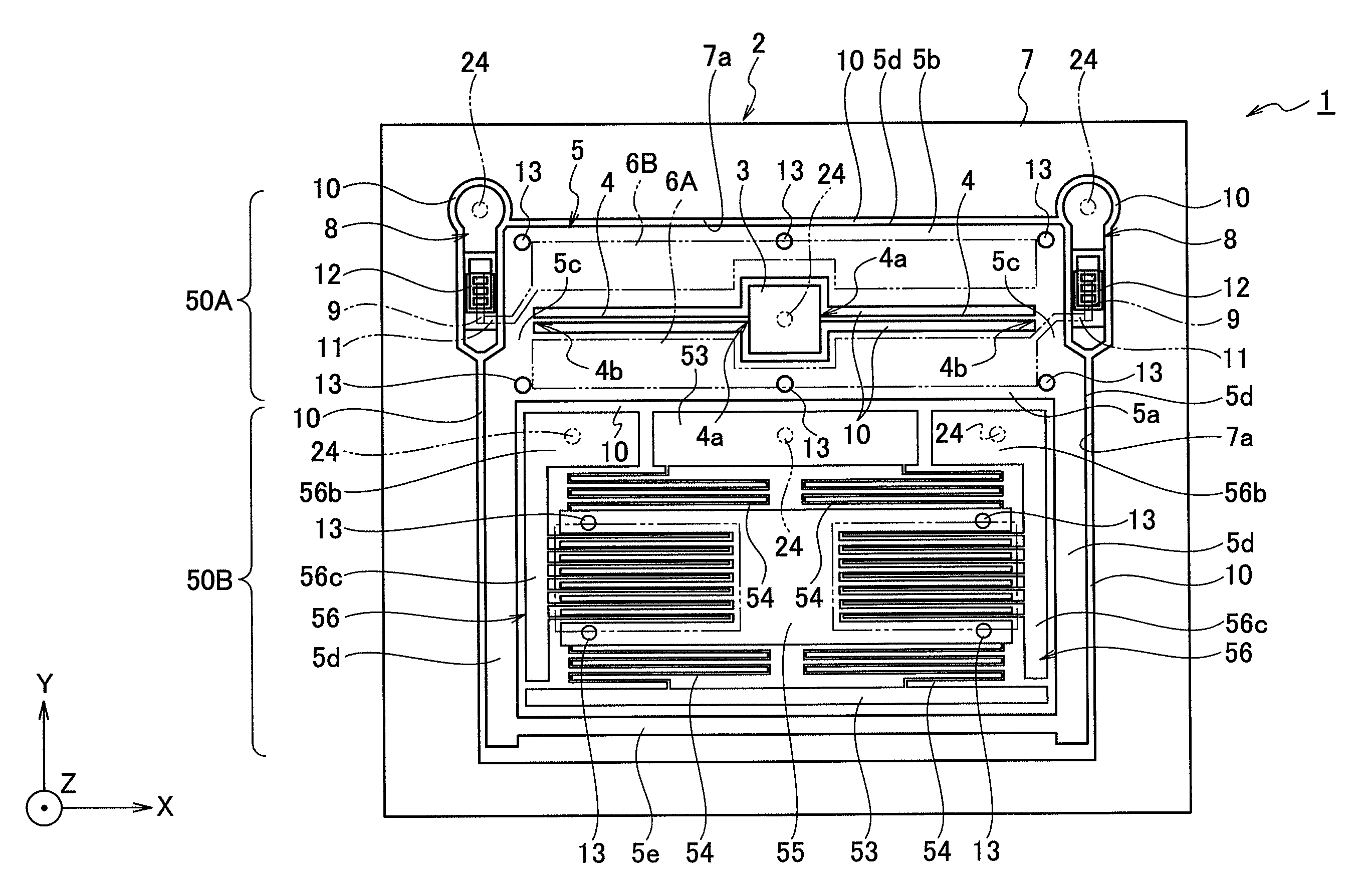

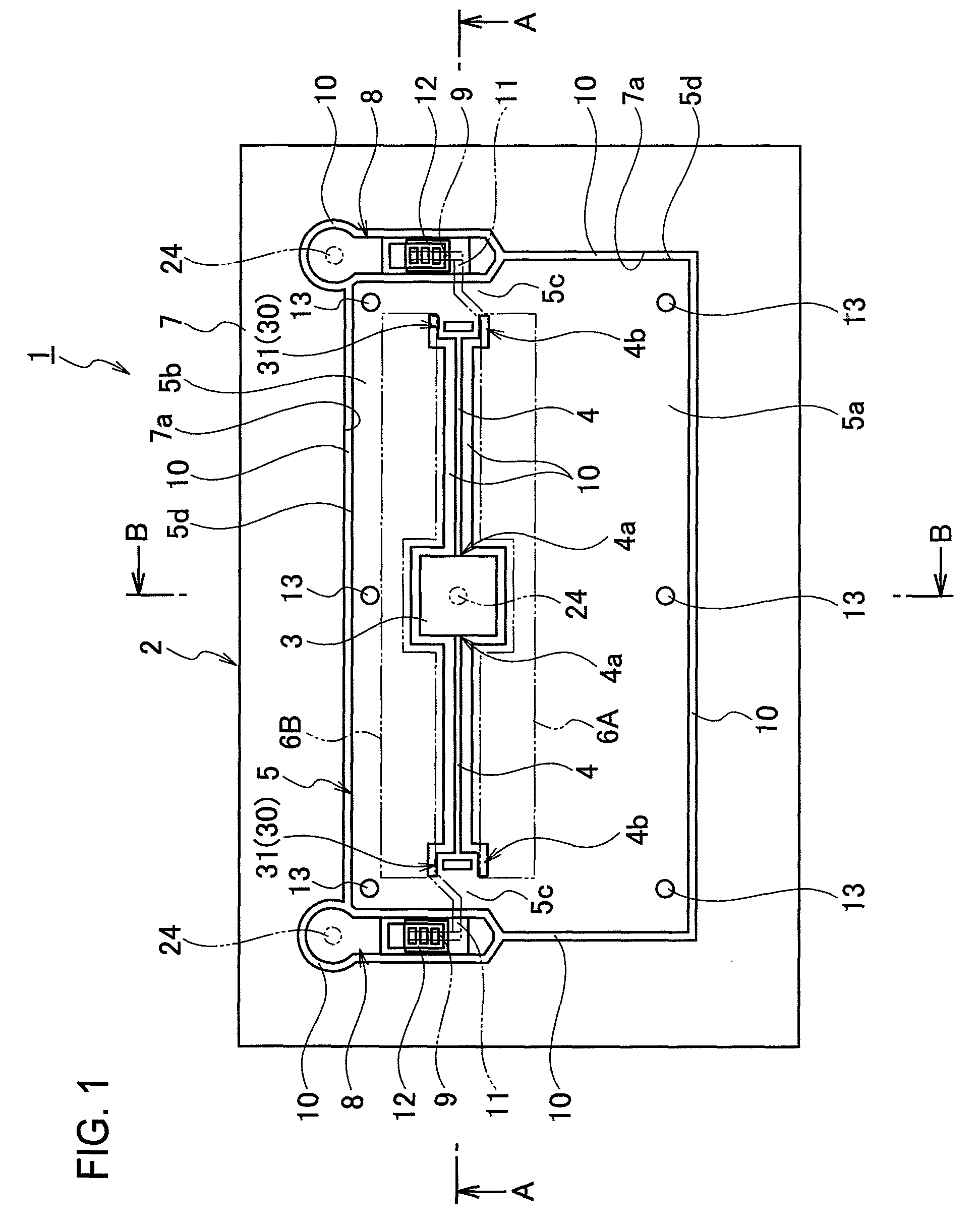

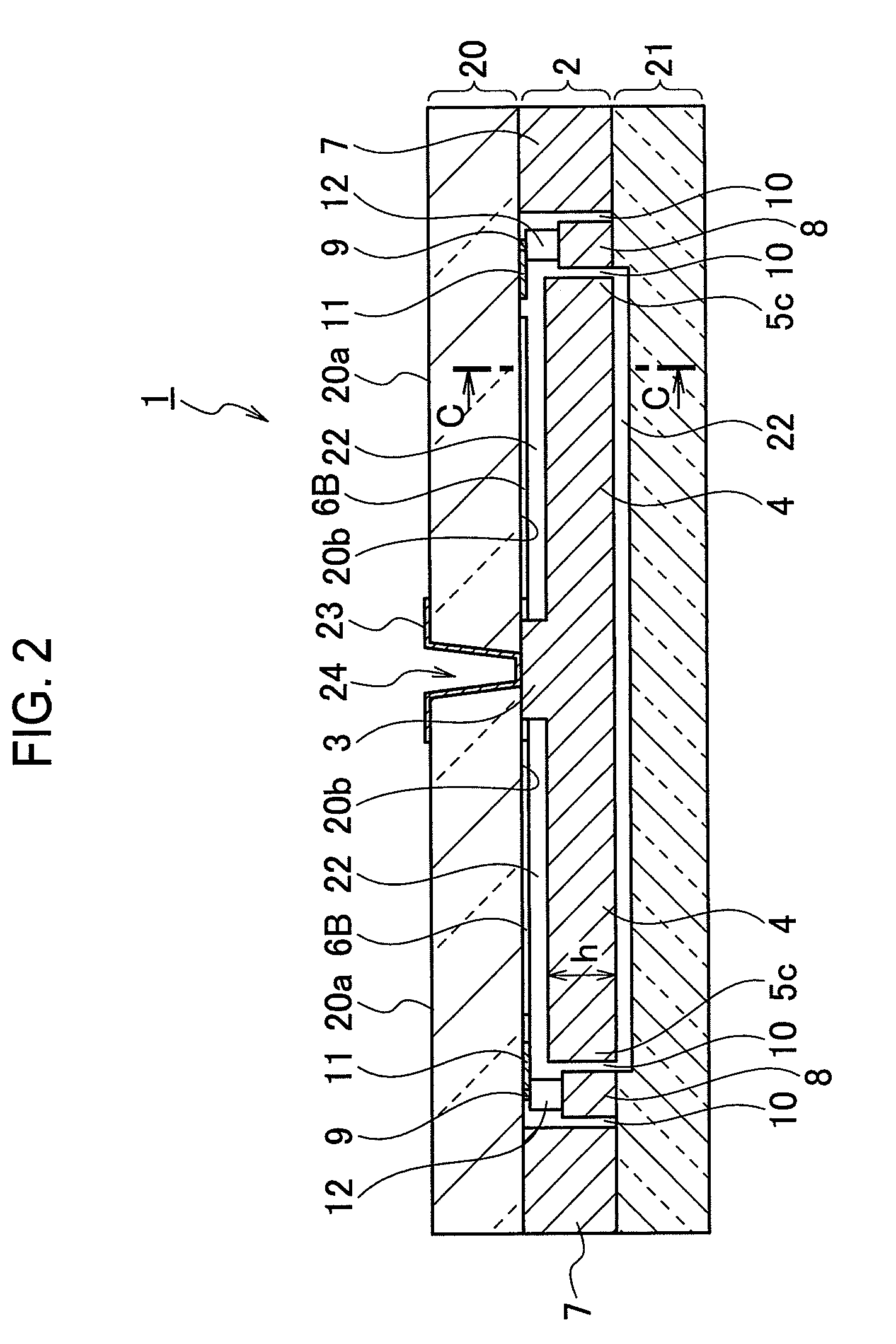

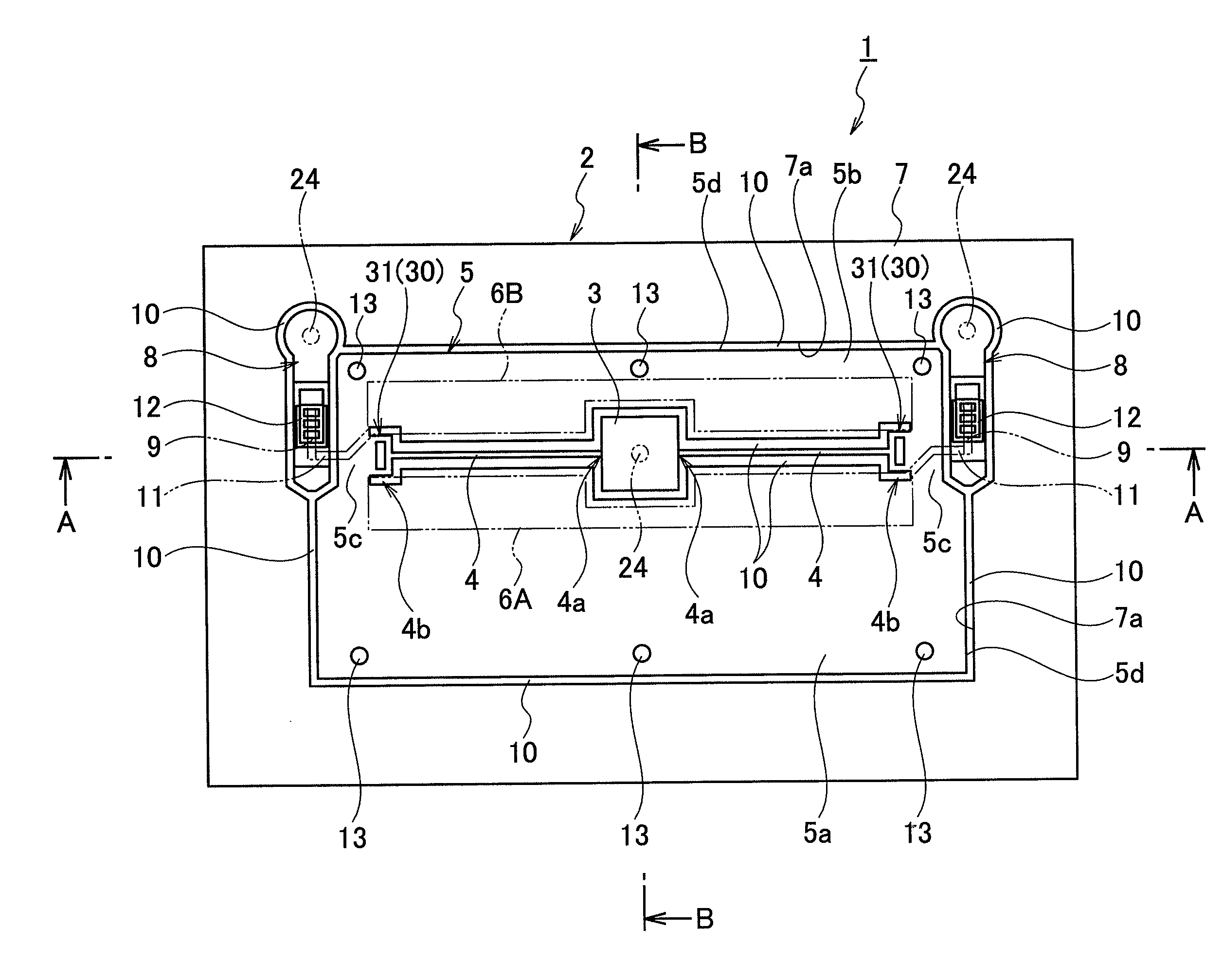

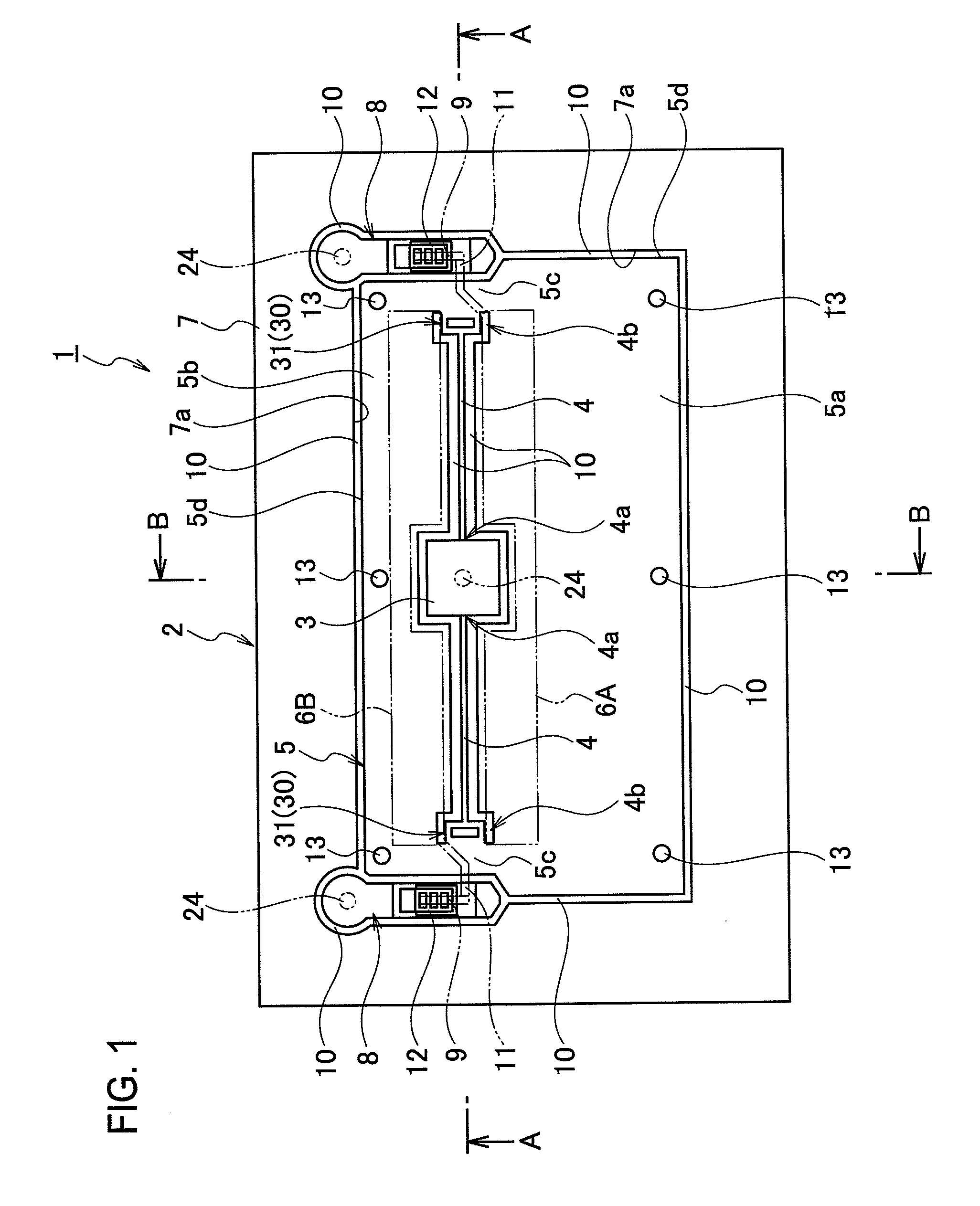

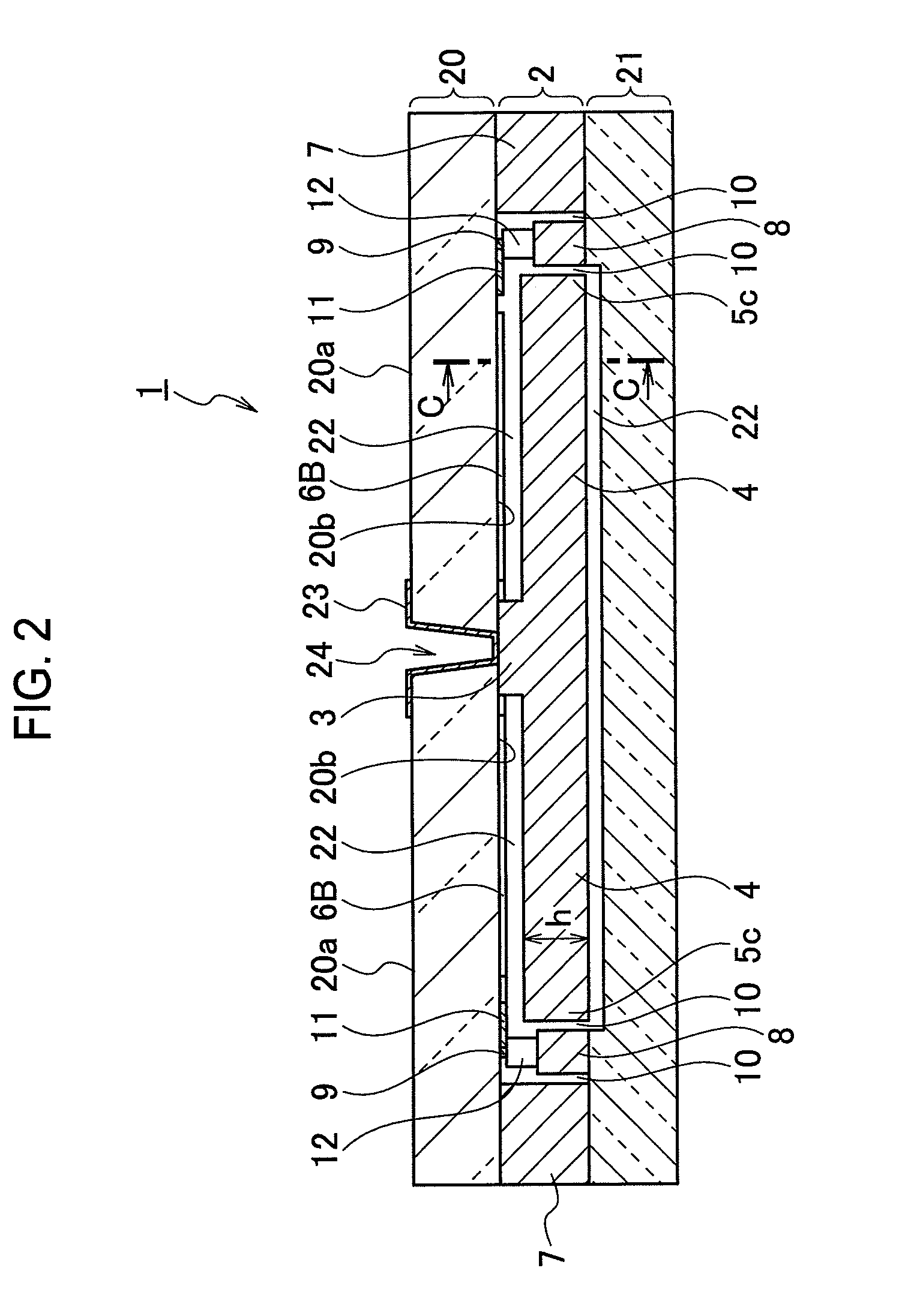

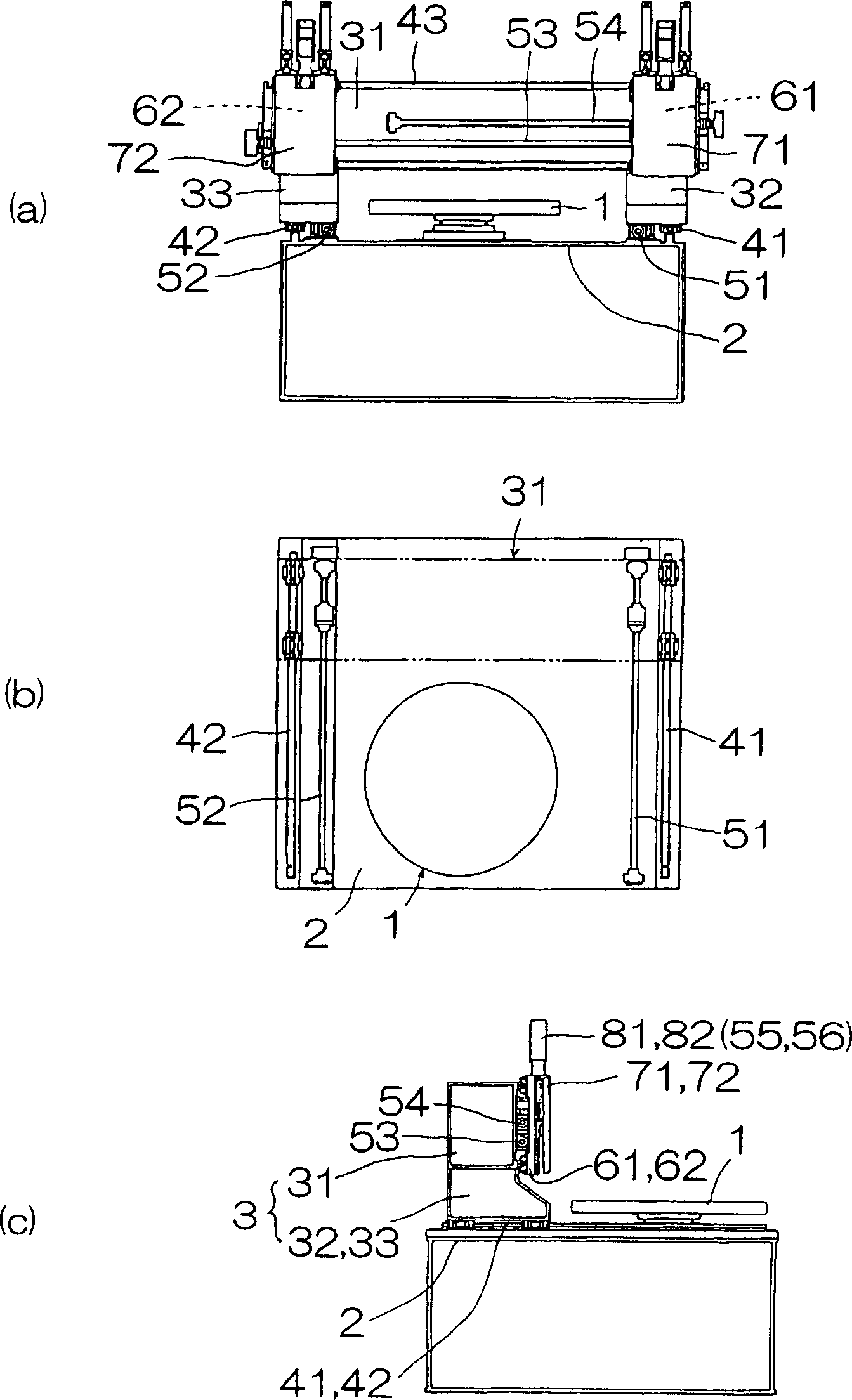

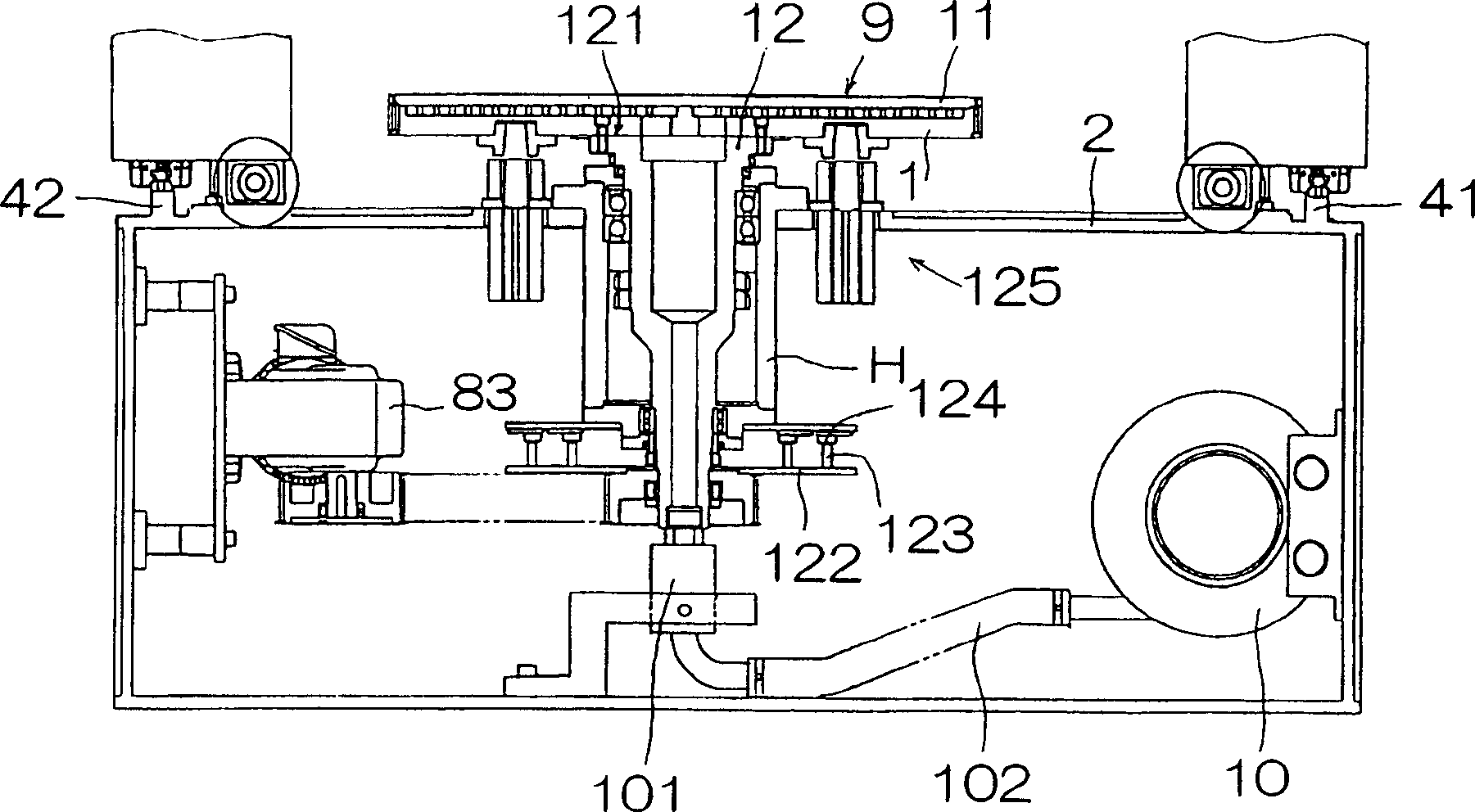

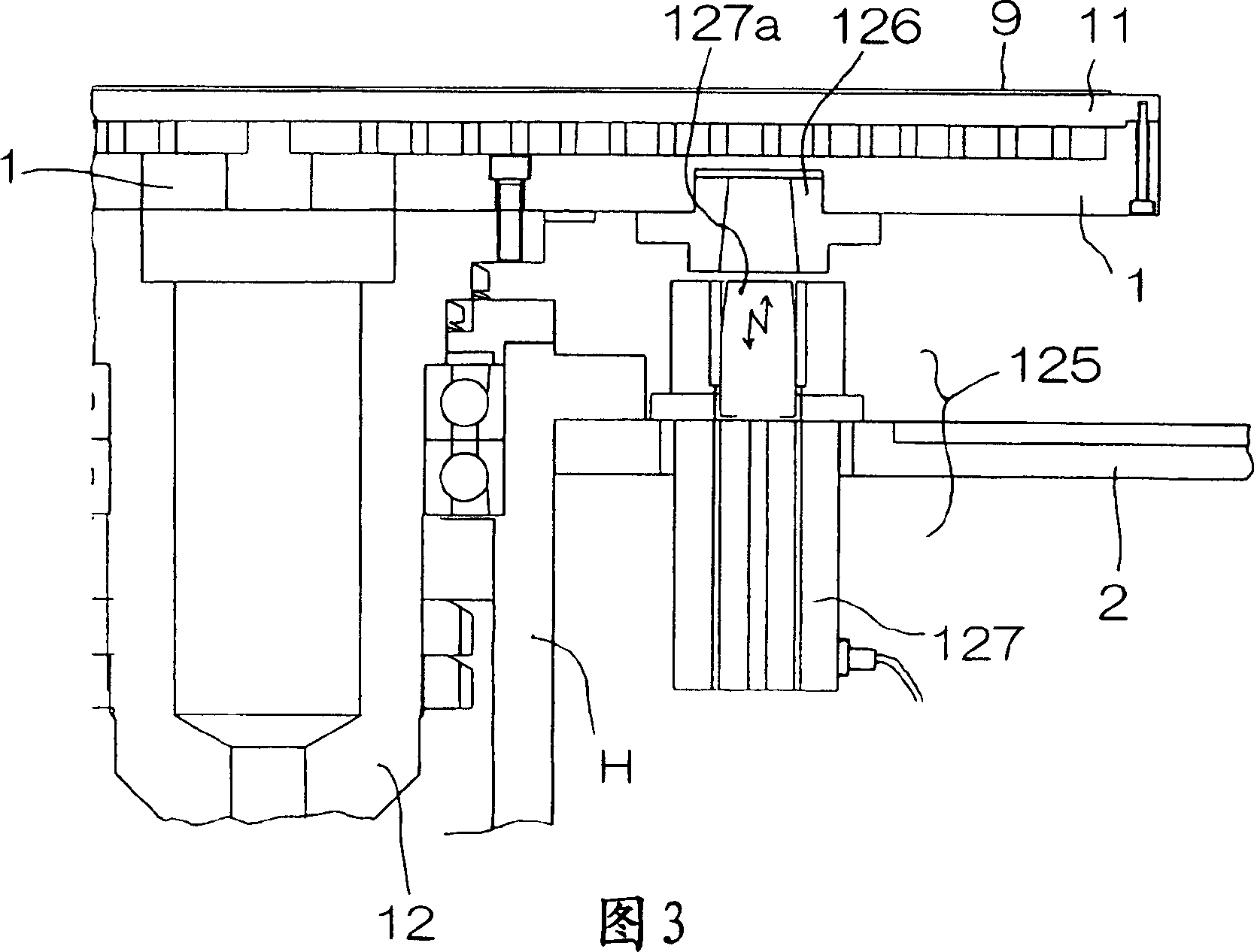

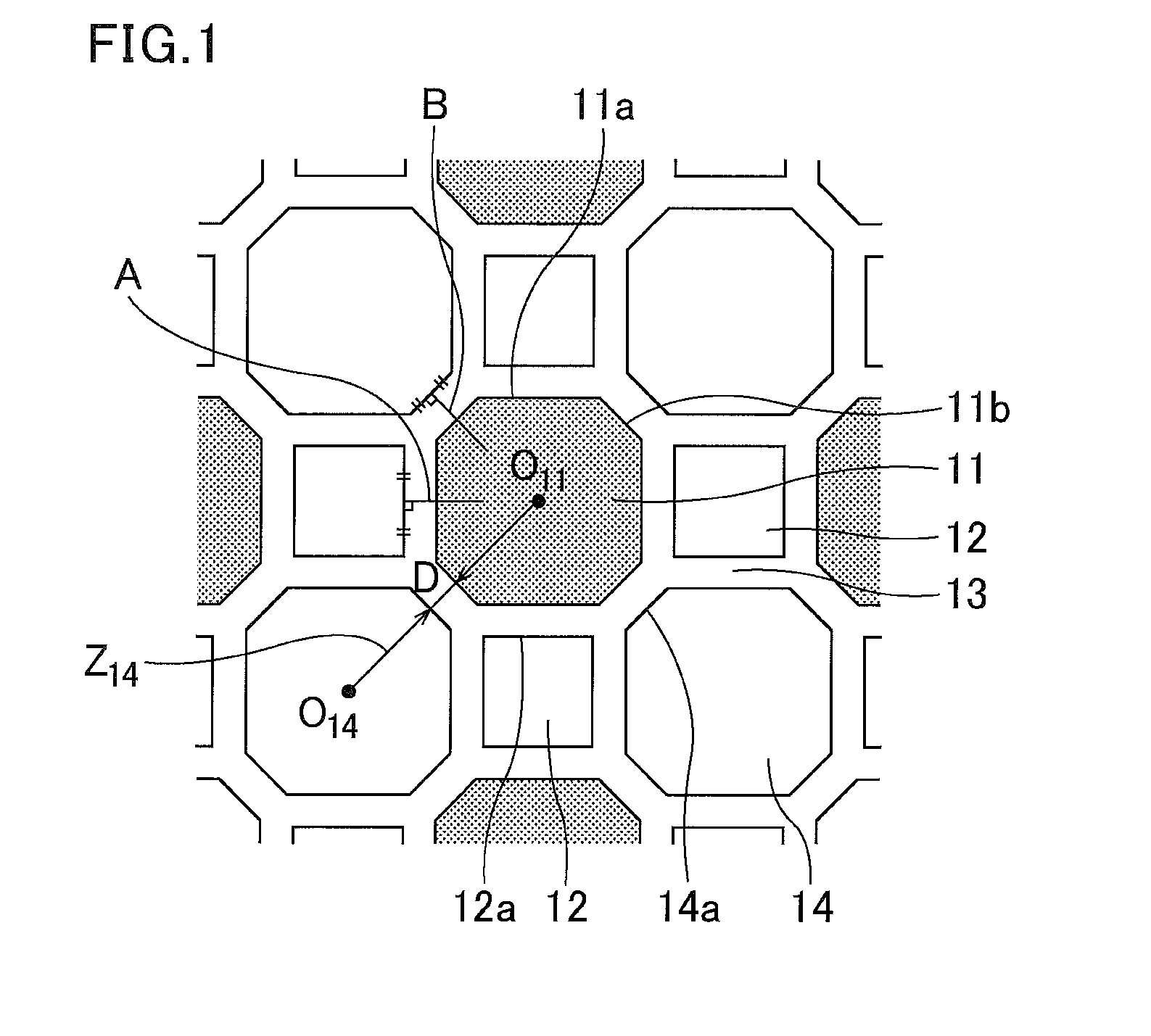

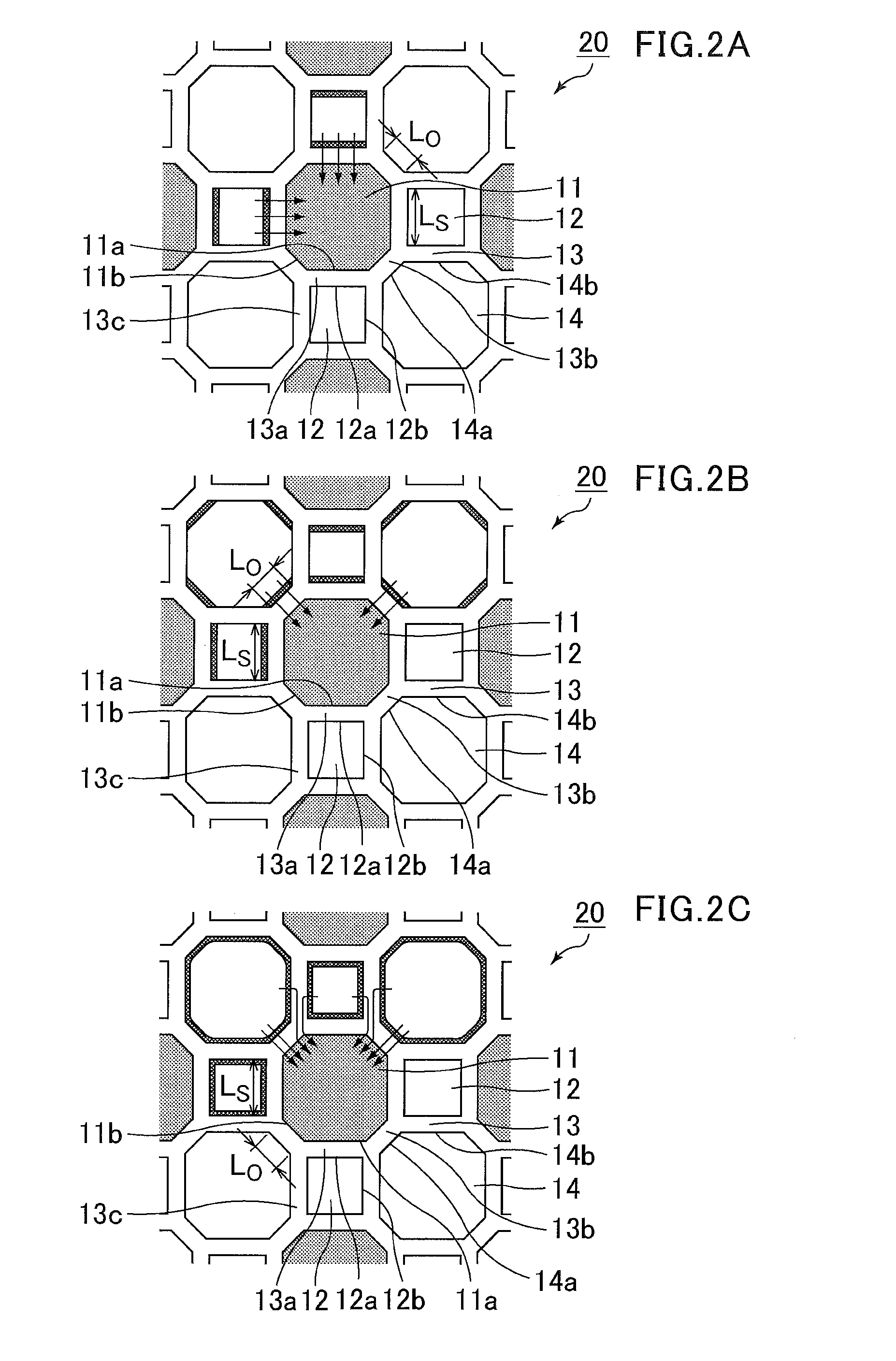

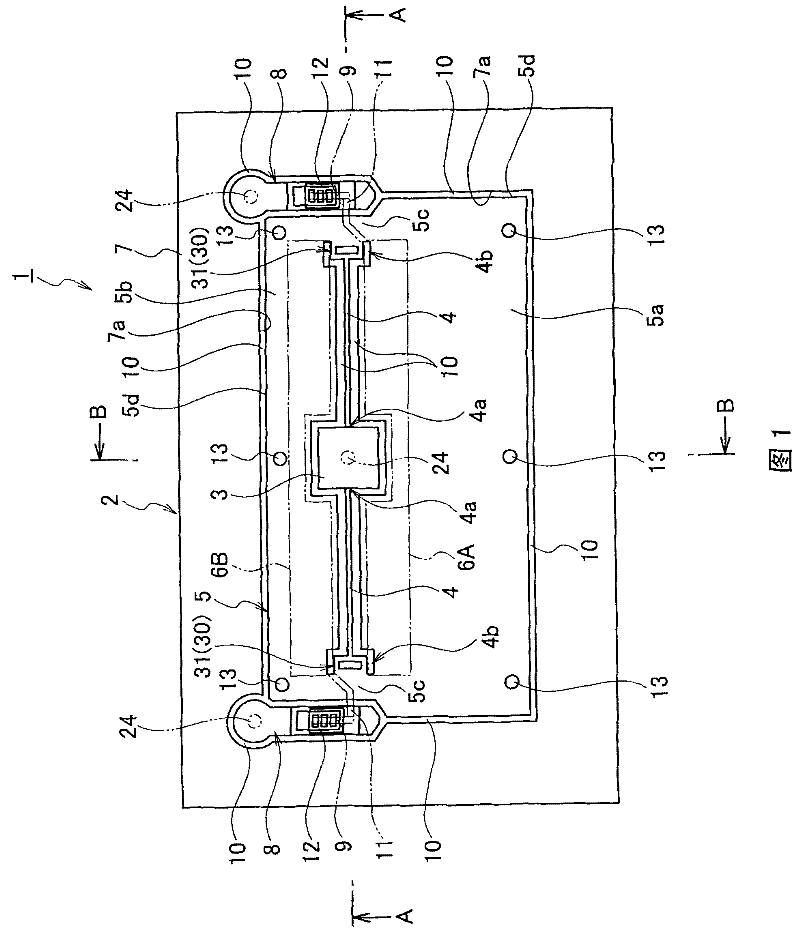

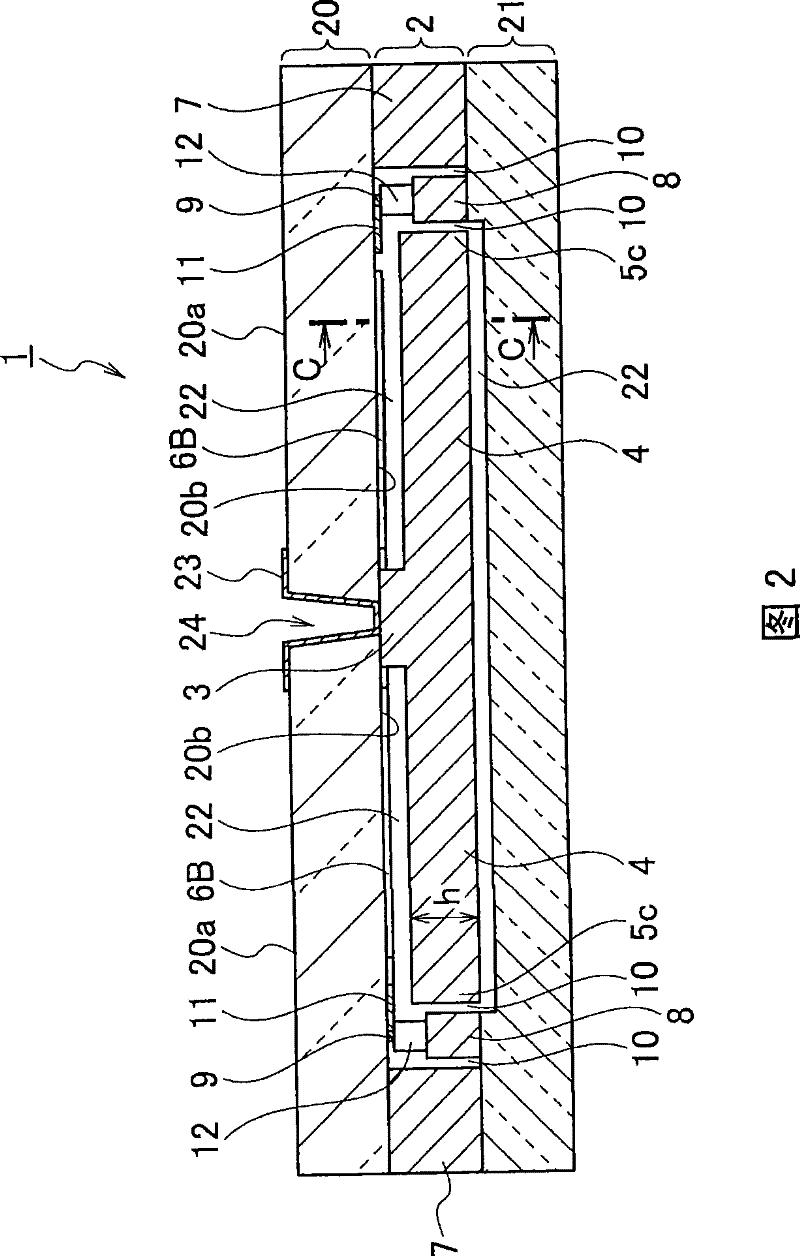

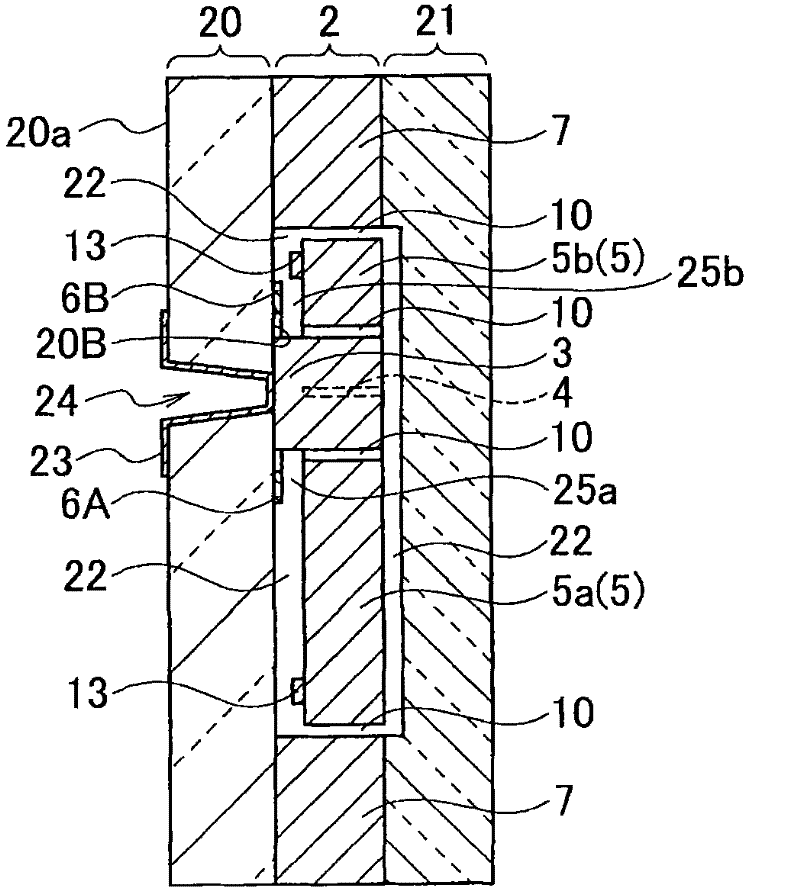

Capacitive sensor

ActiveUS8176782B2Relieve stressRelieve pressureResistance/reactance/impedenceAcceleration measurementEngineeringCapacitive sensing

A capacitive sensor includes a fixed electrode and a movable electrode that is movably supported by an anchor portion through a beam portion. The fixed electrode and the movable electrode are opposed to each other with a gap interposed therebetween, thereby constituting a detecting unit. A capacitance suitable for a size of the gap is detected to detect a predetermined physical value. At least one of an end of the beam portion connected to the anchor portion and an end of the beam portion connected to the movable electrode is provided with a stress moderating unit that moderates a stress.

Owner:MOSAID TECH

Capacitive sensor

ActiveUS20090266164A1Relieve stressRelieve pressureResistance/reactance/impedenceAcceleration measurementEngineeringCapacitive sensing

A capacitive sensor includes a fixed electrode and a movable electrode that is movably supported by an anchor portion through a beam portion. The fixed electrode and the movable electrode are opposed to each other with a gap interposed therebetween, thereby constituting a detecting unit. A capacitance suitable for a size of the gap is detected to detect a predetermined physical value. At least one of an end of the beam portion connected to the anchor portion and an end of the beam portion connected to the movable electrode is provided with a stress moderating unit that moderates a stress.

Owner:MOSAID TECH

Methods of manufacturing composite slickline cables

ActiveUS8000572B2Variation in diameterUniform cross-sectional shapeLamination ancillary operationsLaminationEpoxyComposite strength

Disclosed are wellbore electric cables, and methods of manufacturing such cables, and in one aspect, methods of manufacturing wireline composite slickline cables. Some embodiments are methods which include preparing a slickline cable by providing an inner metallic tube containing at least one conductor (such as an optical fiber), disposing an epoxy / fiber composite strength layer substantially upon the outer periphery of the inner metallic tube, and exposing the combination of the inner metallic tube and composite strength layer to at least one technique for minimizing the variation in diameter and providing a substantially uniform circular cross-sectional shape of the combination. Further, an outer metallic tube is draw around the combination of the composite strength member and the inner metallic tube, to form a wellbore slickline. Cables prepared using such methods are also disclosed.

Owner:SCHLUMBERGER TECH CORP

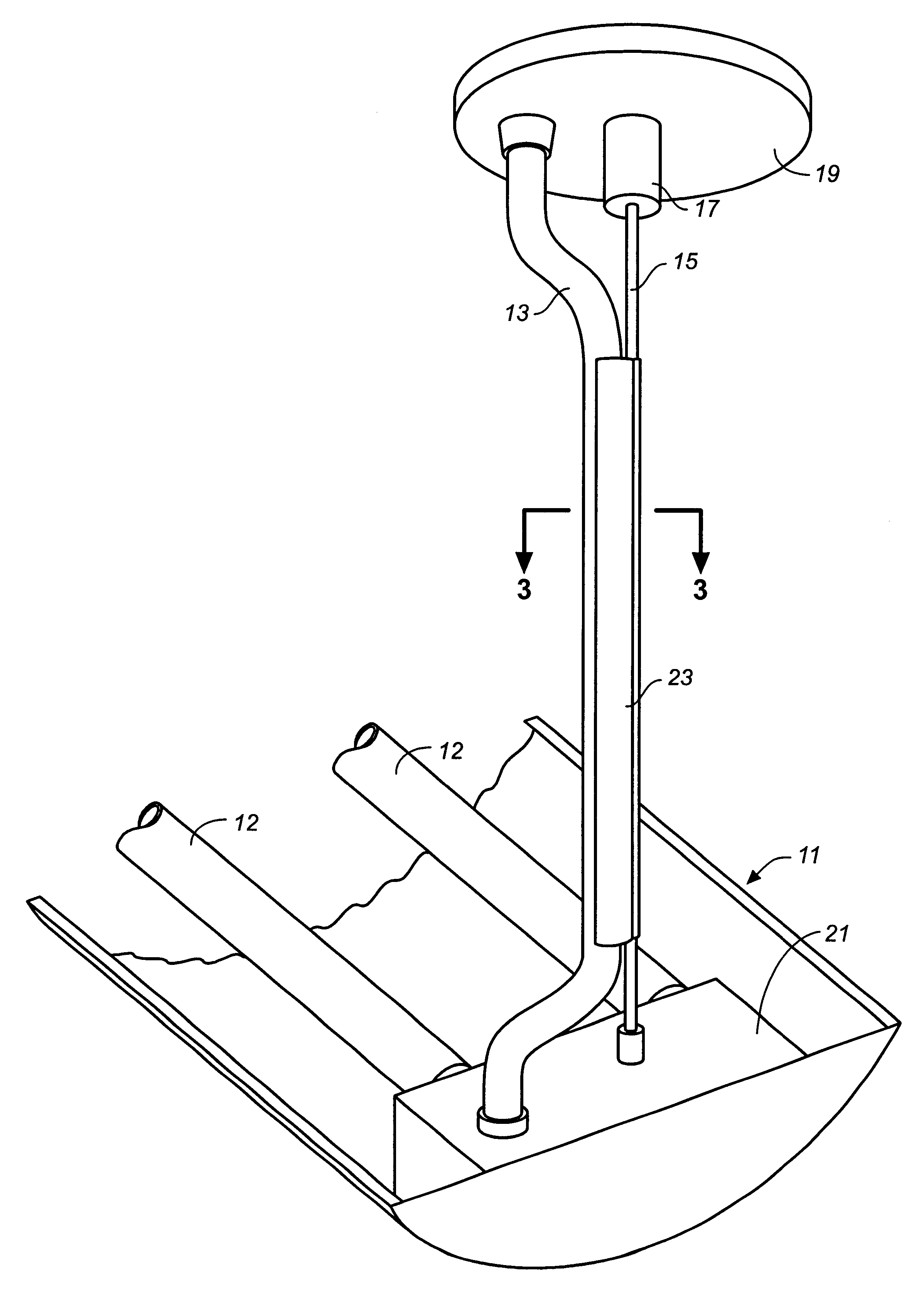

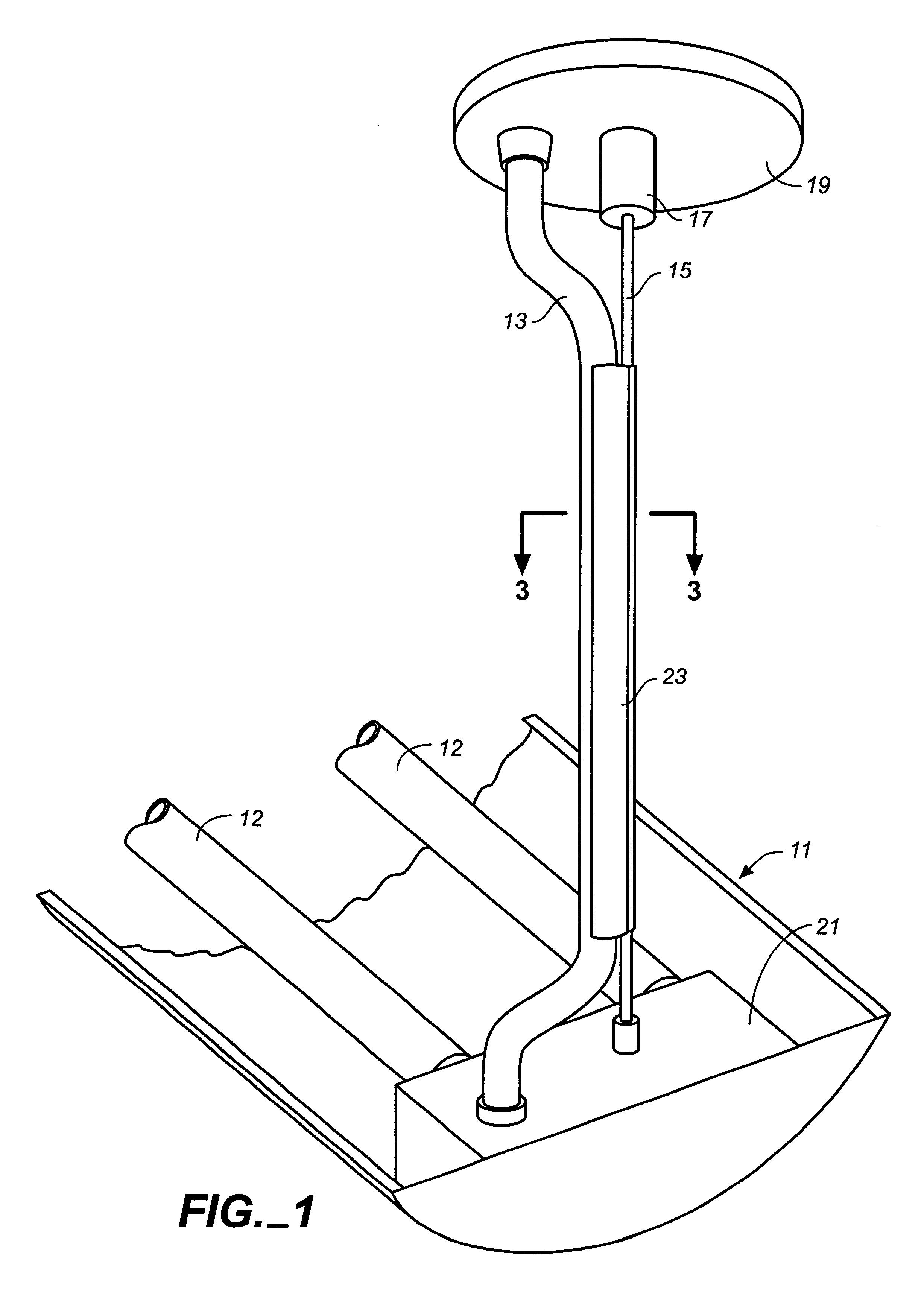

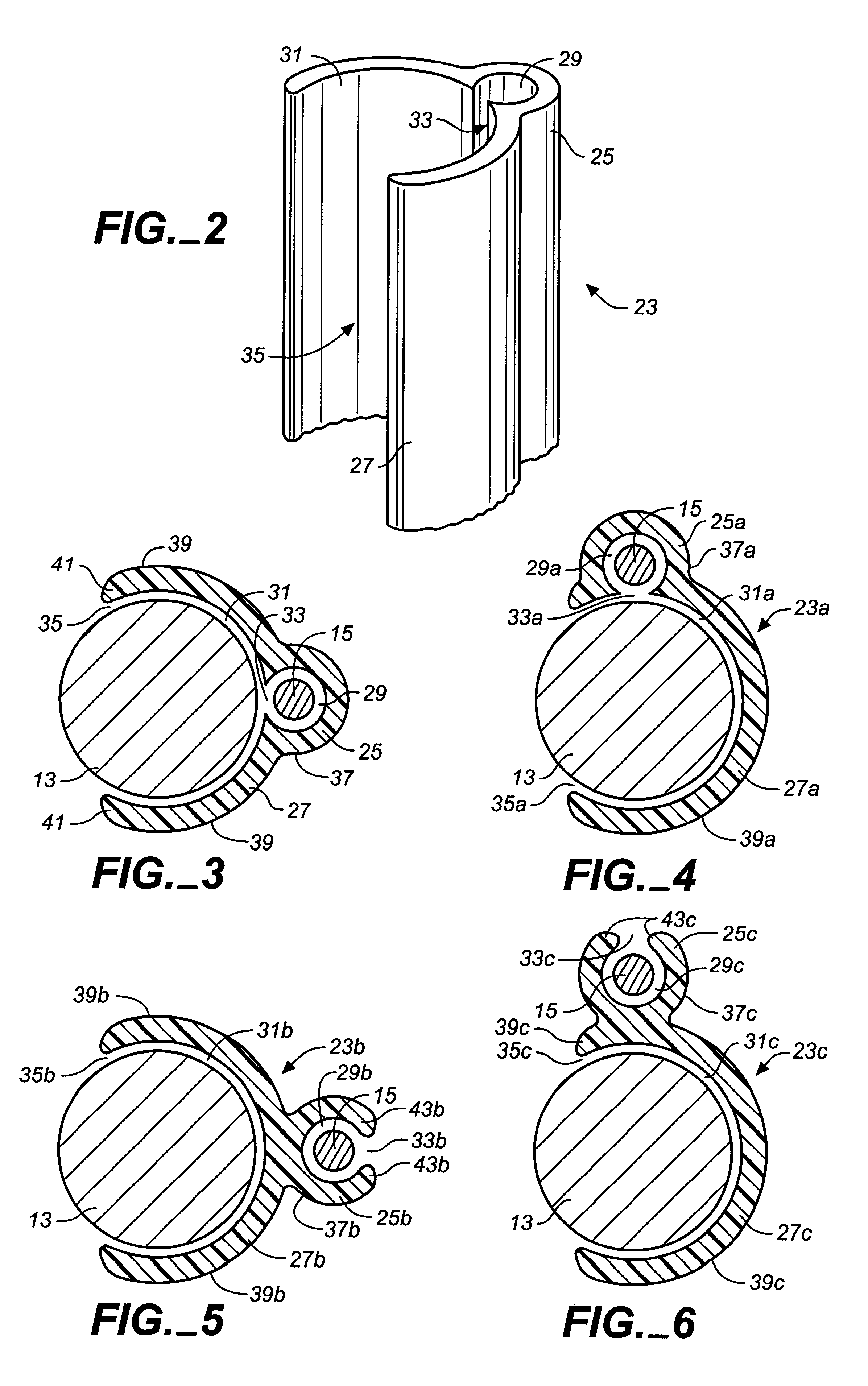

Electrical power cord manager for a lighting fixture

InactiveUS6428190B1Uniform cross-sectional shapeLight source combinationsLighting support devicesElectricityLight equipment

A cord manager for a suspended electric lighting fixture holds the fixture's power cord in close parallel relation to the fixture's suspension cable at electrical feed locations. The cord manager, which is suitably fabricated of extruded plastic, has an elongated first body portion with a lengthwise cable retention channel and an elongated second body portion having a power cord retention channel. In one embodiment of the invention, the retention channel for the suspension cable opens onto the power cord retention channel. In another embodiment, the suspension cable and power cord retention channels open outwardly away from each other. The cord manager provides the clean, finished look to the lighting installation at power feed locations.

Owner:ABL IP HLDG

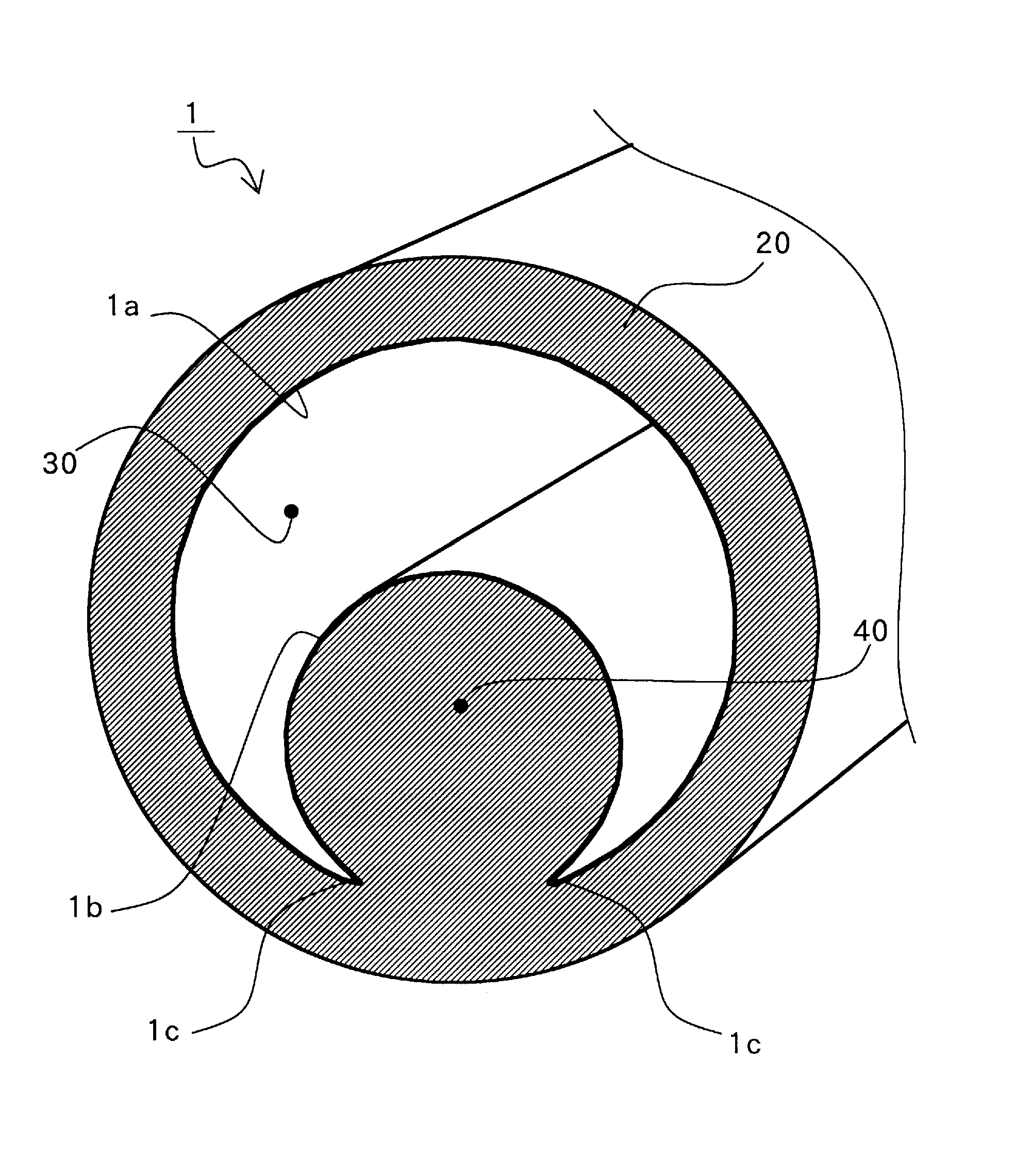

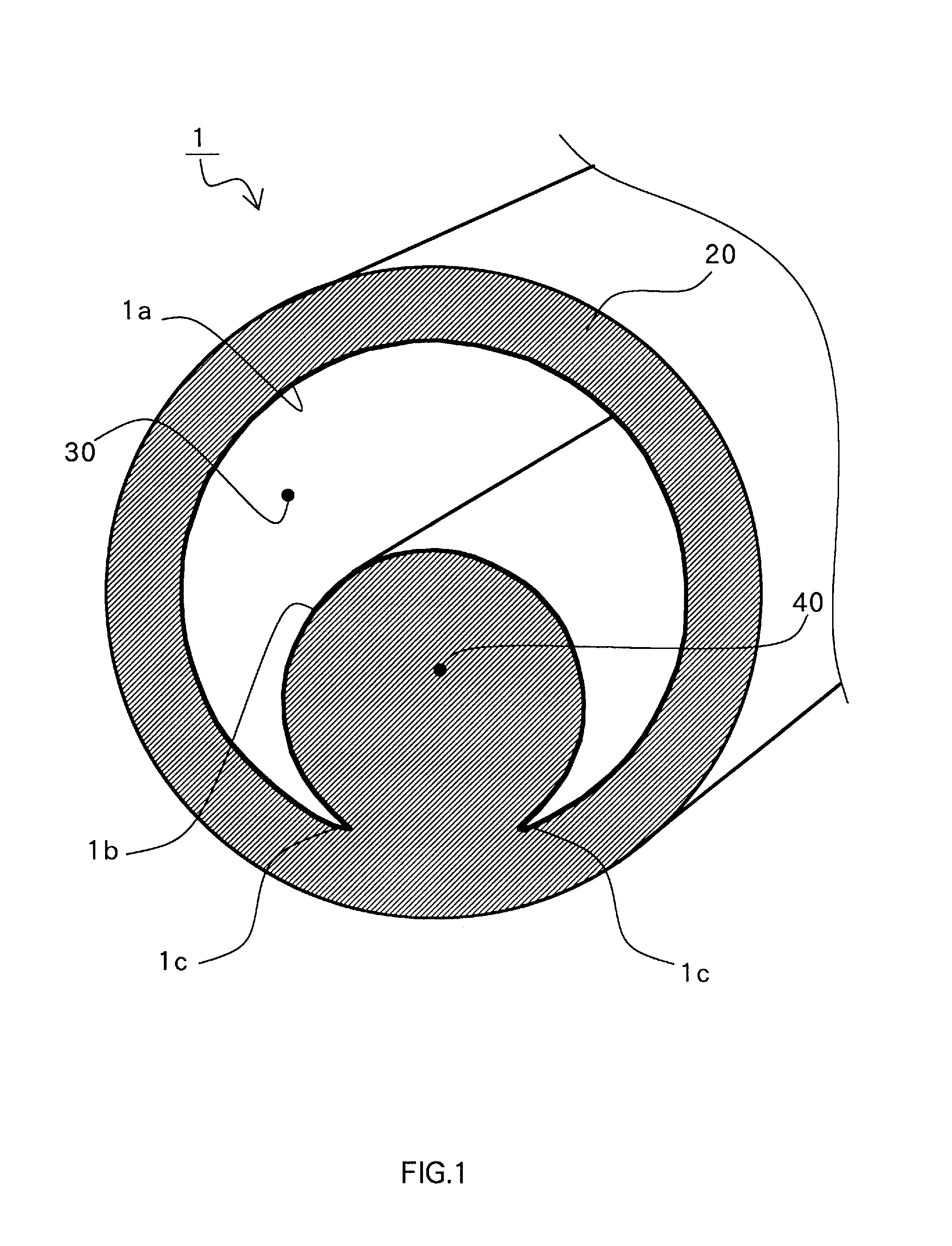

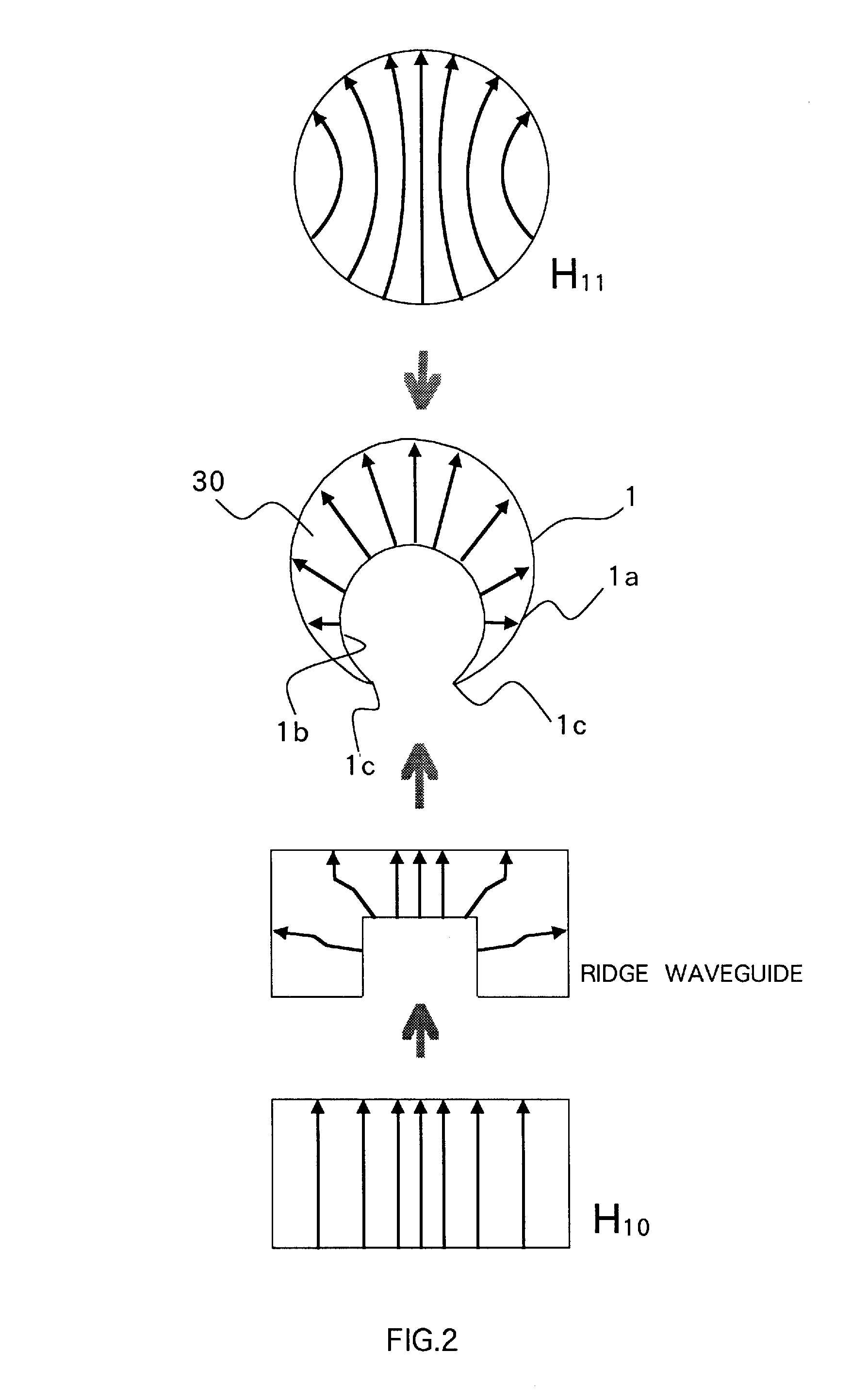

Electromagnetic wave transmission medium

ActiveUS20100001809A1Increase valueInhibit deteriorationOne-port networksWaveguidesElectricityElectromagnetic wave transmission

Provided is an electromagnetic wave transmission medium which is suited for mass production and does not affect a transmission mode. The electromagnetic wave transmission medium includes, as a main element, a flexible cylindrical tube (1) molded so that a cross-sectional shape of the cylindrical tube in a direction orthogonal to a tube axis is uniform in a direction of the tube axis. The cylindrical tube (1) includes an inner wall formed of a conductive layer having a thickness equal to or more than a skin depth. The cross-sectional shape is a circular ridge waveguide shape having a ridge (1b) which is oriented to a cylindrical axis and is symmetric with respect to a center, and the ridge (1b) has a structure to be fed with electricity.

Owner:YOKOWO CO LTD

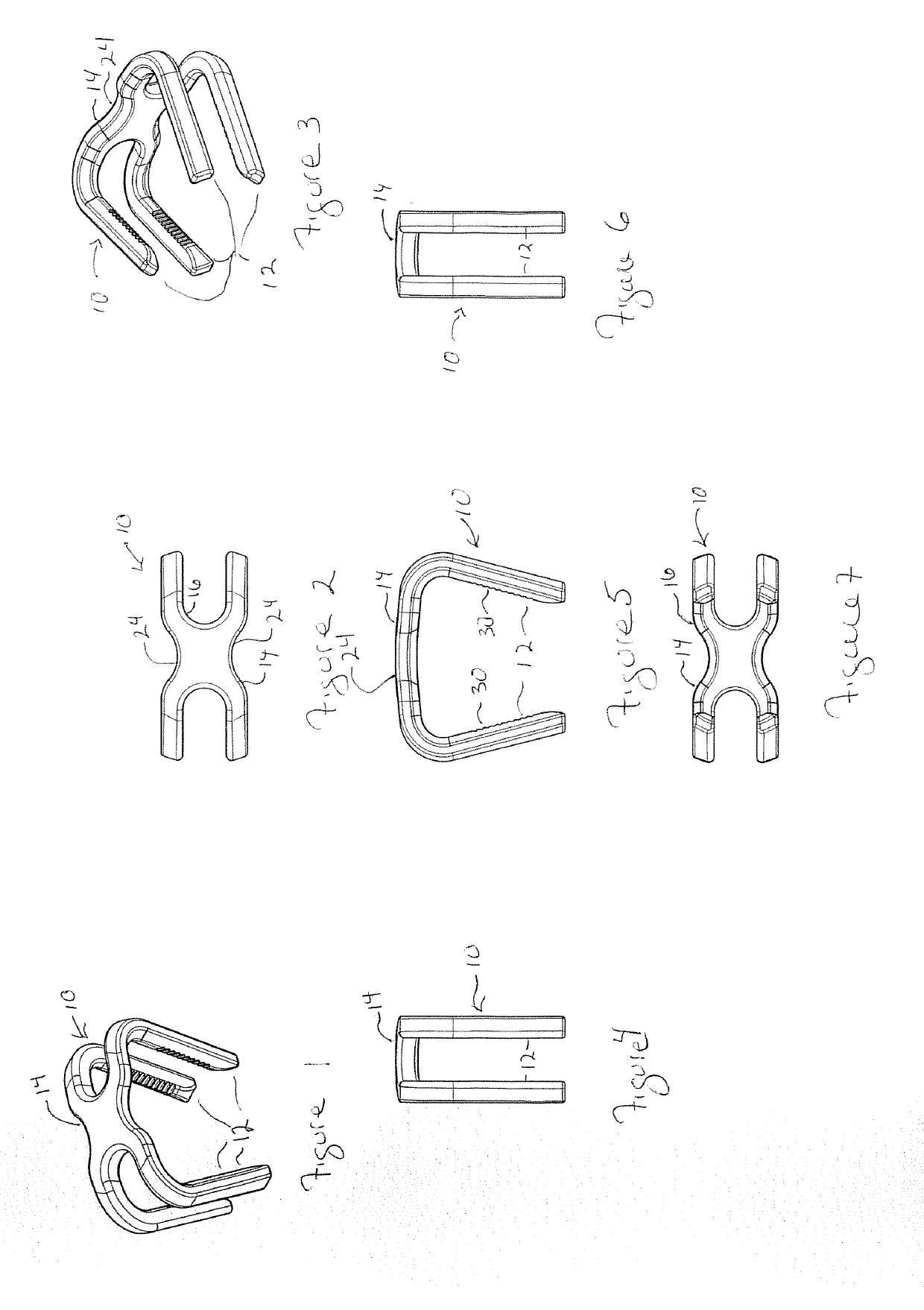

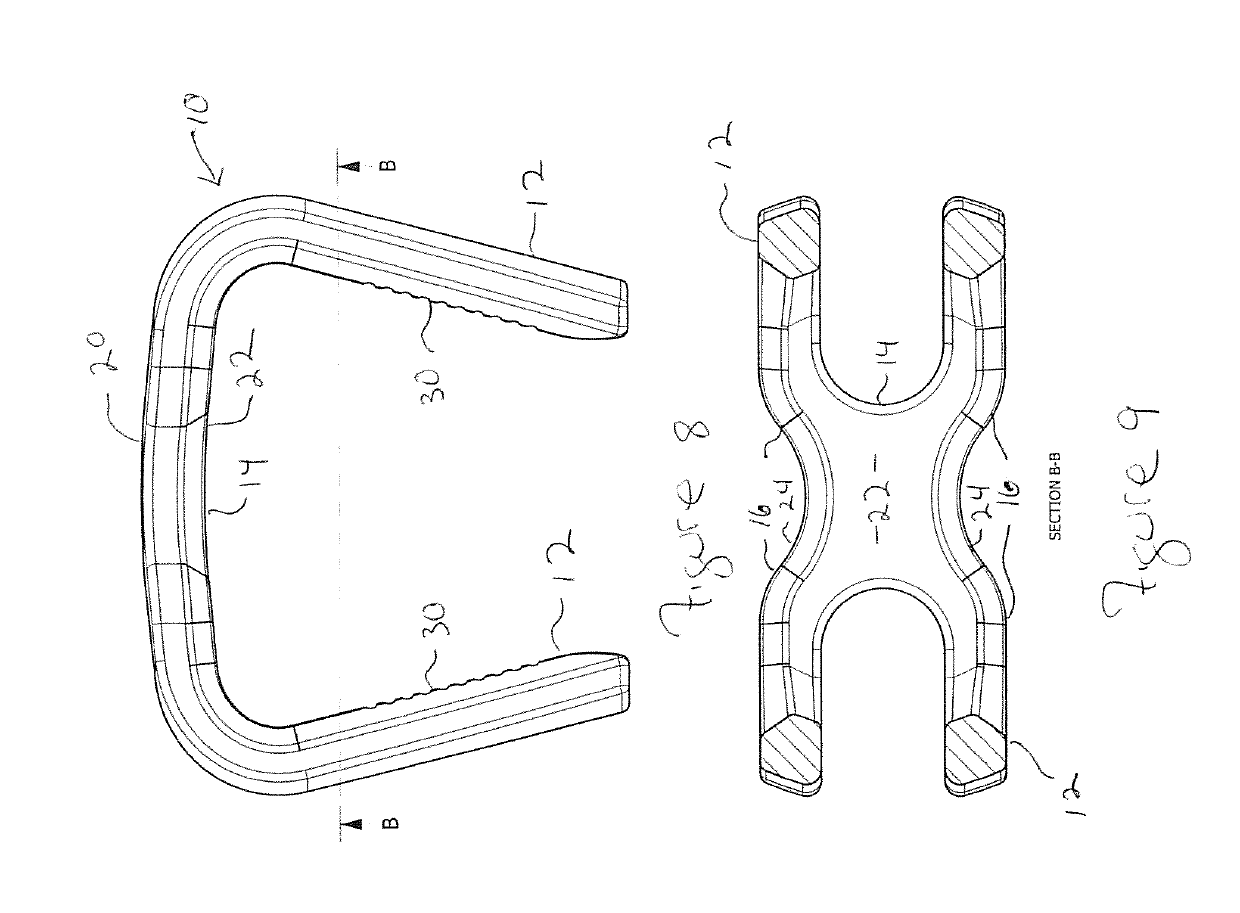

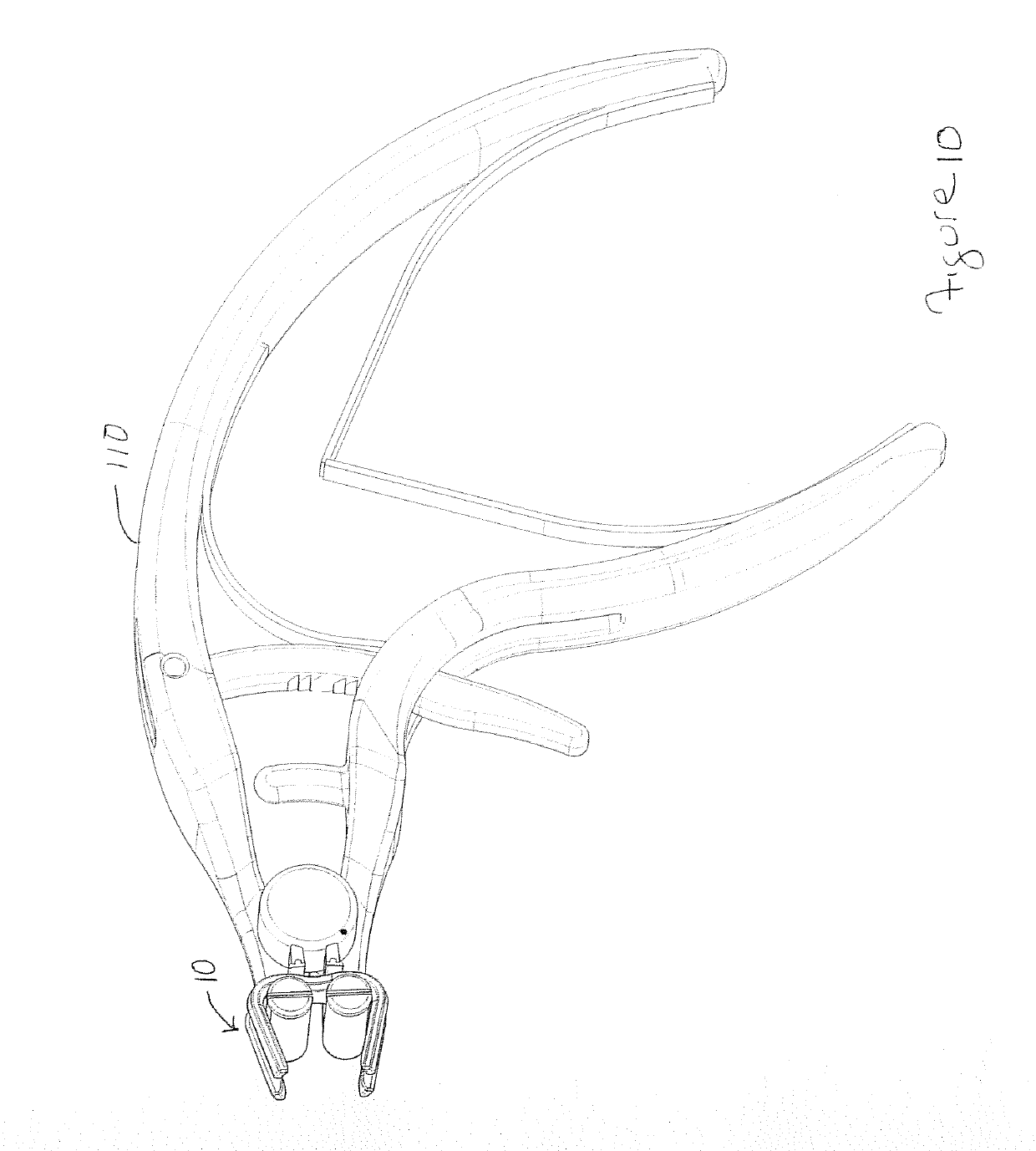

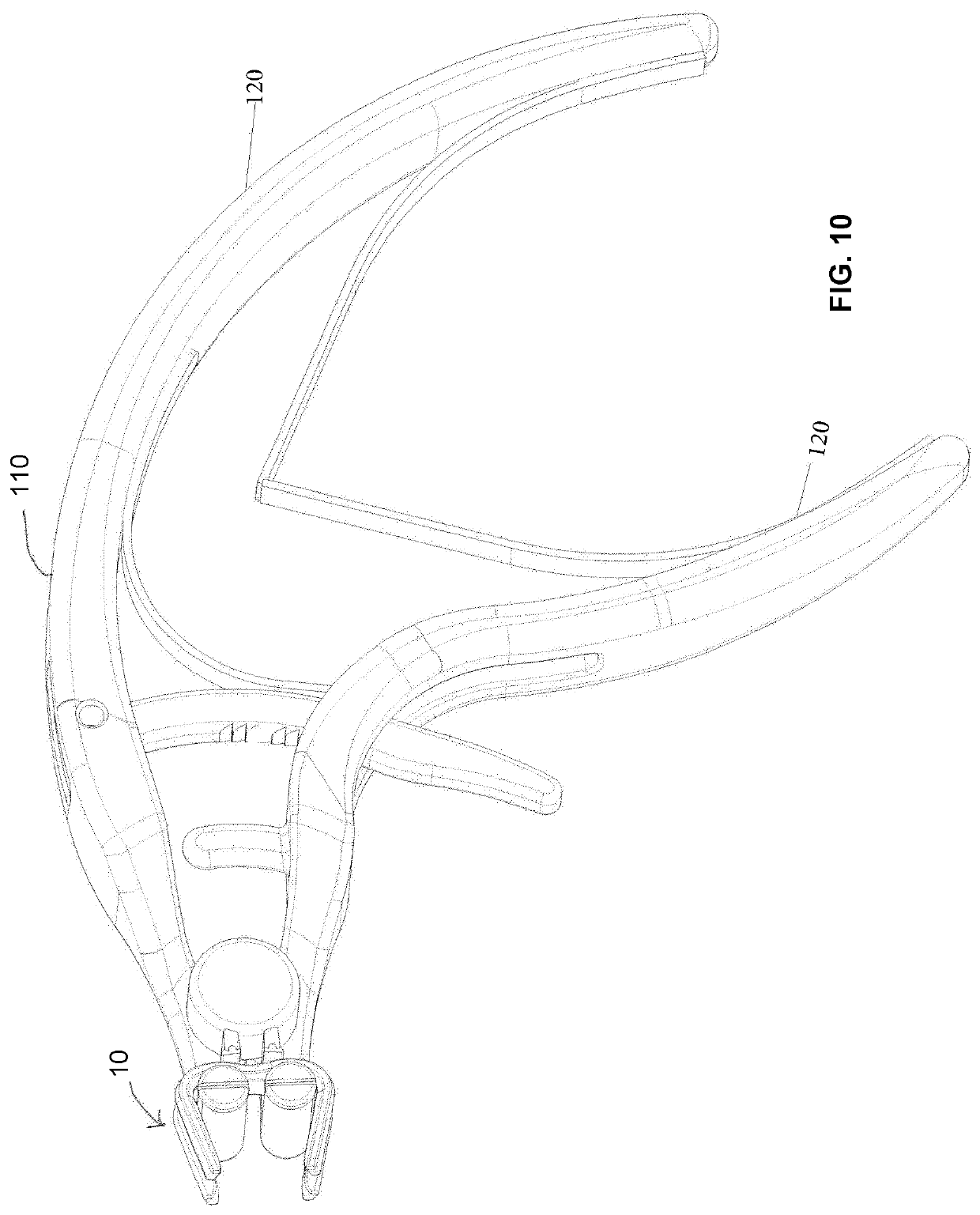

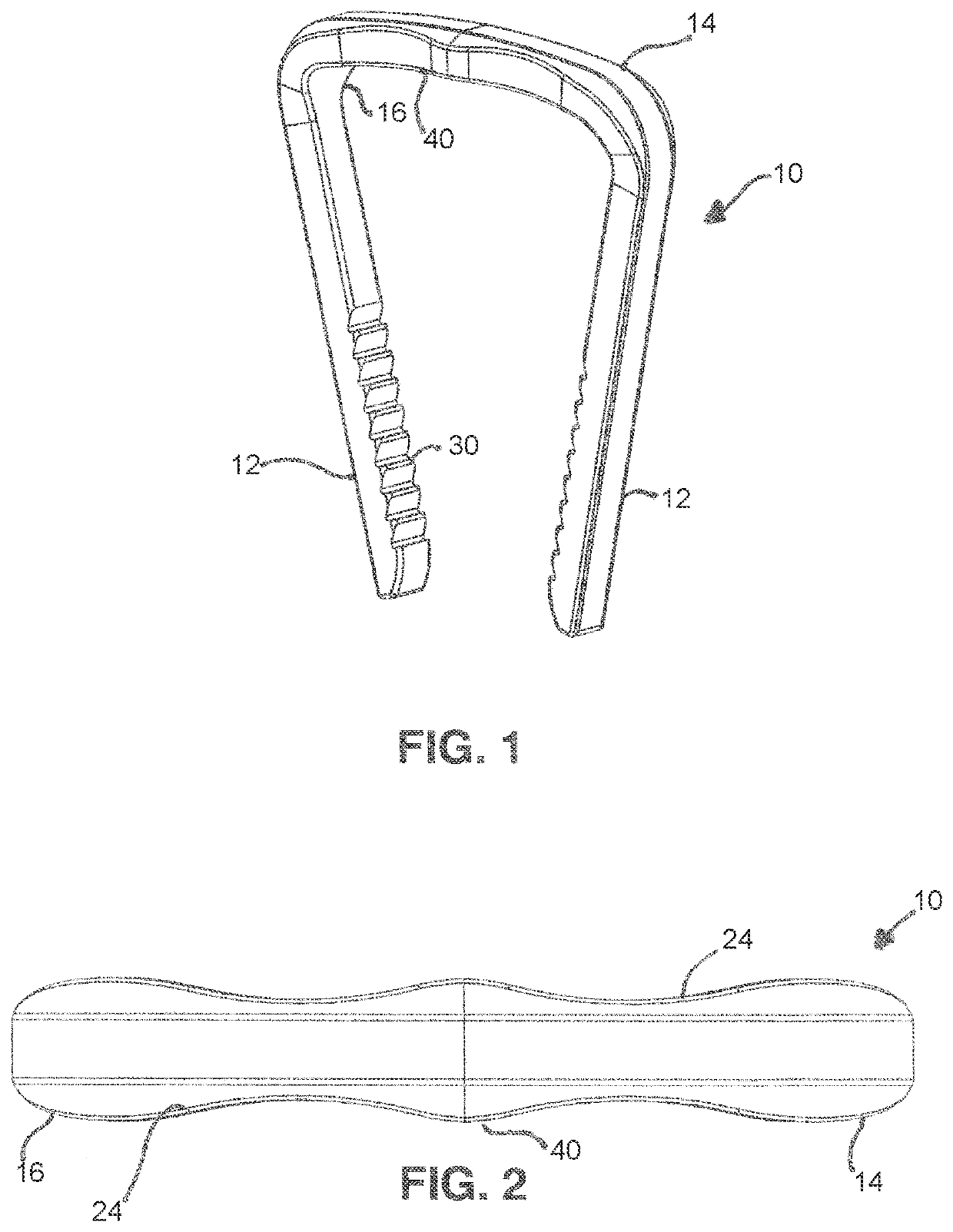

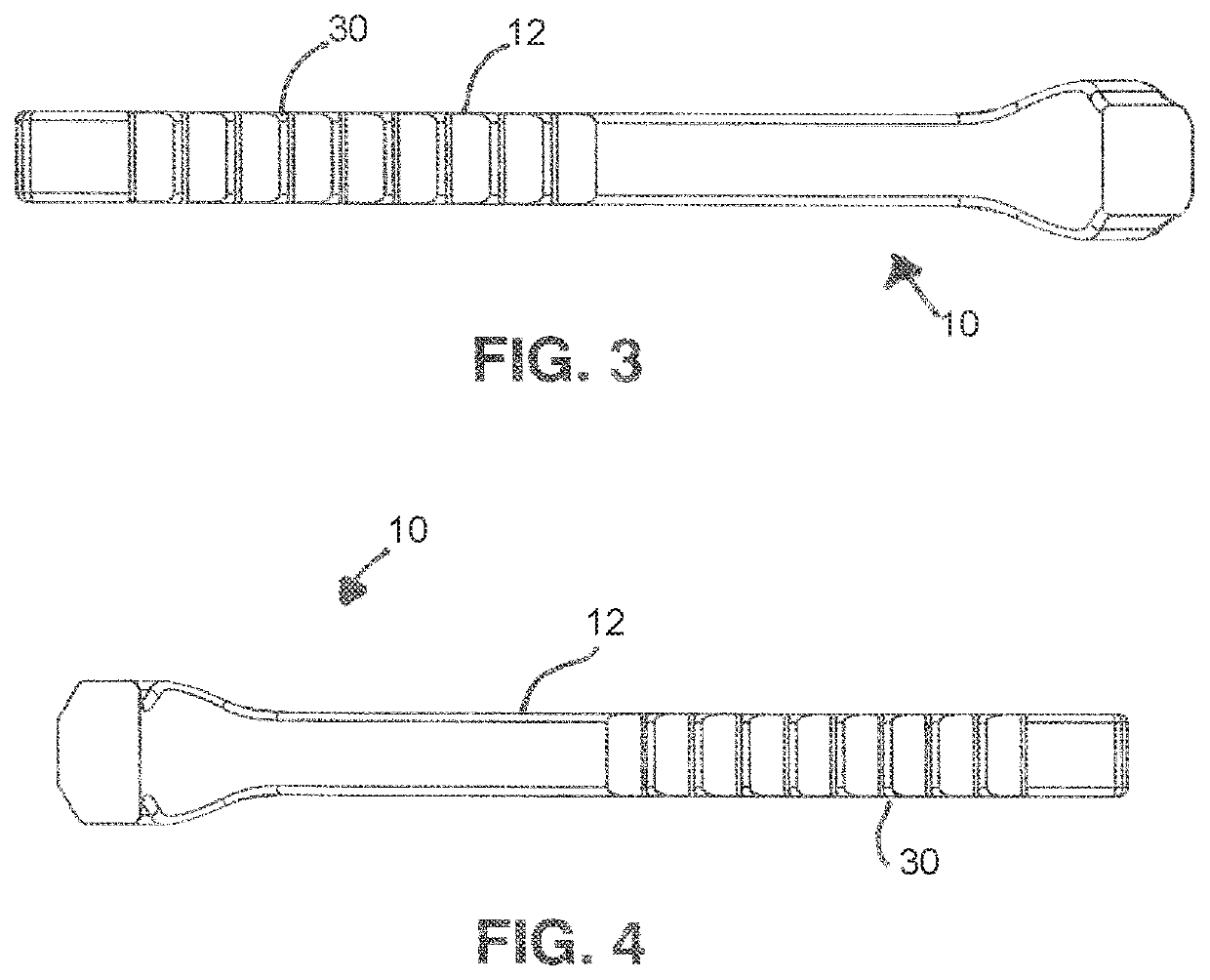

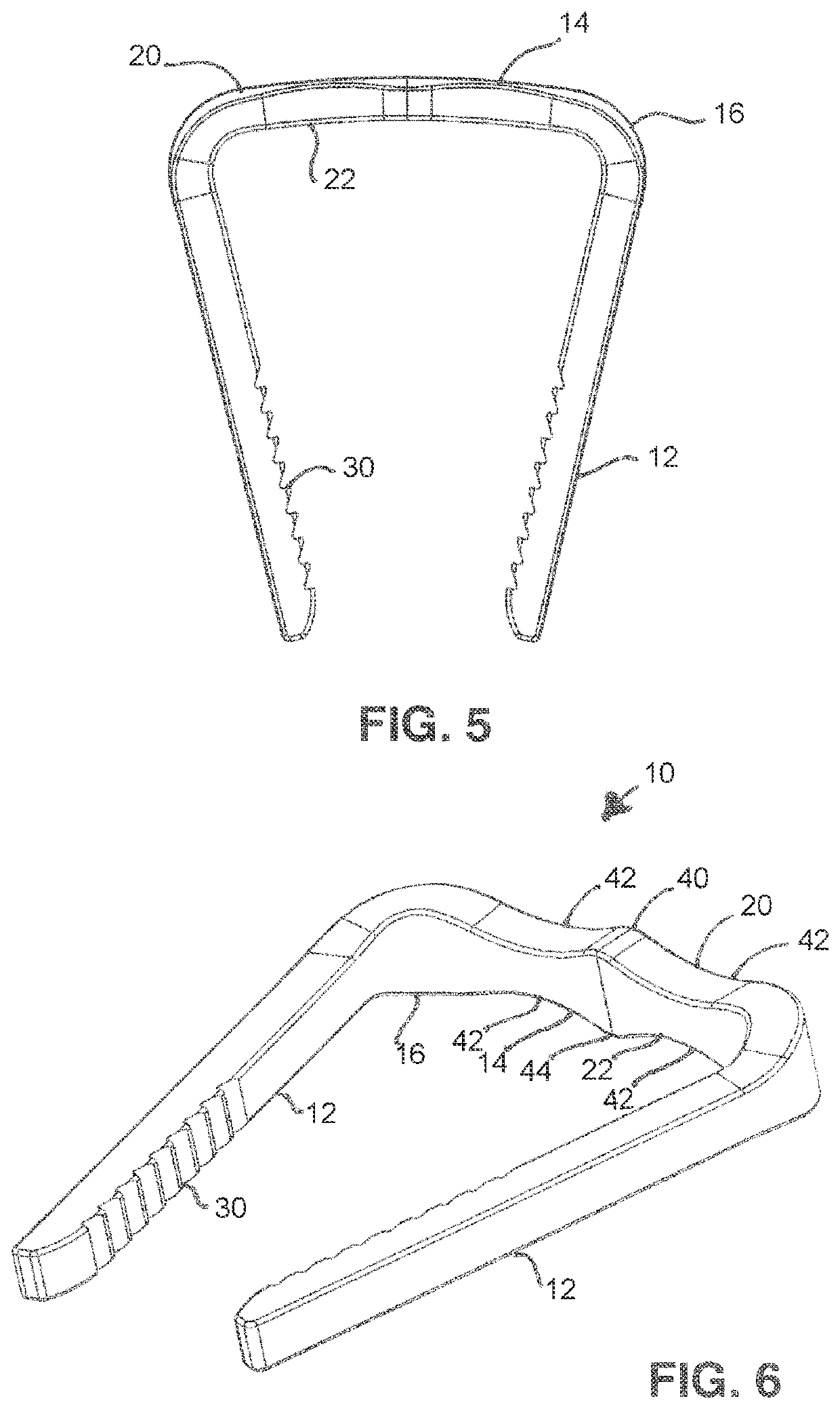

Superelastic bone compression staple

ActiveUS20190192140A1Uniform cross-sectional shapeIncrease holdingsStaplesNailsEngineeringSpherical form

Owner:ORTHO SOLUTIONS HLDG LTD

Photo sensitive resin compositon, optical spacer, protective film, coloring pattern, display device and substrate thereof

ActiveCN101470350AHigh sensitivityExcellent mechanical propertiesPhotomechanical apparatusLiquid stateSide chain

The present invention relates to a photosensitive resin compound, an optical spacer, a protective film, a coloring pattern, a display device and a substrate thereof. The photosensitive resin compound provided by the invention comprises the following components: (A) a resin which is provided with branched structure and / or alicyclic ring structure on the side chain, acidic group and substituted alkyl that is provided with two ethylenic linkage type unsaturated bonds, (B) a polymeric compound which is provided with ethylenic linkage type unsaturated bond, and (C) a photopolymerization initiatingagent. The photosensitive resin compound can form a pattern structure or protective film which has the advantages of high sensitivity, excellent storability in liquid state, excellent ageing stability and mechanical characteristic of photosensitive film after film forming.

Owner:FUJIFILM CORP

Superelastic bone compression staple

Owner:ORTHO SOLUTIONS HLDG LTD

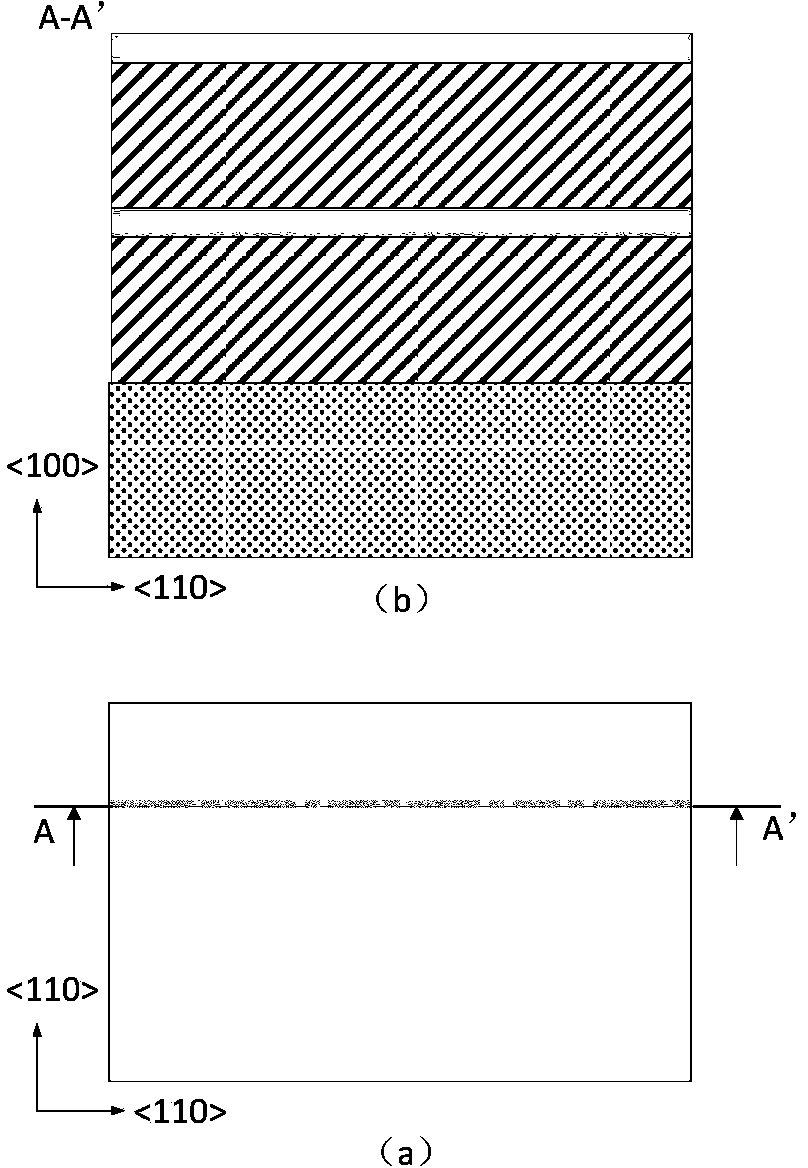

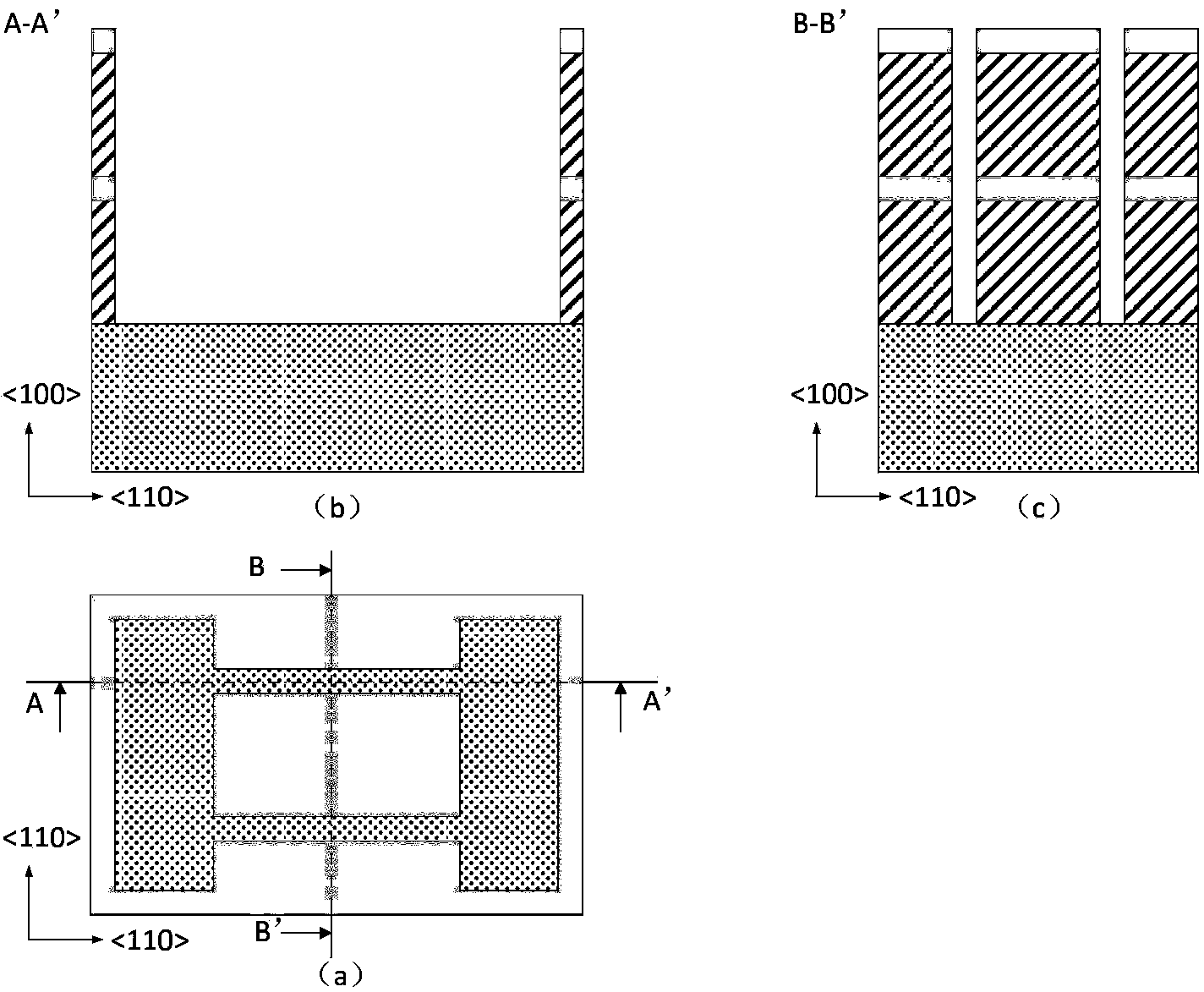

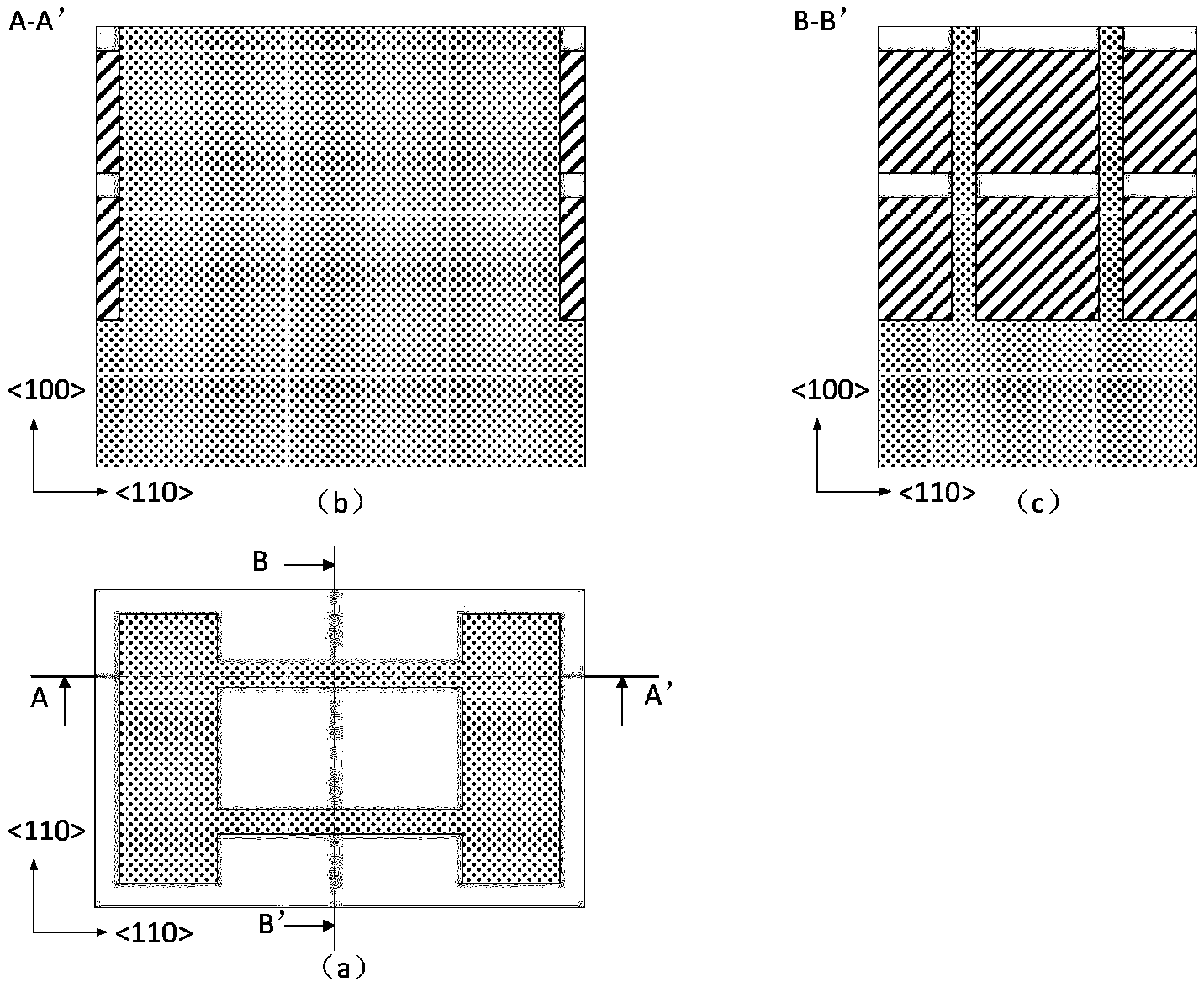

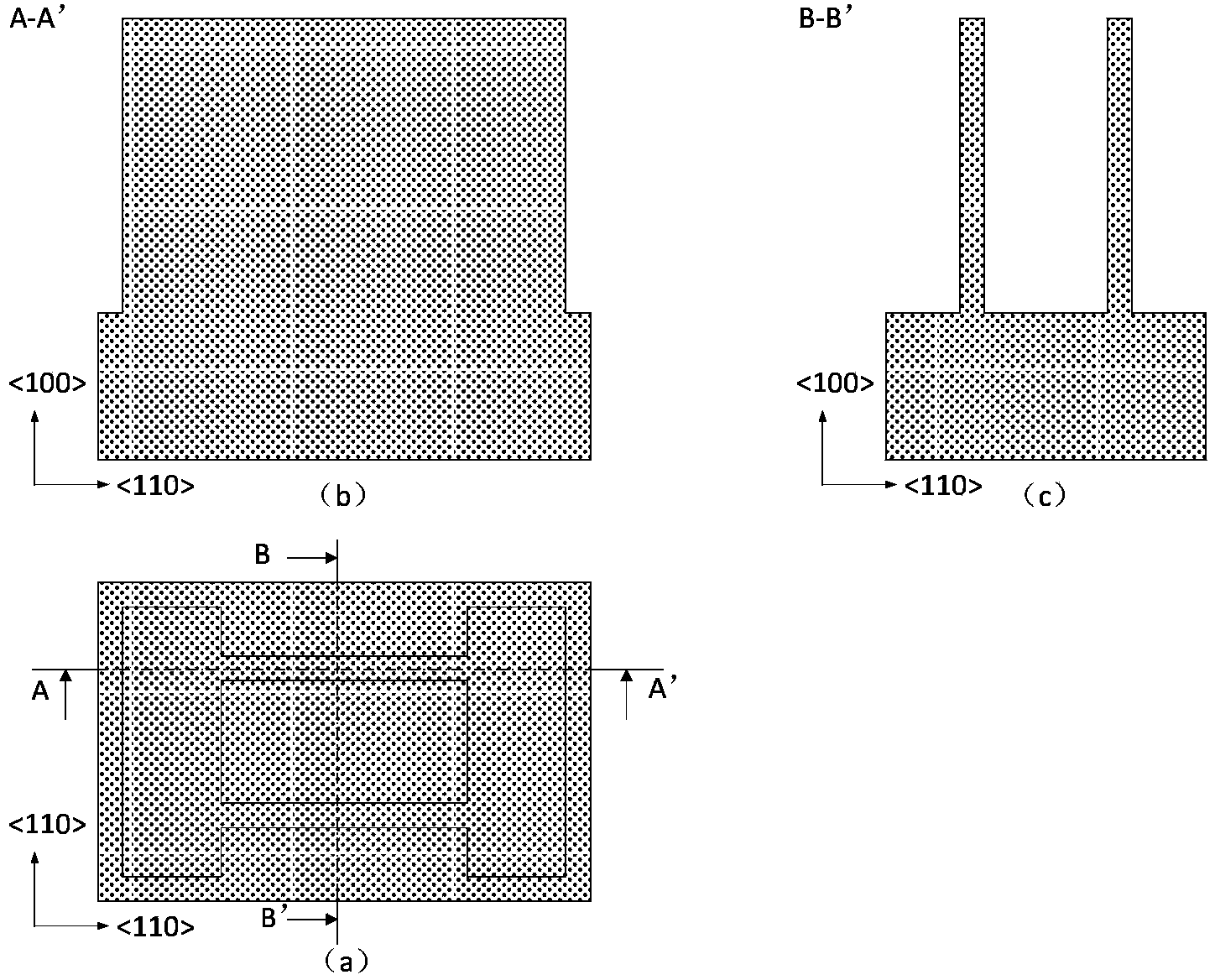

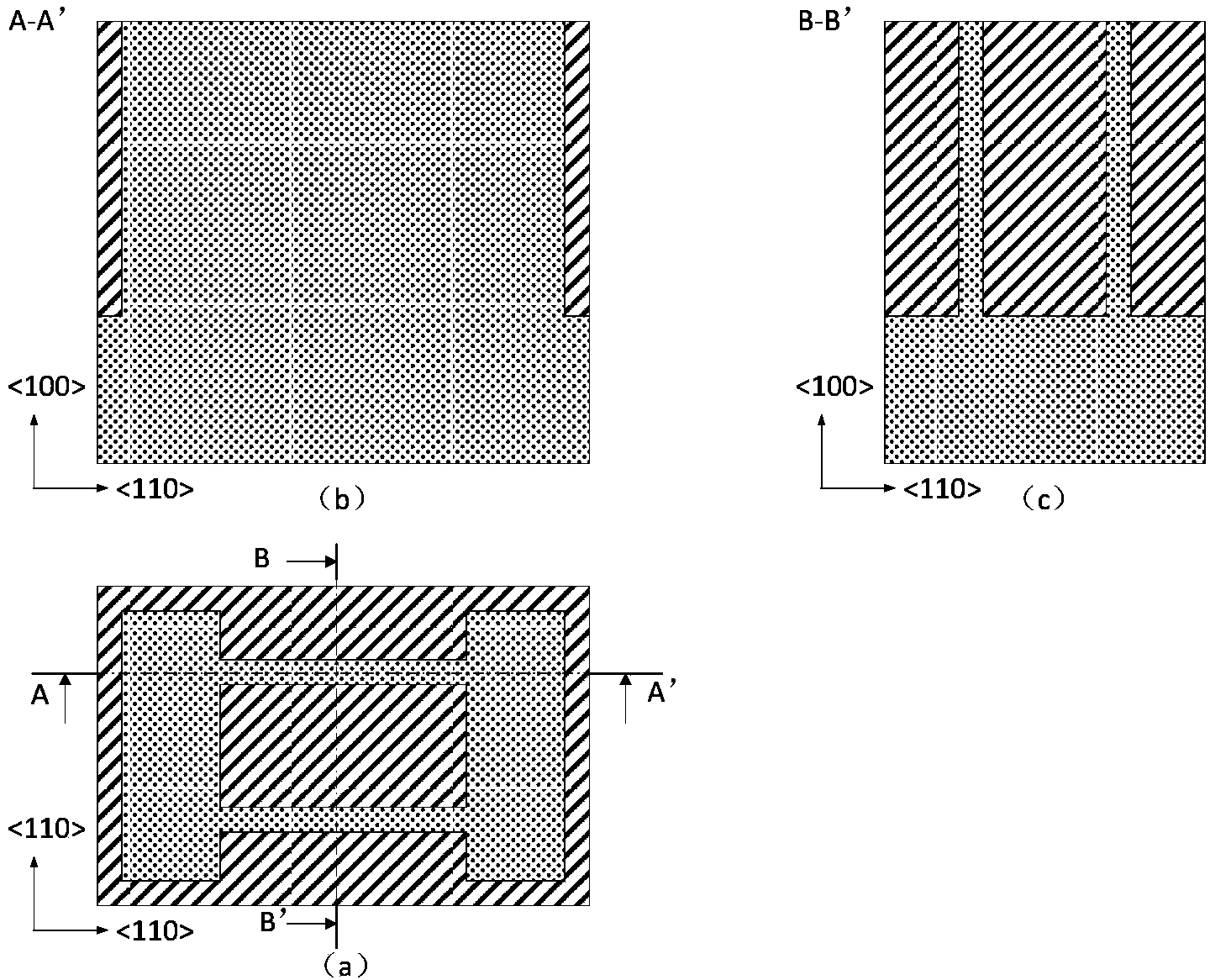

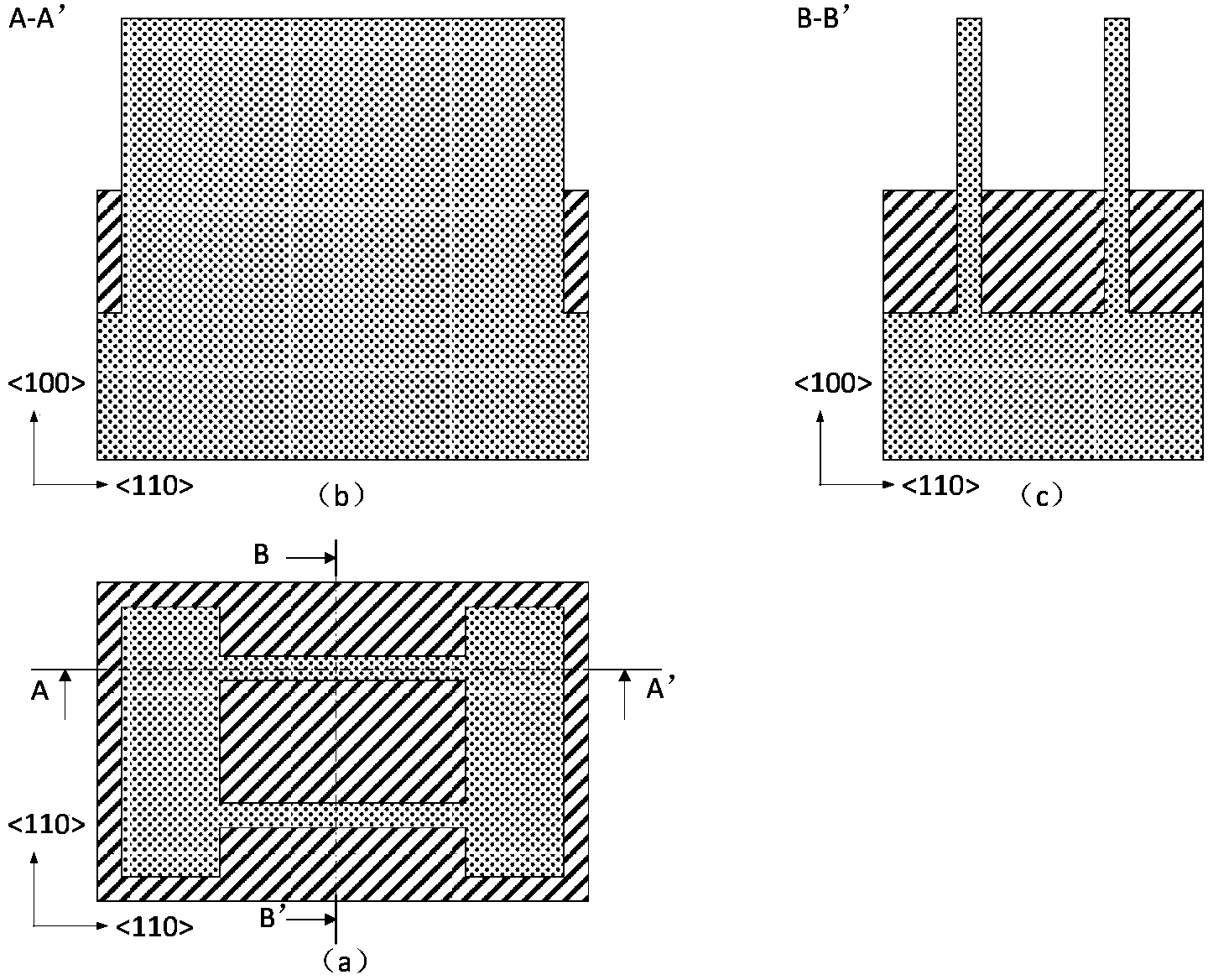

Method for preparing plurality of layers of superfine silicon lines

ActiveCN103824759AUniform positionUniform cross-sectional shapeNanoinformaticsSemiconductor/solid-state device manufacturingNanowireIntegrated circuit manufacturing

The invention relates to a method for preparing a plurality of layers of superfine silicon lines. The method comprises the following steps: preparing a silicon etching masking layer; extending to form Fin and source drain regions on two ends of the Fin; and forming the plurality of layers of superfine silicon lines. The method has the advantages that the positions of the superfine lines can be accurately defined through the deposition of an atomic layer, and the controllability is good; the anisotropy etching on silicon stops automatically, a process window is large, and the sections of nano lines obtained by etching are uniform and smooth in appearance; the process for forming a plurality of layers of side wall etching masks by a method of firstly preparing masks and then extending a channel is simple, and the plurality of layers of side wall masks can be obtained only by one etching of the extension window regardless of the number of masking layers; the lines with sizes of less than 10nm can be prepared by combining oxidization technology, thus meeting the requirement of the key process of small-sized devices; polycrystalline silicon can be subjected to wet etching with a TMAH solution, and the operation is simple, convenient and safe; metal ions are not introduced, and the method is applicable to the integrated circuit manufacturing technology; the method is entirely compatible with a bulk silicon planar transistor process, and the process cost is small.

Owner:PEKING UNIV

Method of machining semiconductor wafer-use polishing pad and semiconductor wafer-use polishing pad

InactiveCN1592955AReduce surface roughnessHigh dimensional accuracyPigmenting treatmentSemiconductor/solid-state device manufacturingWater insolubleSurface roughness

An object of the invention is to provide a processing method of a polishing pad for semiconductor wafer capable of forming a groove, a concave portion, a through hole and the like having a small surface roughness of the inner surface of the groove and the like of 20 mu m or less, a high dimensional accuracy and a uniform cross-sectional shape, and a polishing pad for semiconductor wafer. In the present processing method, a surface of a polishing pad comprising a water-insoluble matrix containing a crosslinked polymer and a water-soluble particle dispersed in the water-insoluble matrix is processed by cutting and the like. Additionally, when a groove and the like are formed, it is preferable that a polishing pad is placed on one surface side of a machining table having a sucking hole, the pad is fixed on the one surface side of the machining table by vacuuming sucking it from the other surface of the machining table, and then a groove and the like are formed.

Owner:JSR CORPORATIOON

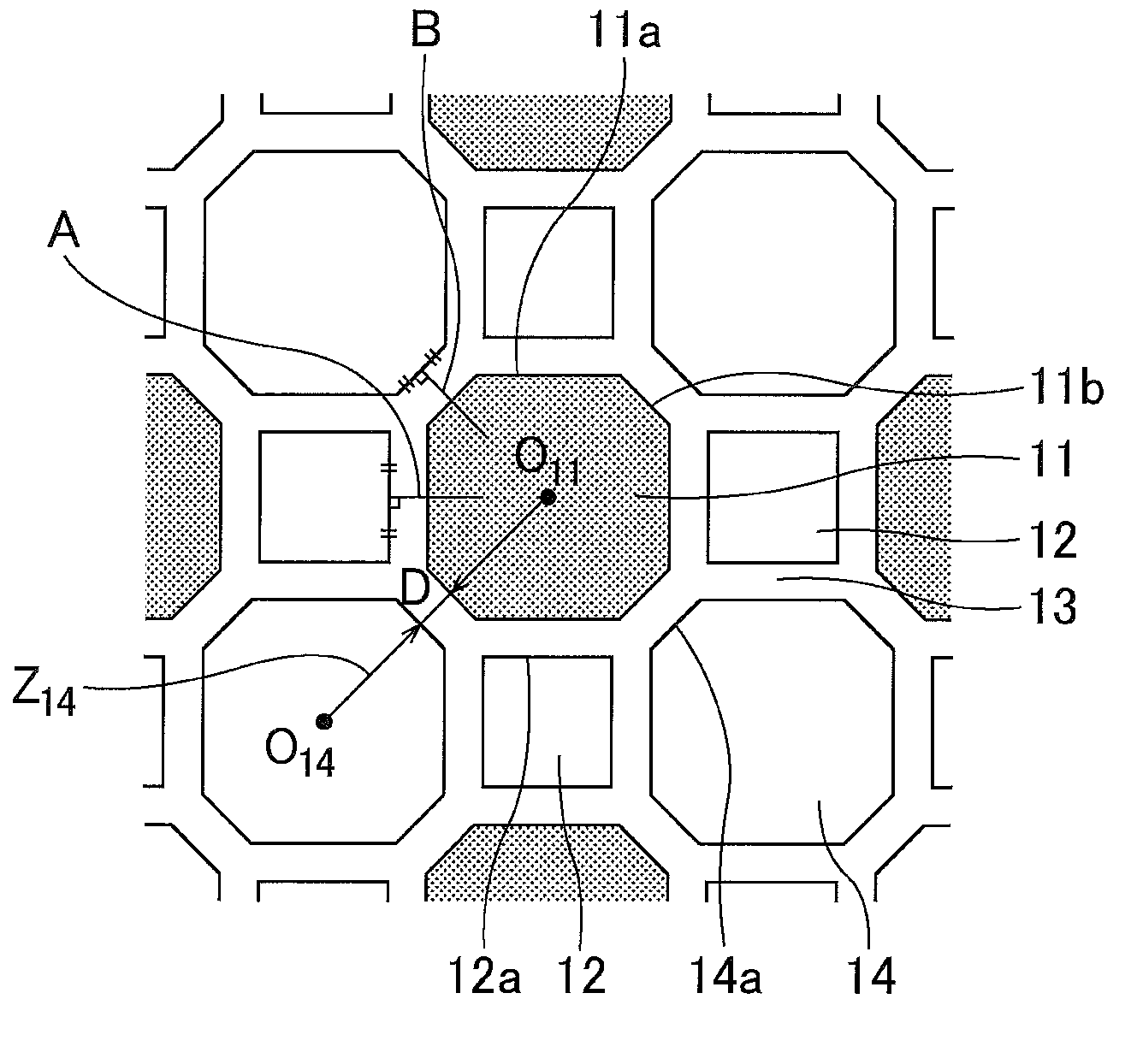

Honeycomb filter

ActiveUS20150033691A1Uniform cross-sectional shapeInternal combustion piston enginesDispersed particle filtrationHoneycombExhaust gas emissions

A honeycomb filter includes a plurality of cells and porous cell walls. The plurality of cells include exhaust gas introduction cells and exhaust gas emission cells. Each of the exhaust gas emission cells is adjacently surrounded fully by the exhaust gas introduction cells across the porous cell walls. The exhaust gas introduction cells include first exhaust gas introduction cells and second exhaust gas introduction cells. Each of the first exhaust gas introduction cells has the cross sectional area equal to or smaller than 0.7 mm2 in the cross section perpendicular to the longitudinal direction of the plurality of cells.

Owner:IBIDEN CO LTD

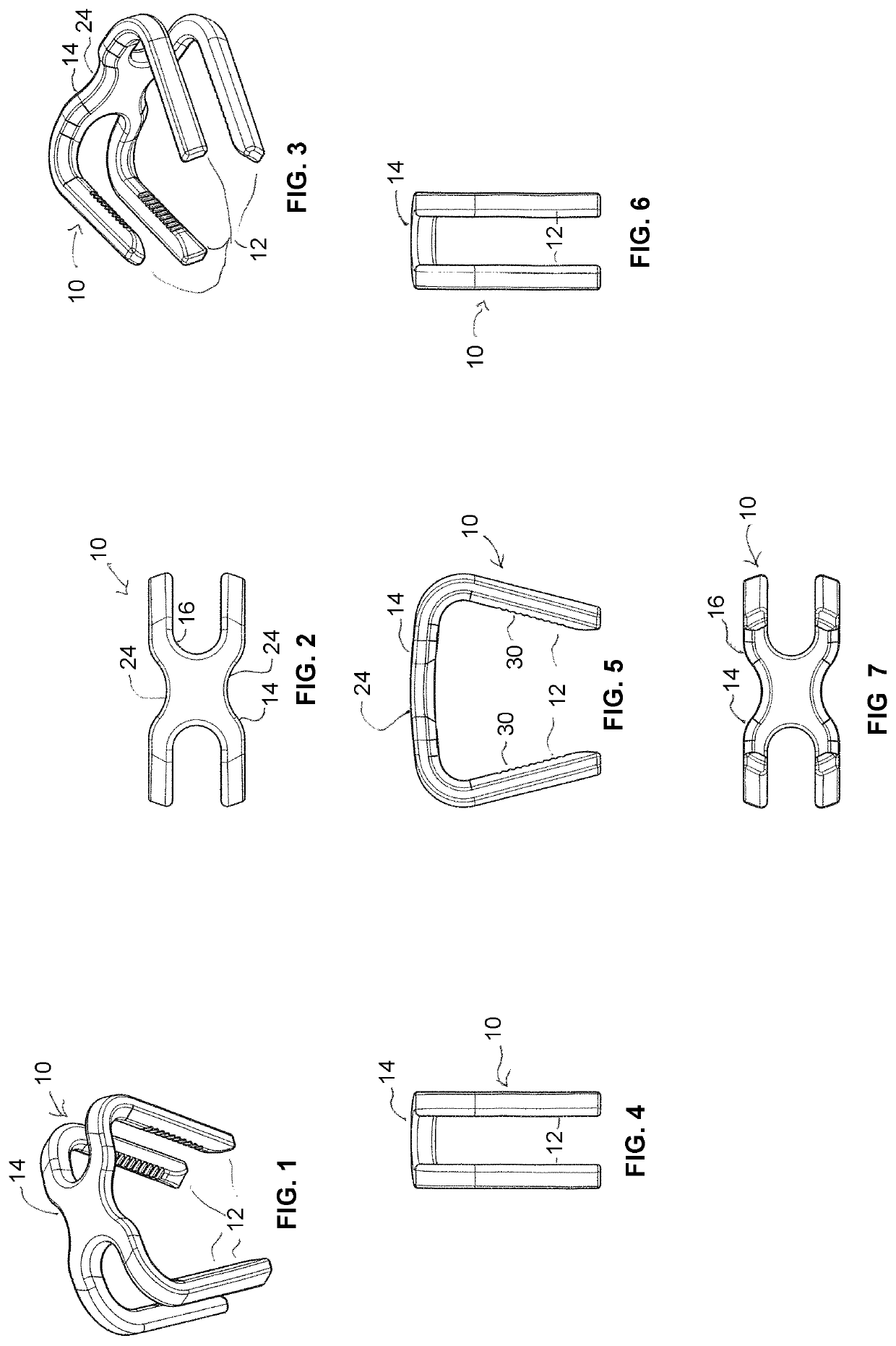

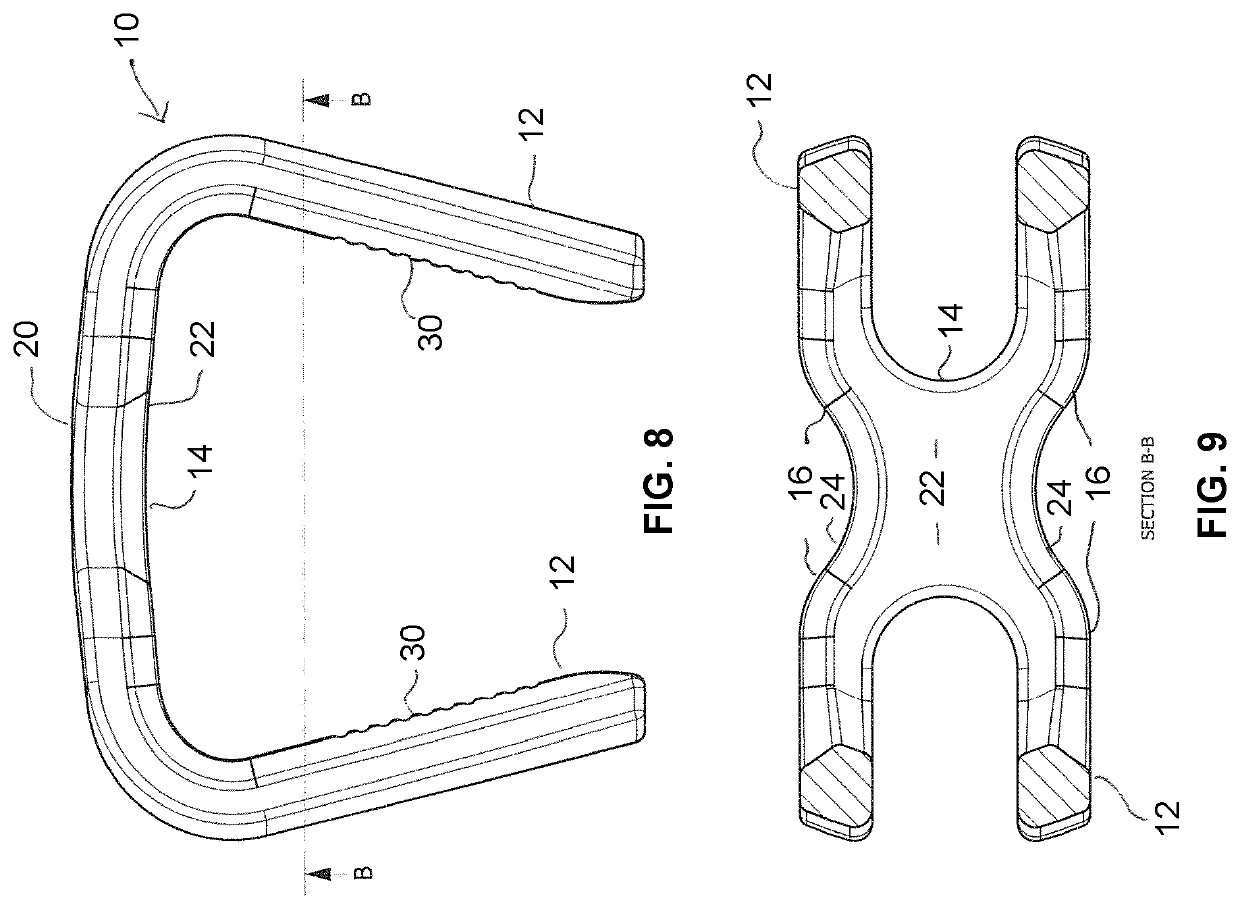

Reinforced bridge superelastic bone compression staple and inserter system

The invention is a staple comprising a bridge member having a top surface and an opposing bottom surface defining a thickness between and two lateral edges defining a width therebetween and either the thickness or the width includes a center flared area, such as a “diamond-like” shape meaning that it has a v-shape on opposing lateral edges flanked by opposing fillets to form an inserter mount area and the staple has a pair of legs spaced apart along the axis and each joined at a rounded flared shoulder to the bridge member. In a four-legged version the bridge has a waist.

Owner:ORTHO SOLUTIONS HLDG LTD

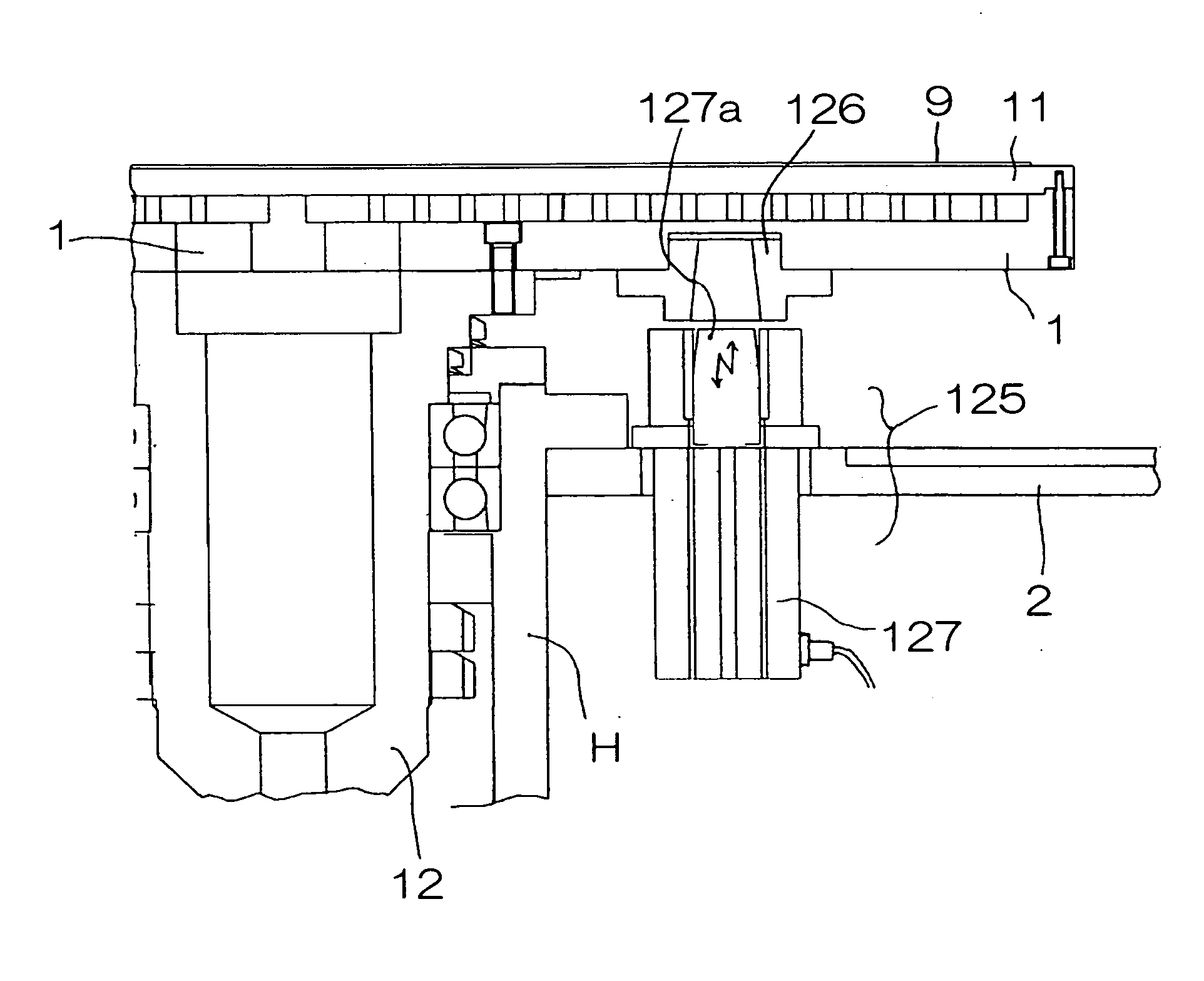

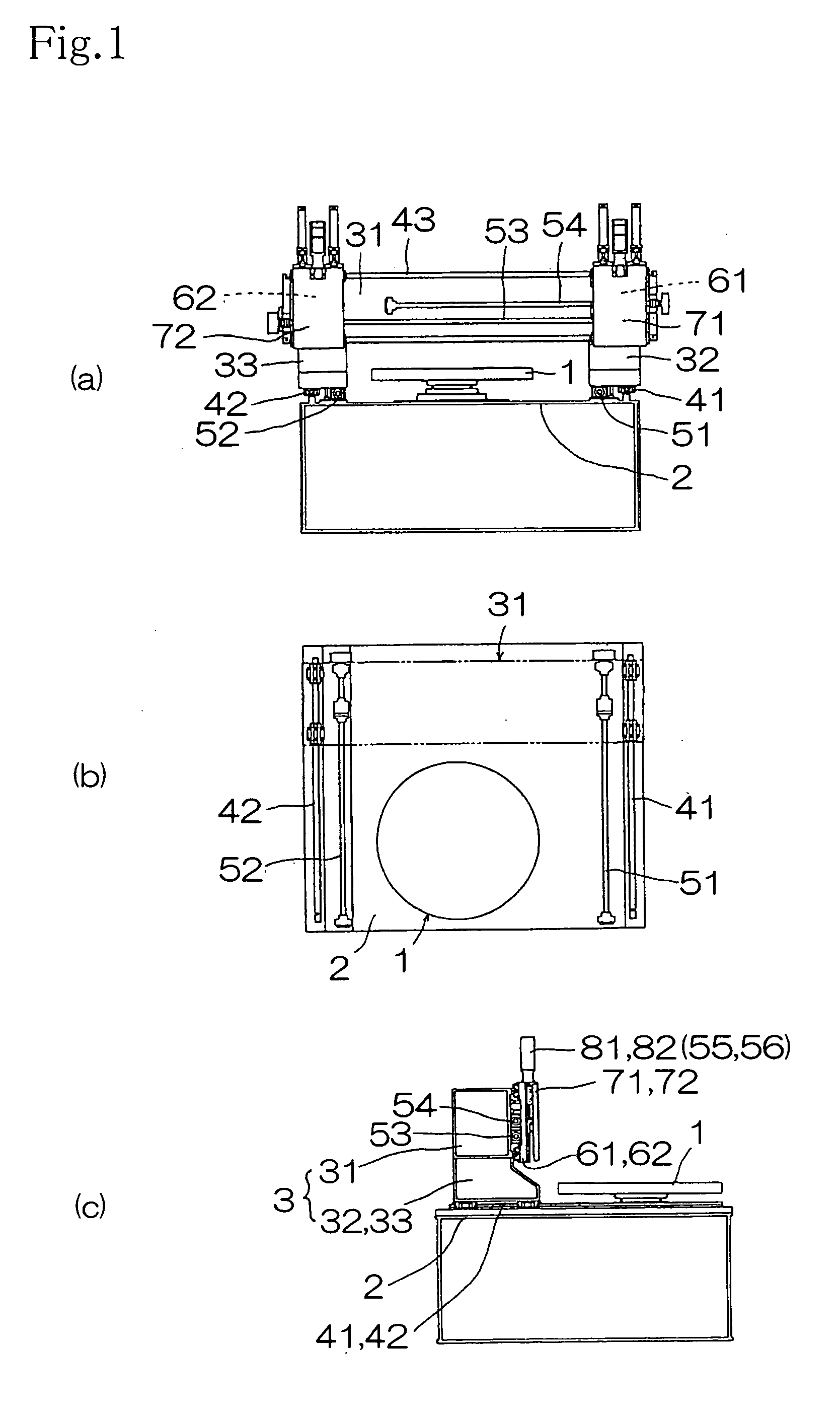

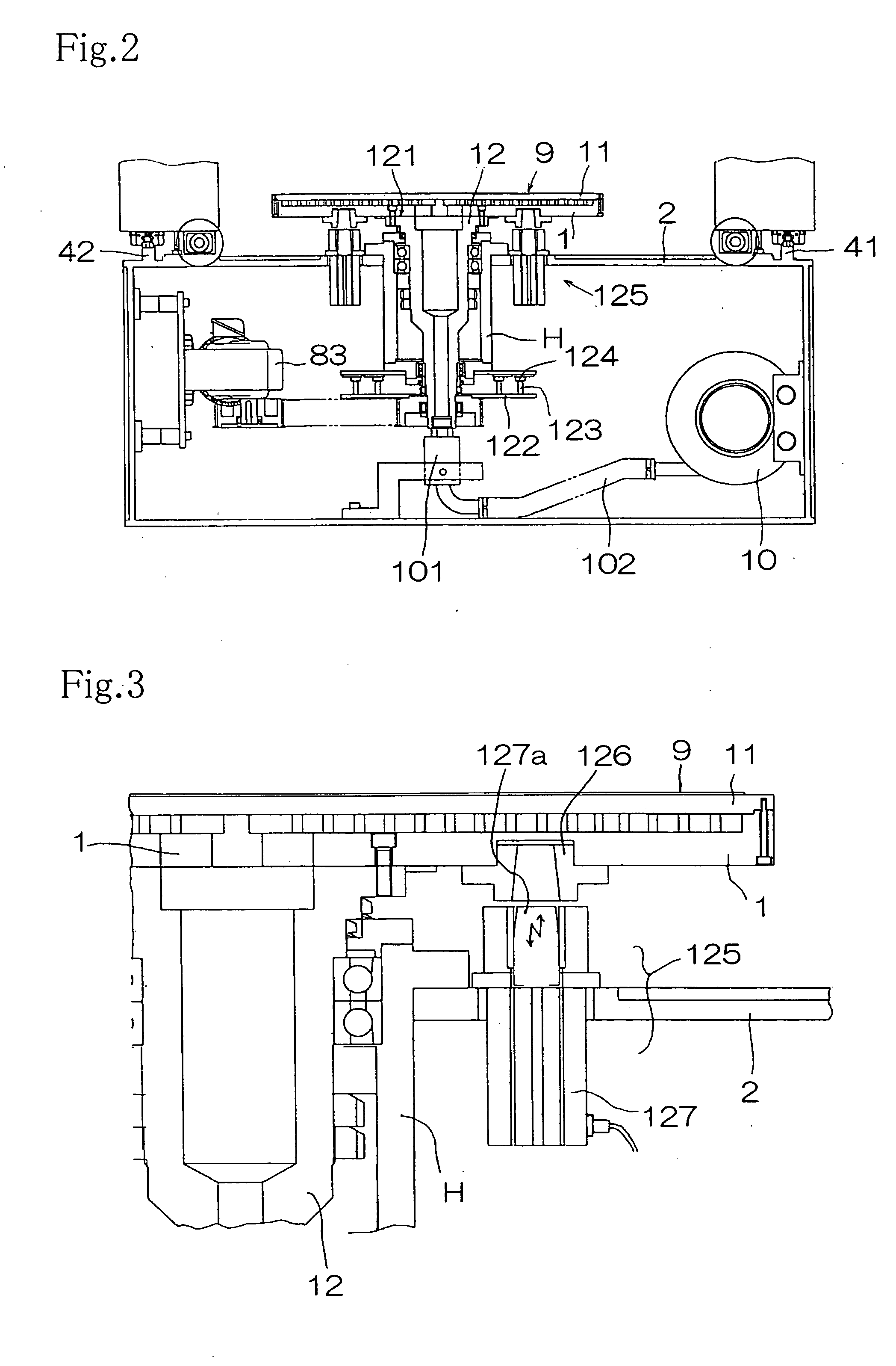

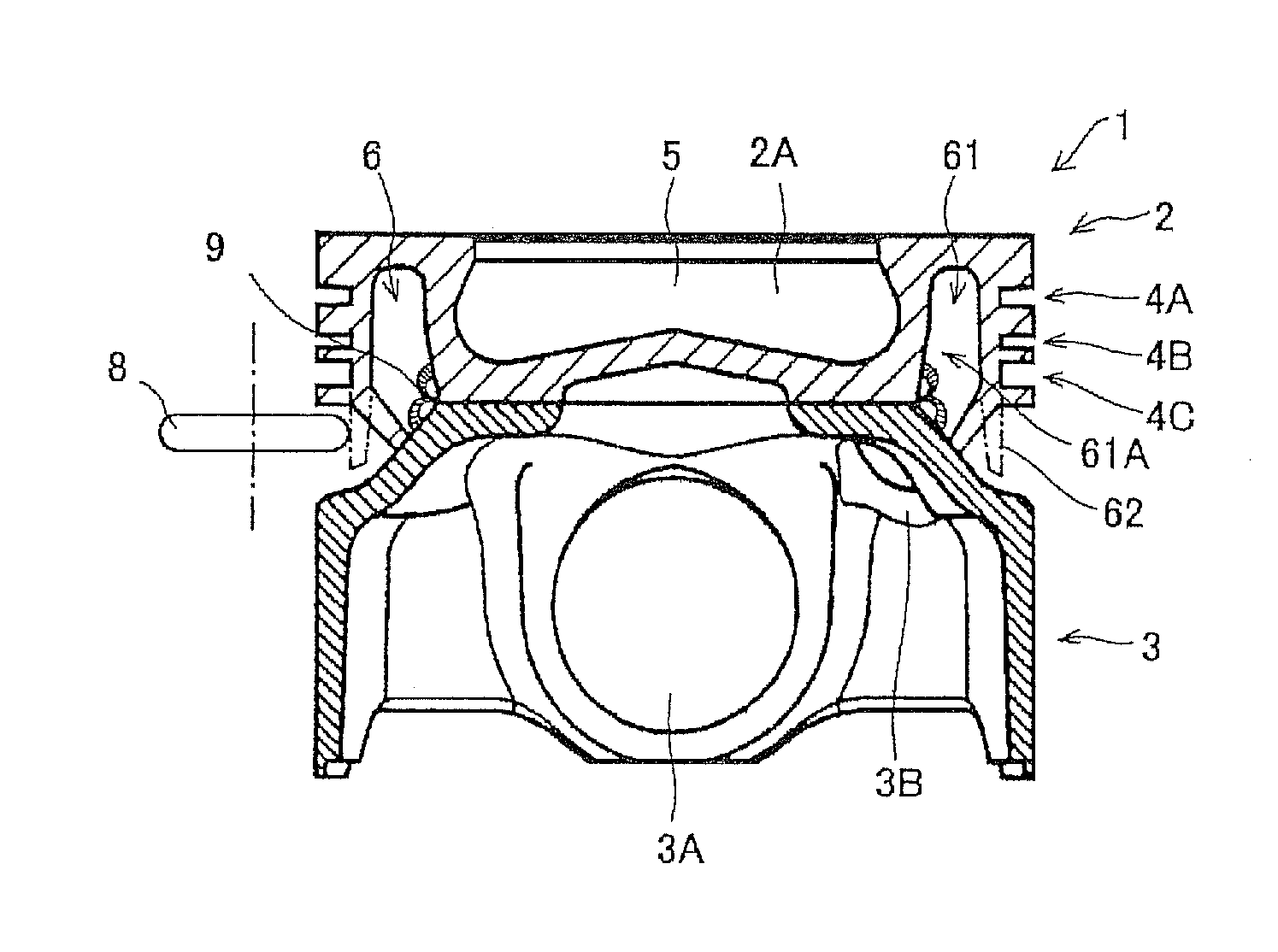

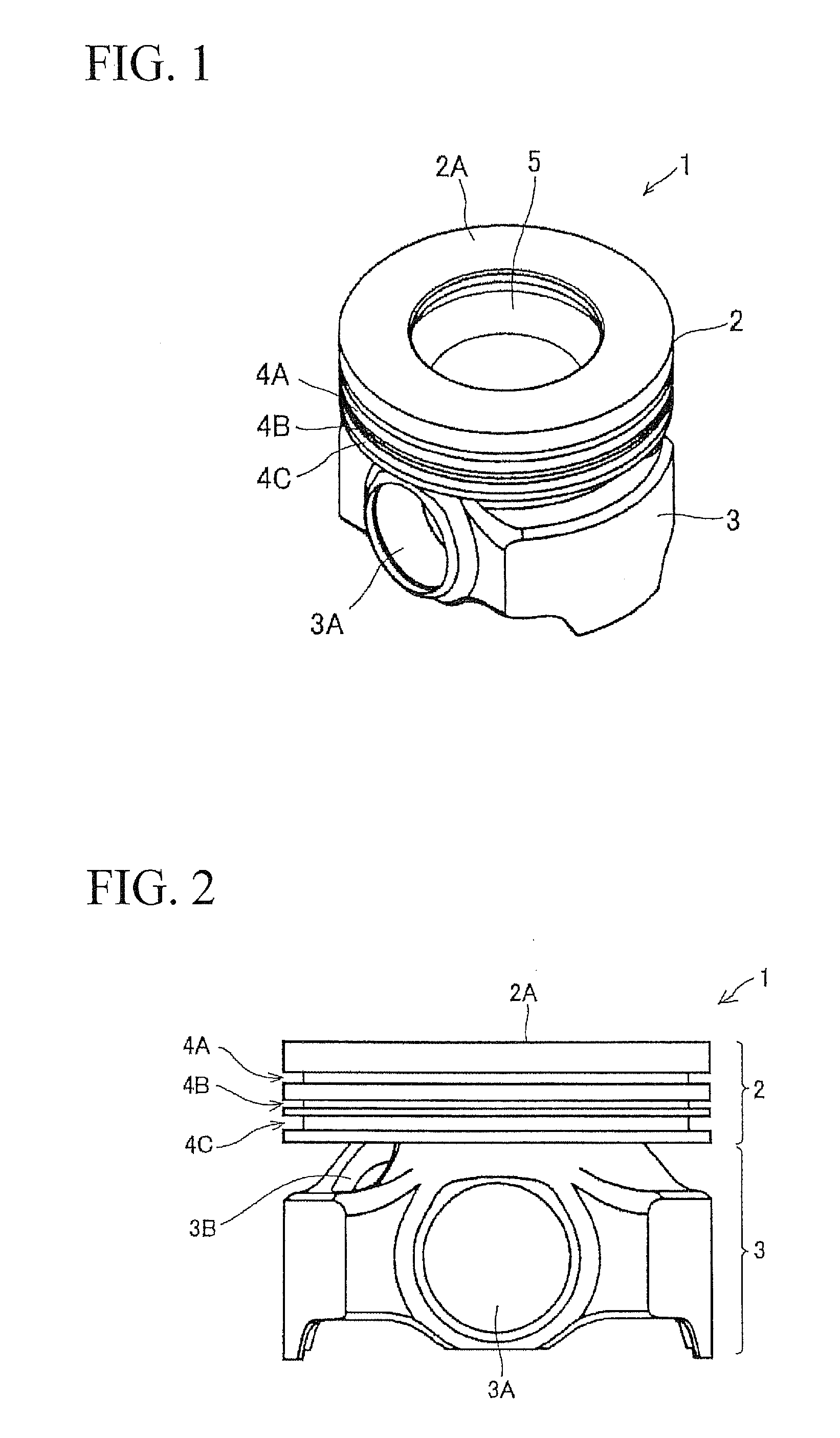

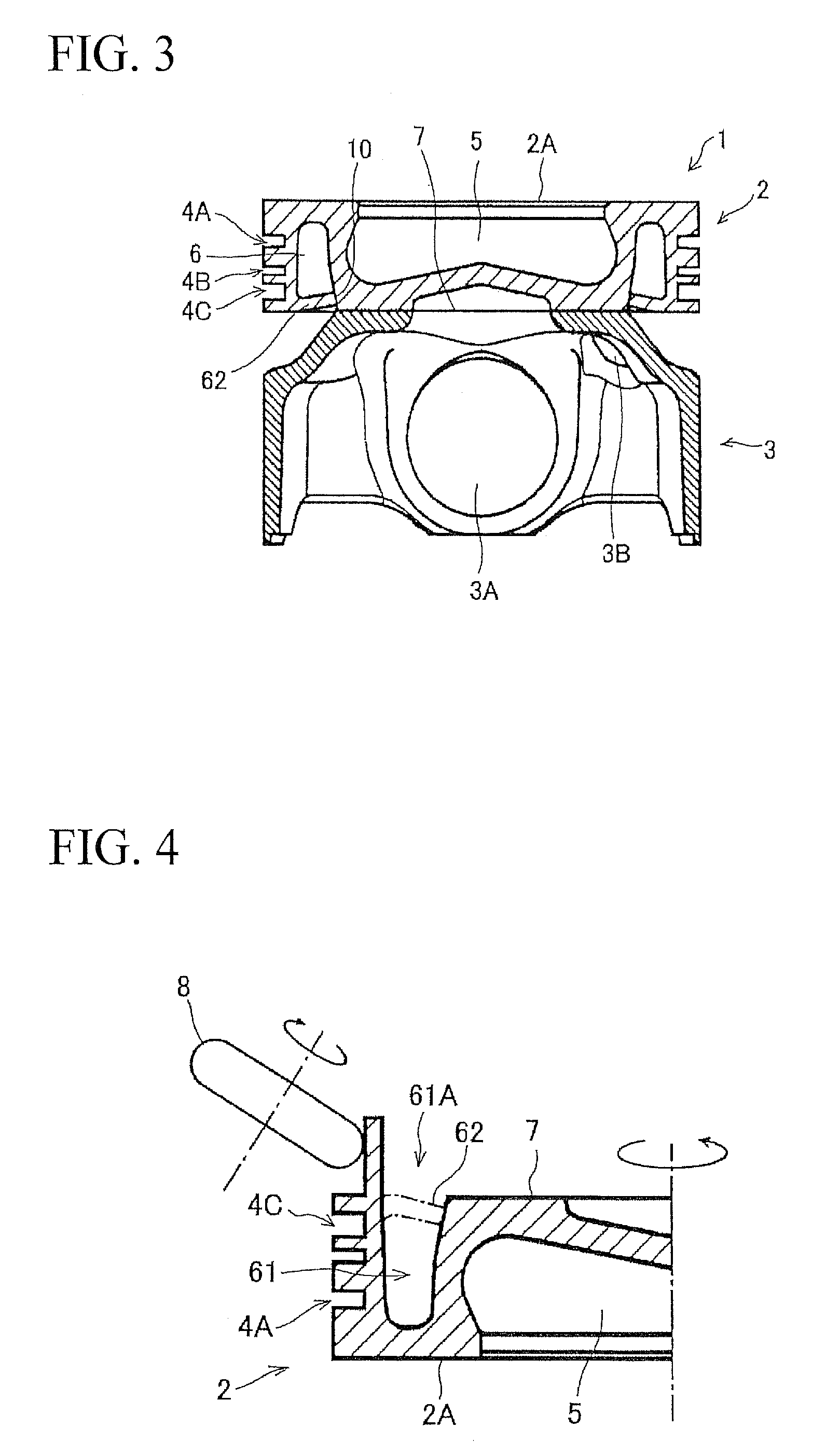

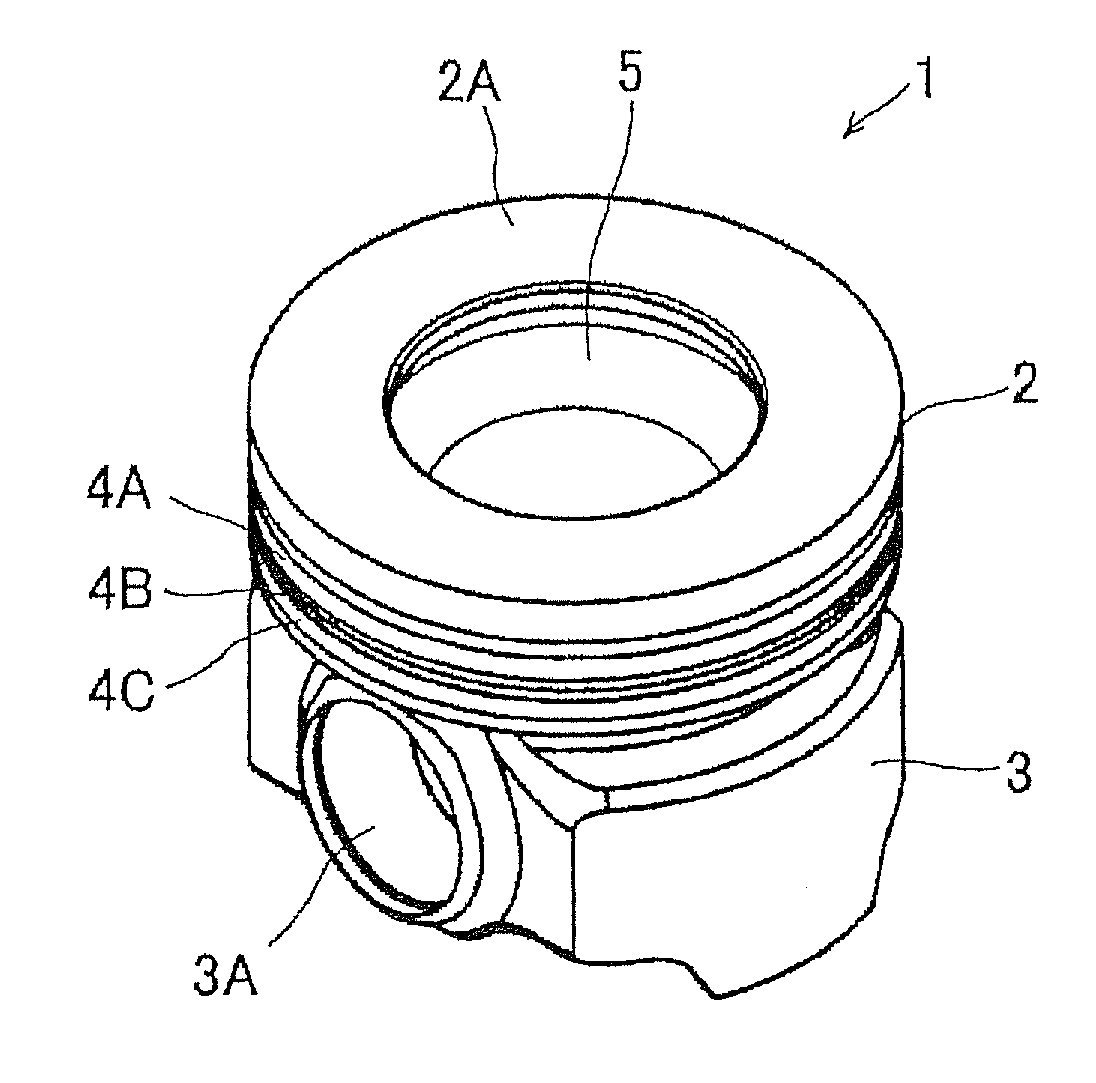

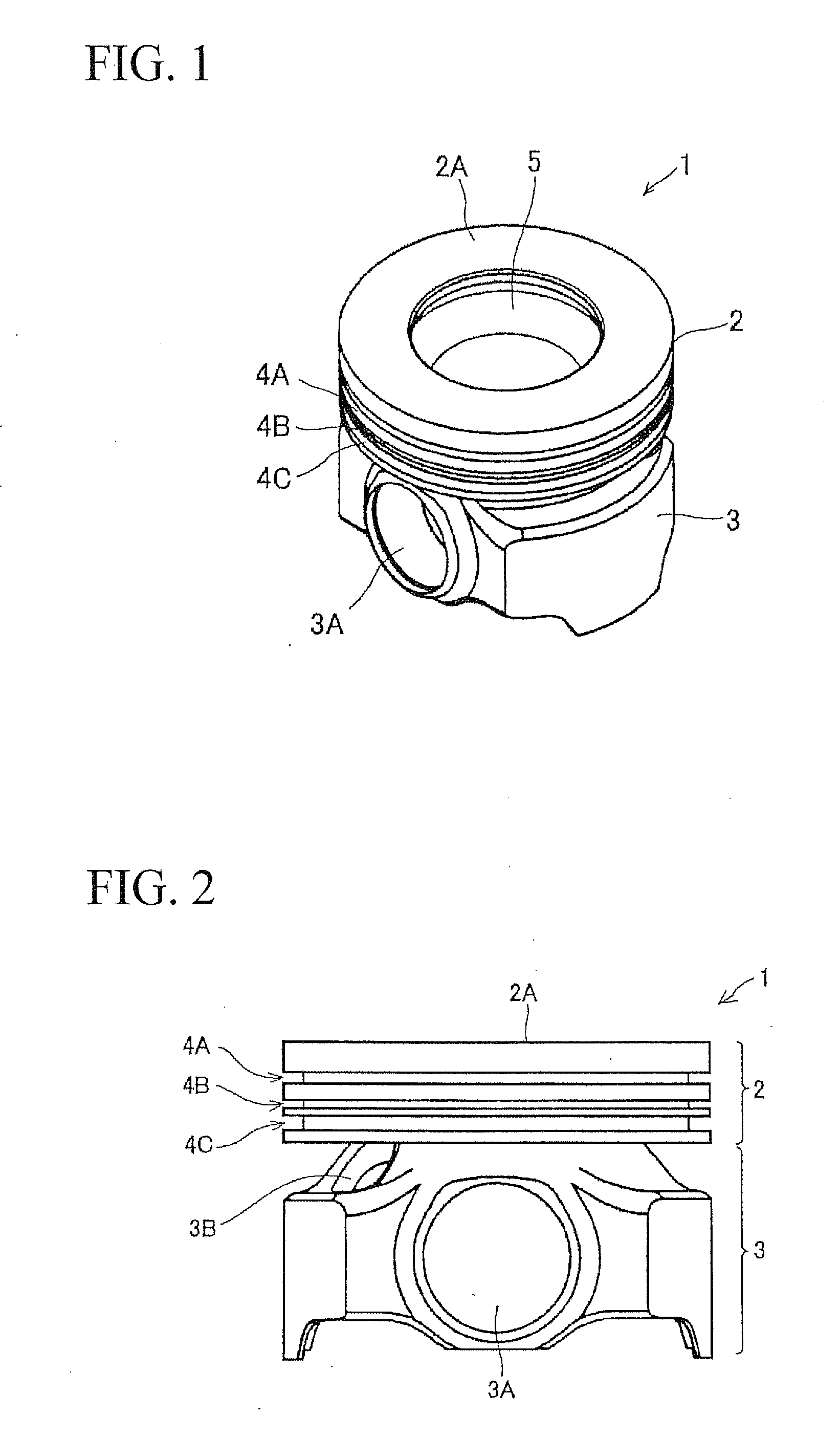

Method for producing piston for internal-combustion engine

ActiveUS8240039B2Speed up the flowReadily and well-formedValve arrangementsPlungersPiston ringInternal combustion engine

A method is provided for producing a piston for an internal-combustion engine of the structure in which a piston body which is composed of a crown having a groove for fitting a piston ring into an outer circumference surface and a skirt in connection with the bottom of the crown is provided with an annular cavity for flowing cooling liquid on an inside of the groove, the method comprising the steps of: forming the crown and the skirt individually; forming an annular groove for the annular cavity in the inner bottom of the crown and an annular rib in connection with the open edge of the annular groove before the crown and the skirt are joined together; bending the rib toward the opening of the annular groove by application of pressure to close the opening of the annular groove to thereby form the annular cavity; and joining the crown and the skirt together.

Owner:RIKEN FORGE +1

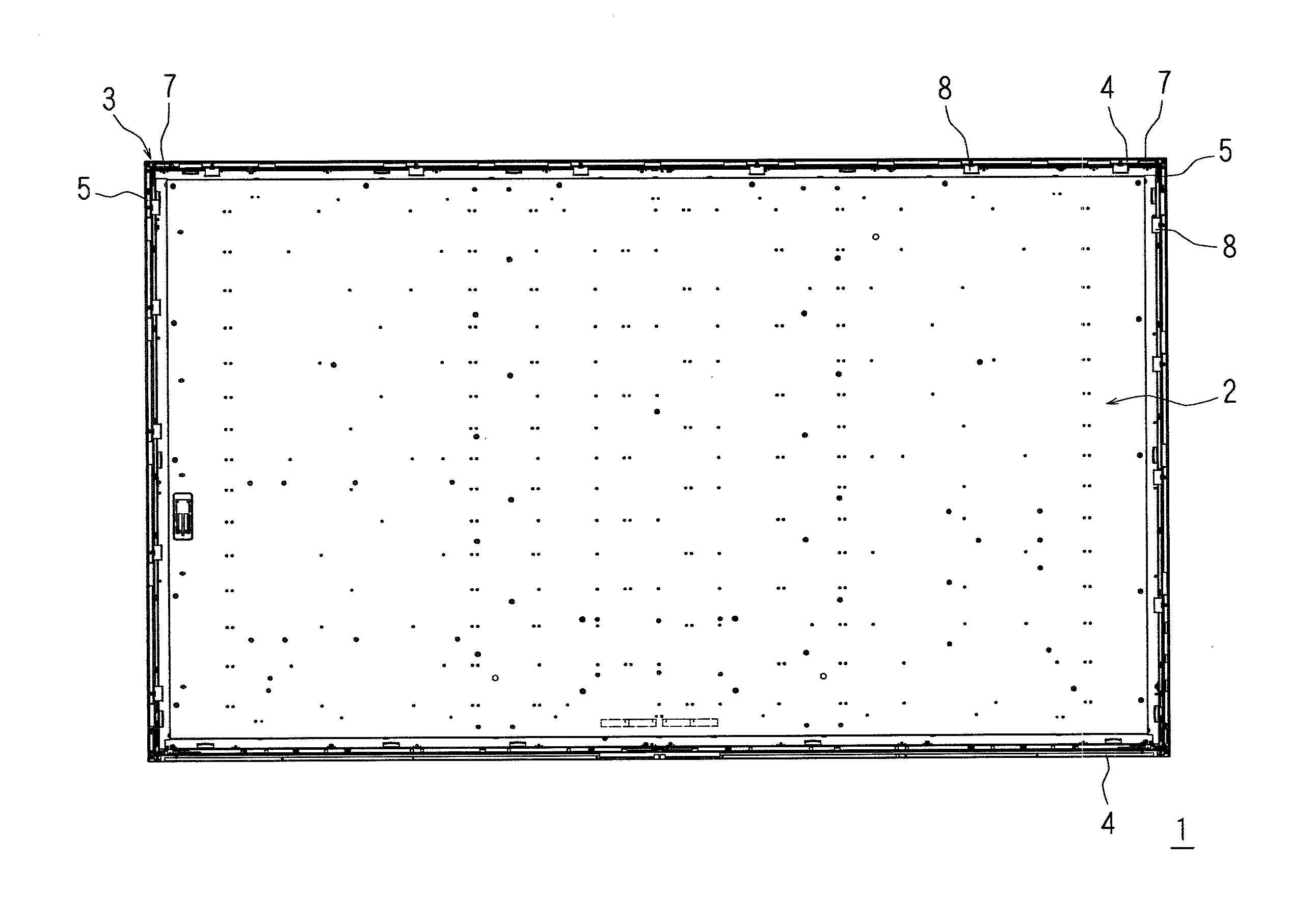

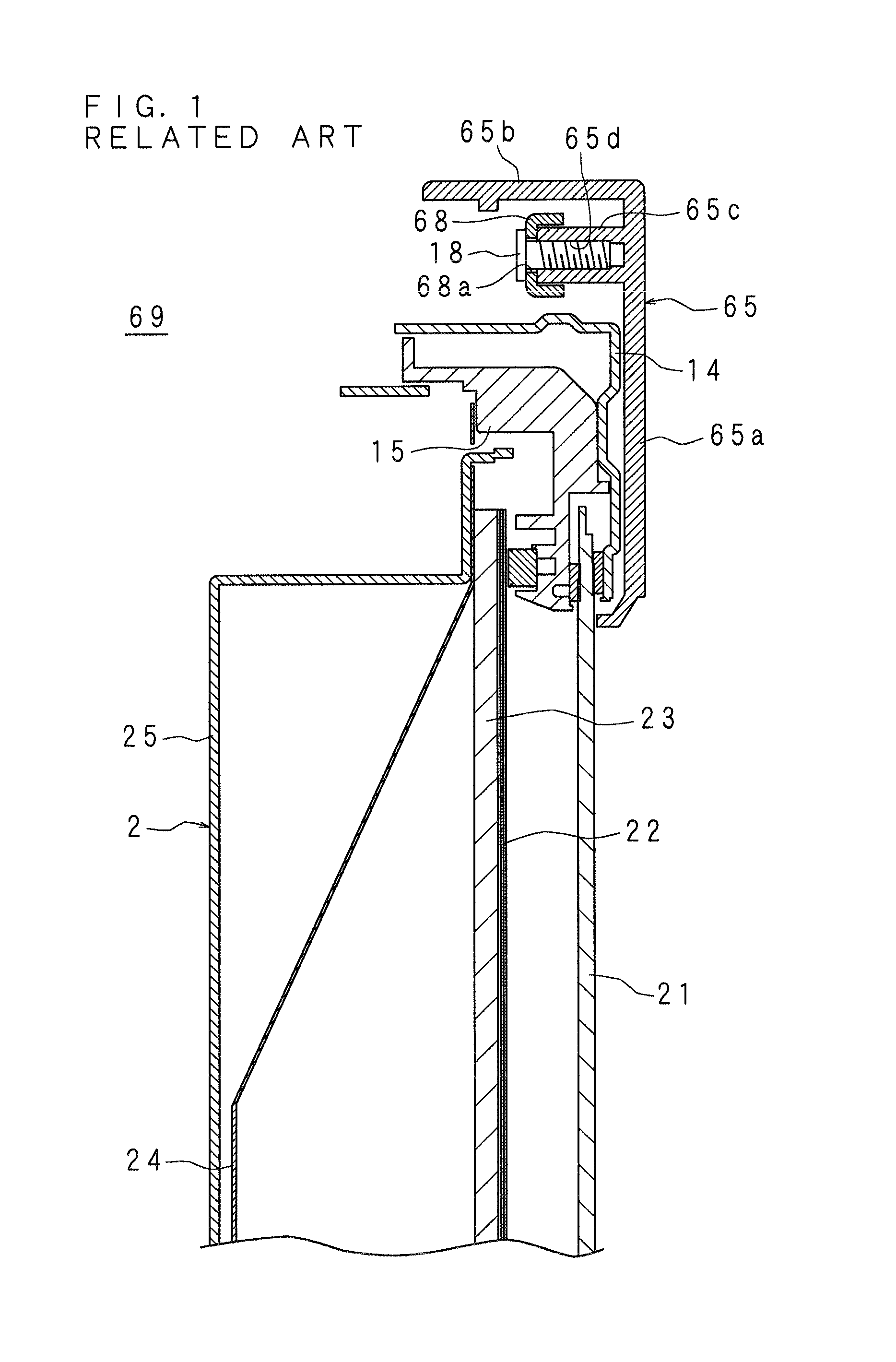

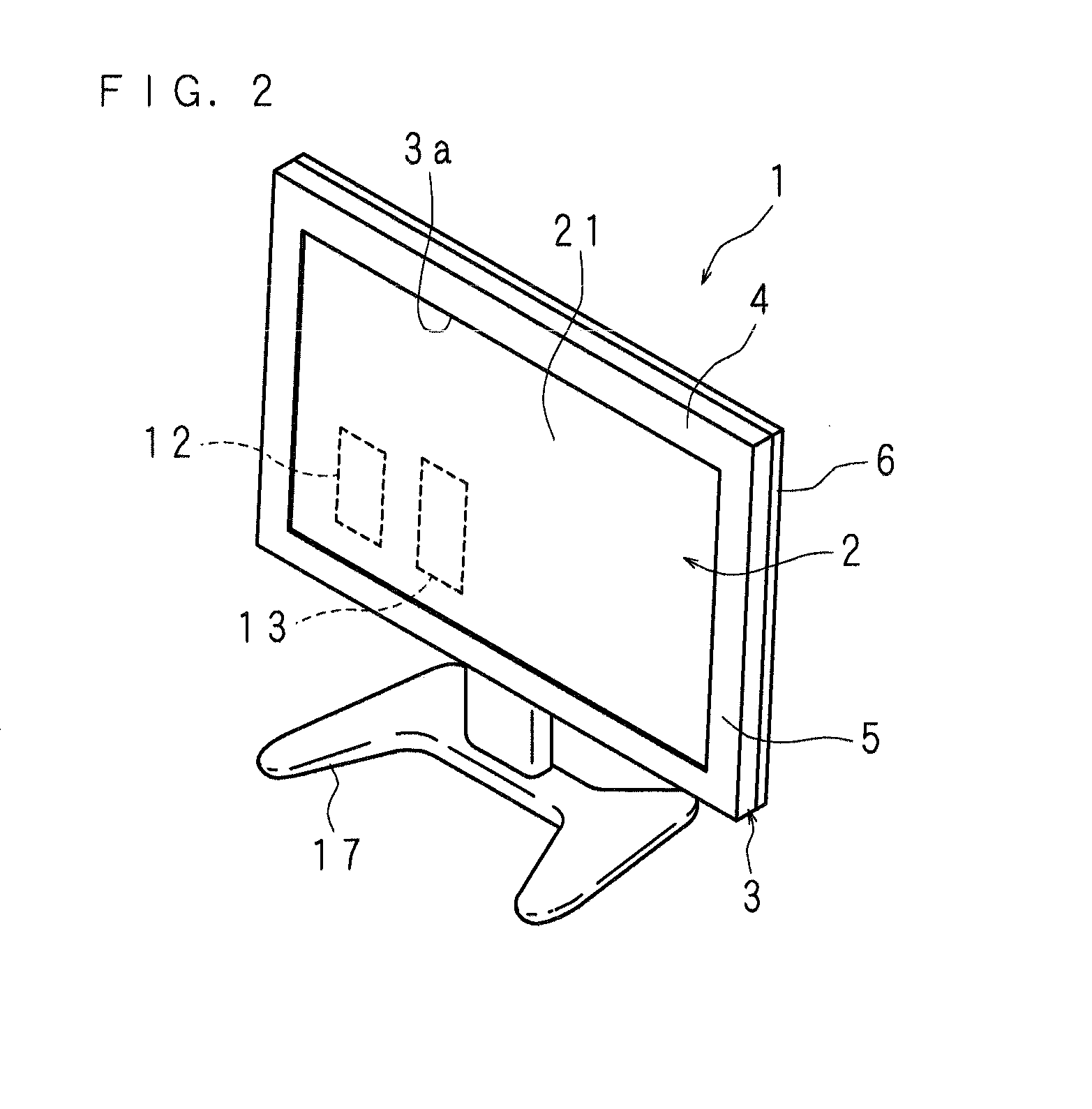

Display device and television receiver

InactiveUS20160165747A1Reduce replacement costsIncrease productivityTelevision system detailsColor television detailsProduction rateTelevision receivers

Provided are a display device capable of suppressing occurrence of defective products due to fastening defect of screws, having excellent productivity and workability, achieving narrowing of frame and thinning of set thickness with excellent appearance quality, and manufacturing at a low cost, as well as a television receiver including the display device. A TV receiver includes a display module, and horizontal frames which cover long side peripheral end part of a front surface of the display module. A first plate part and a second plate part forming each side of L-shaped connectors are provided with a plurality of female screws. The horizontal frame includes an end edge covering part which covers long side end edge part of the display module, and a side covering part which covers a side part thereof, and a protruding part which protrudes inwardly of the side covering part. The protruding part is provided with a plurality of screw insertion holes. With the connector aligned to end portions of the horizontal frame and the vertical frame, screws are inserted into the screw insertion holes, and screwed to the female screws of the first plate part, and thereby the horizontal frame and the vertical frame are connected to each other.

Owner:SHARP KK

Method for producing piston for internal-combustion engine

ActiveUS20090071001A1Speed up the flowReadily and well-formedValve arrangementsPlungersPiston ringEngineering

A method is provided for producing a piston for an internal-combustion engine of the structure in which a piston body which is composed of a crown having a groove for fitting a piston ring into an outer circumference surface and a skirt in connection with the bottom of the crown is provided with an annular cavity for flowing cooling liquid on an inside of the groove, the method comprising the steps of: forming the crown and the skirt individually; forming an annular groove for the annular cavity in the inner bottom of the crown and an annular rib in connection with the open edge of the annular groove before the crown and the skirt are joined together; bending the rib toward the opening of the annular groove by application of pressure to close the opening of the annular groove to thereby form the annular cavity; and joining the crown and the skirt together.

Owner:RIKEN FORGE +1

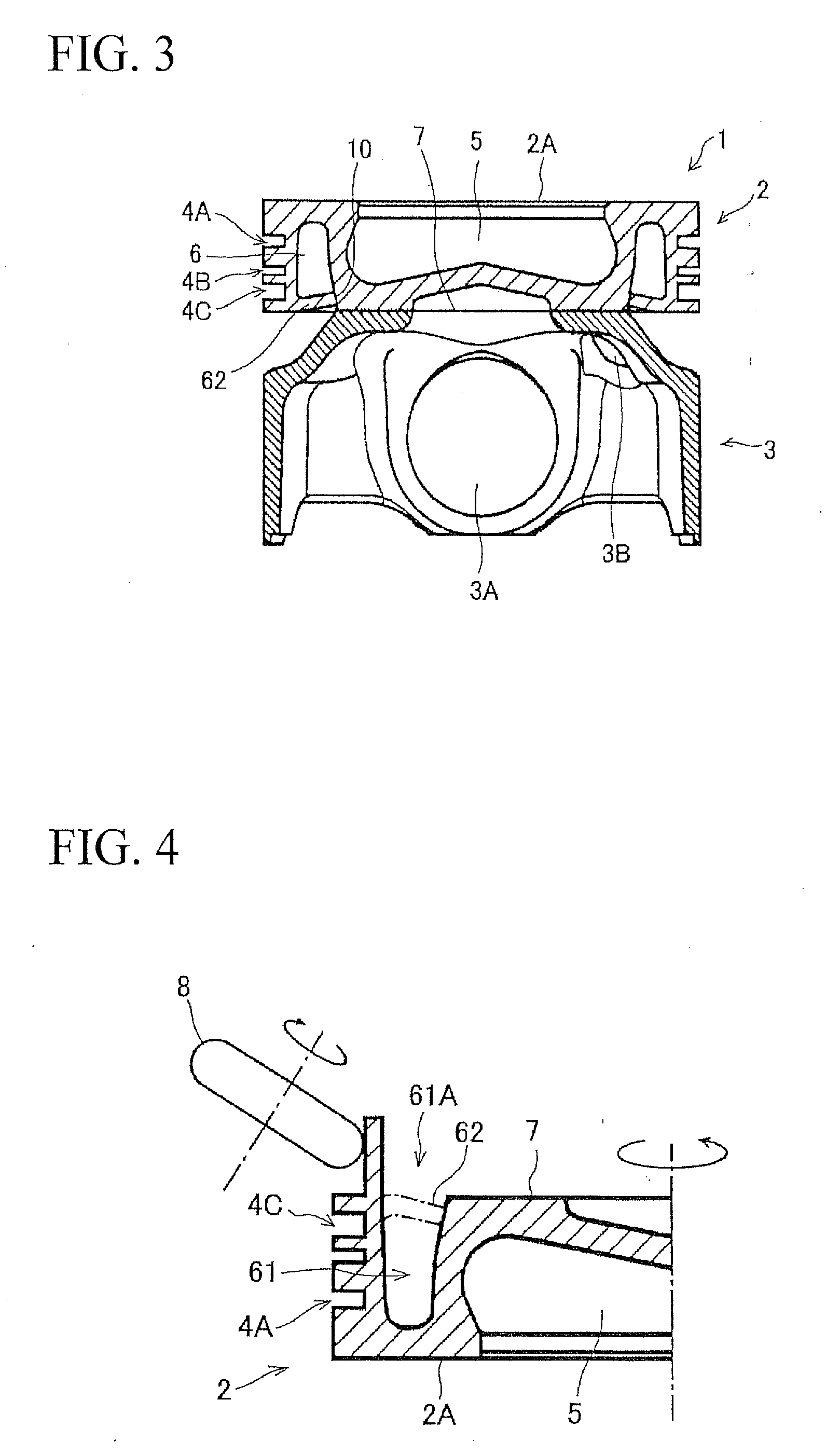

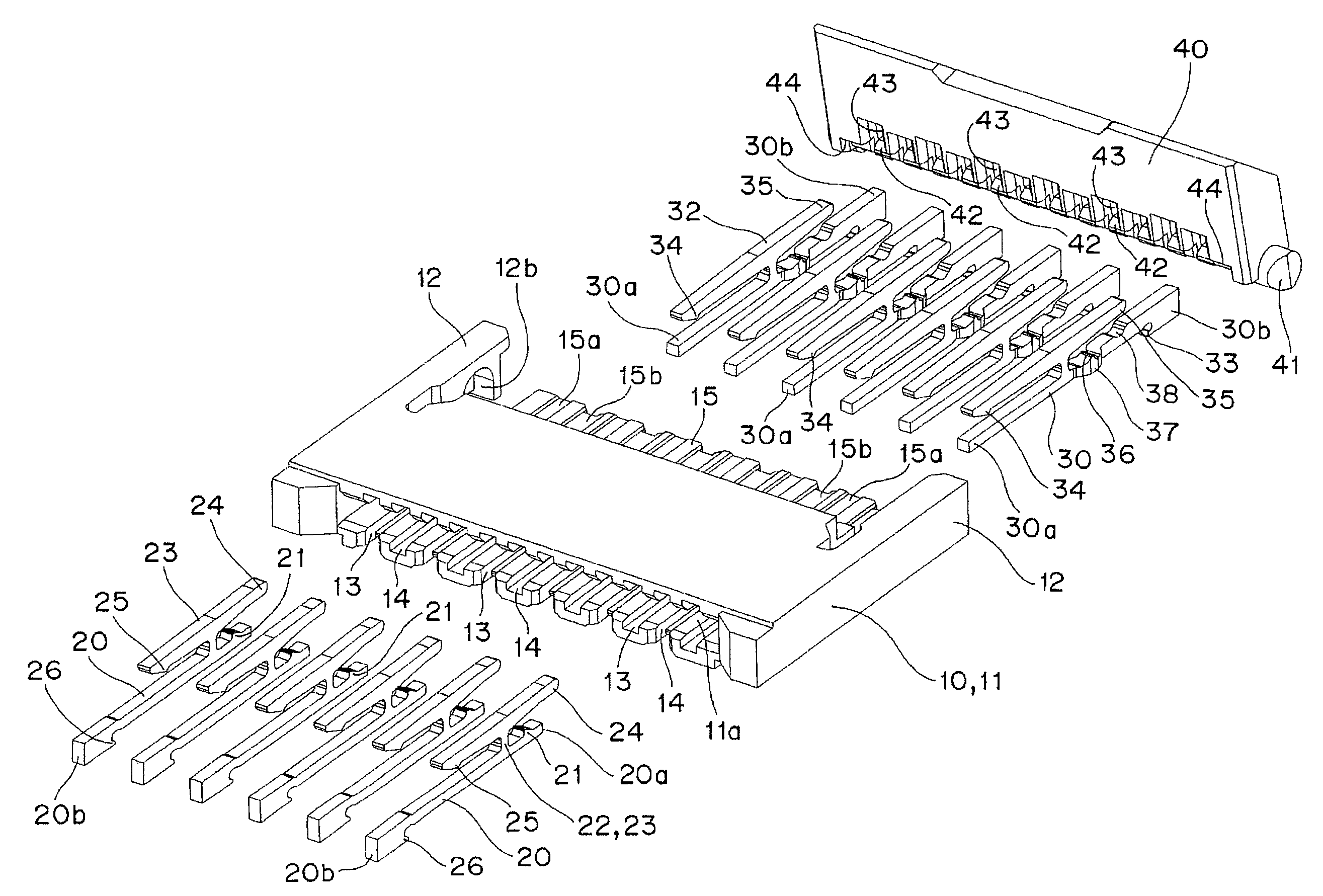

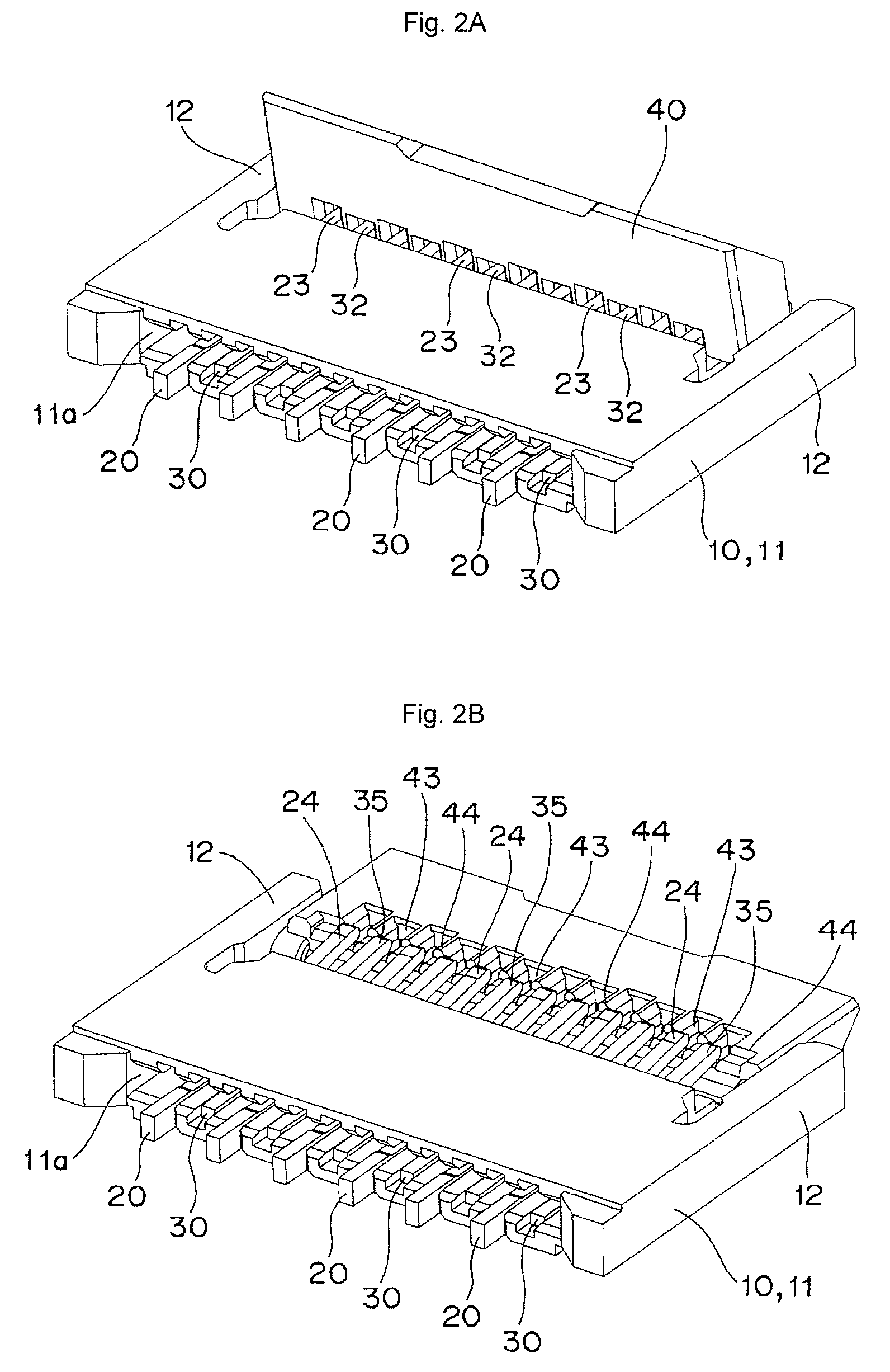

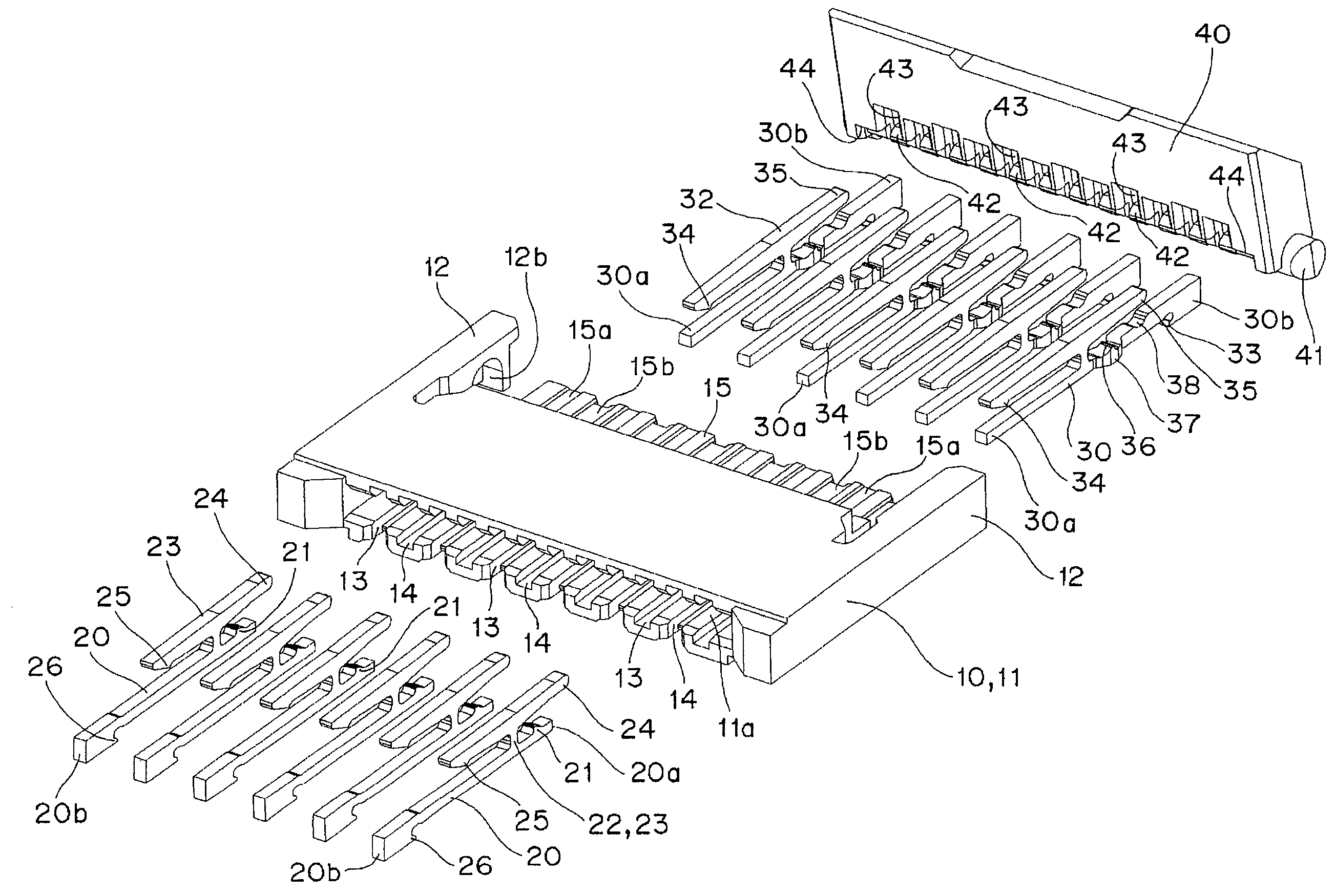

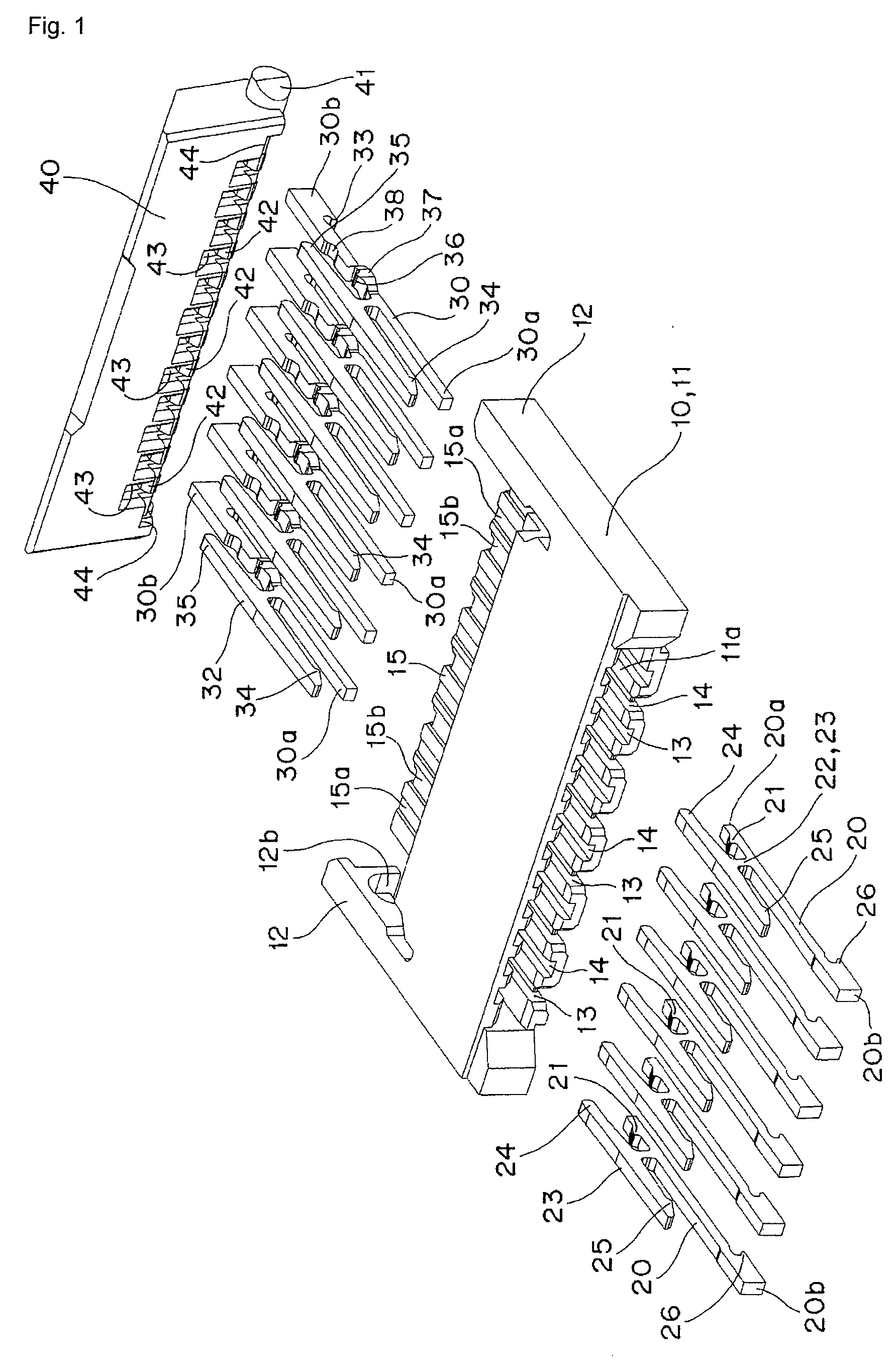

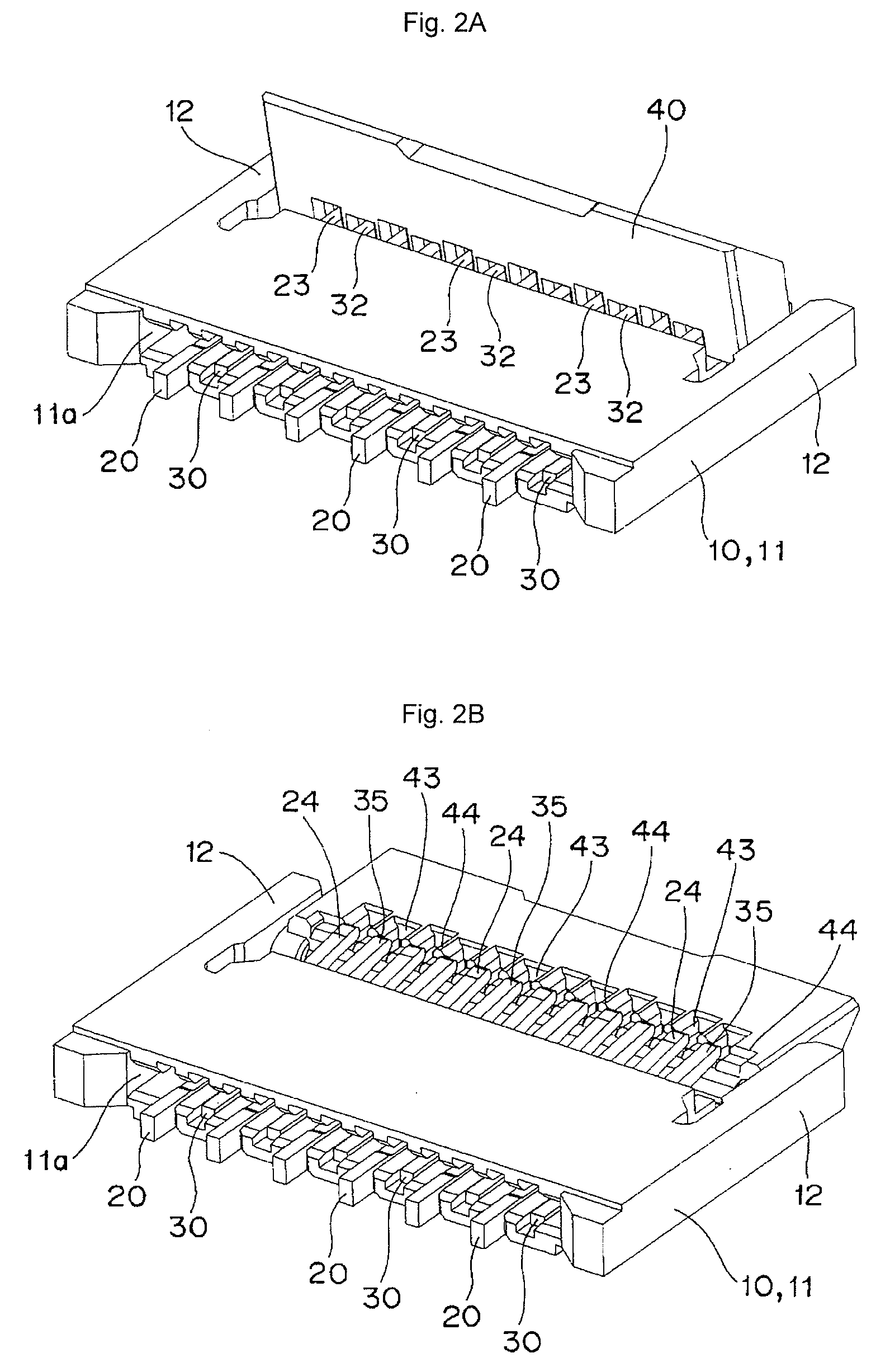

Connector connection terminals

InactiveUS7632136B2Uniform cross-sectional shapeLess likely to buckleCoupling device detailsFixed connectionsMechanical engineering

A connector connection terminal that is less likely to buckle and in which cutting task is facilitated is provided. The present invention provides a connector connection terminal in which substantial height dimension from a rotation recess to an end face at an end on a rear surface side is set larger than a substantial height dimension from the rotation recess to an end face at an end on the front surface side, and an upper surface from the rotation recess to the end face at the end on the rear surface side is a flat surface.

Owner:DAIICHI SEIKO CO LTD

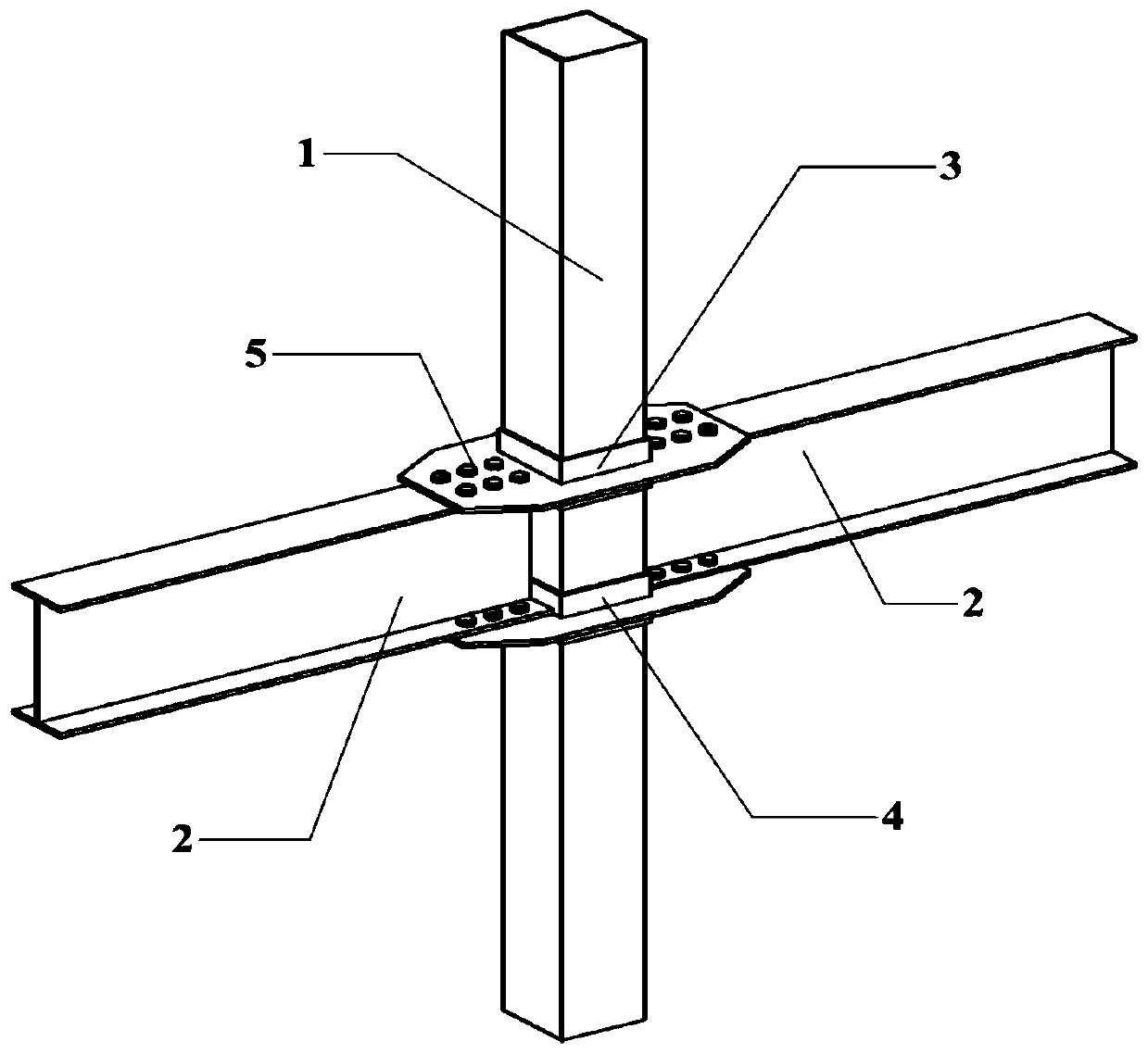

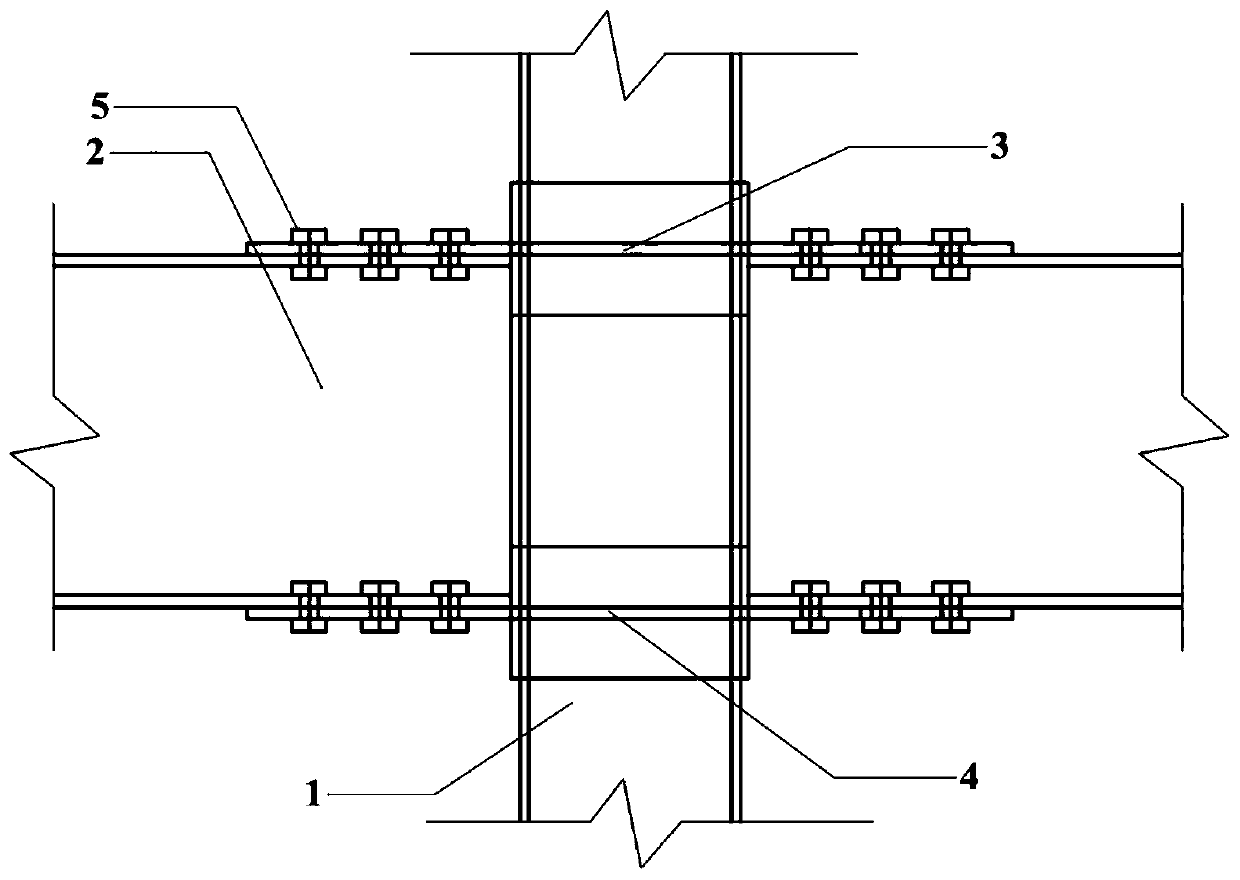

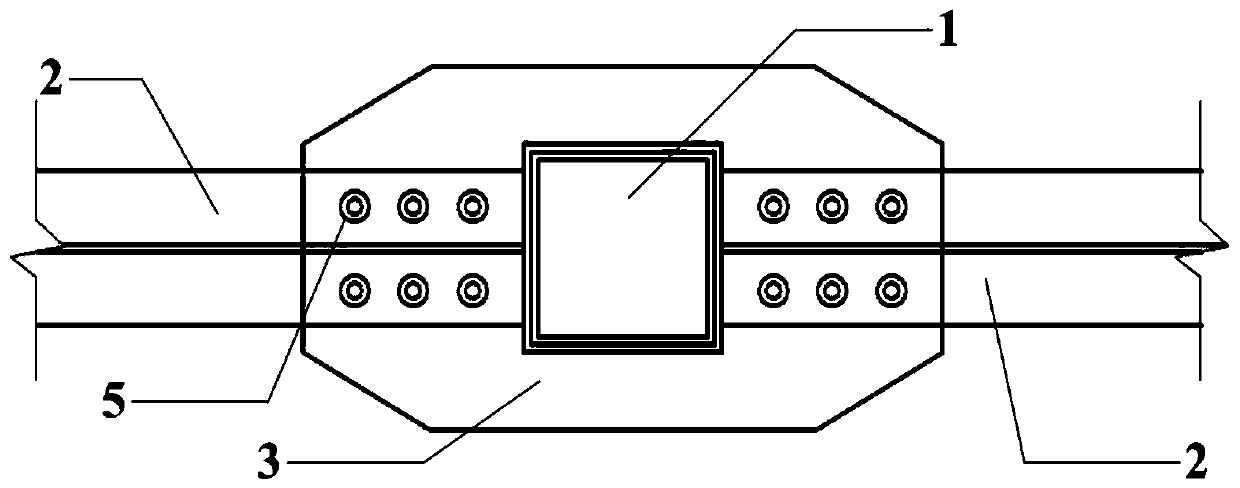

Square steel tube concrete column-steel beam outer ring sleeve plate bolt connection joint

InactiveCN111456235AIncrease the direct contact areaImprove distributionBuilding constructionsBoard structureSteel tube

The invention discloses a square steel tube concrete column-steel beam outer ring sleeve plate bolt connection joint. The square steel tube concrete column-steel beam outer ring sleeve plate bolt connection joint comprises a square steel tube, the square steel tube is sleeved with an upper outer ring sleeve plate and a lower outer ring sleeve plate, the upper outer ring sleeve plate comprises an upper short sleeve, an inner surface of the upper short sleeve is connected with the square steel tube, an outer surface of the upper short sleeve is connected with an upper outer ring plate, the lowerouter ring sleeve plate and the upper outer ring sleeve plate are of the same structure, the lower outer ring sleeve plate comprises a lower short sleeve and a lower outer ring plate, and a steel beam is connected between the upper outer ring sleeve plate and the lower outer ring sleeve plate. The distribution of a column wall yield line is expanded, the column wall rigidity of a joint domain isimproved, and the contribution of an outer ring plate to the joint bearing capacity under the action of external load is increased; the defect that the rigidity at the joint is insufficient due to thefact that an inner ring plate is not arranged is overcome; by adopting the method, the field operation amount is small, the steel structure construction efficiency is improved, the material utilization rate is increased, and good economic benefits and social benefits are achieved.

Owner:SHENYANG JIANZHU UNIVERSITY

Semiconductor structure and forming method thereof

ActiveCN104037159AUniform positionUniform cross-sectional shapeSemiconductor/solid-state device detailsNanoinformaticsSemiconductor structureCrystal orientation

Owner:PEKING UNIV

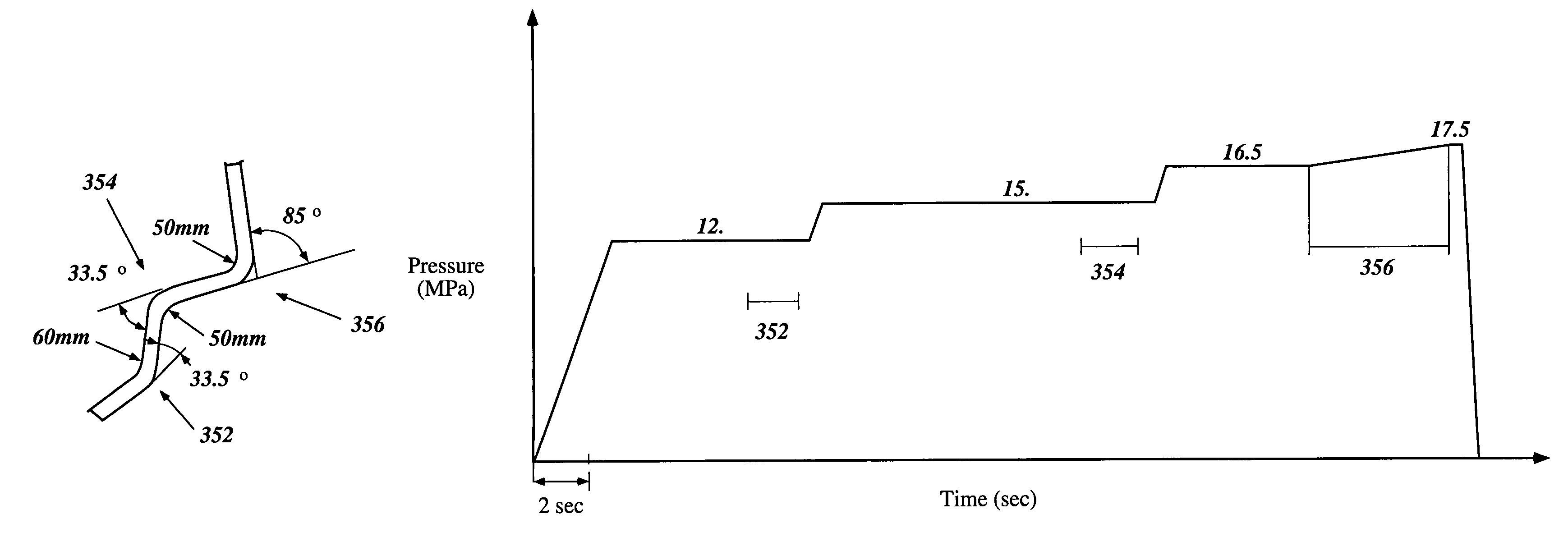

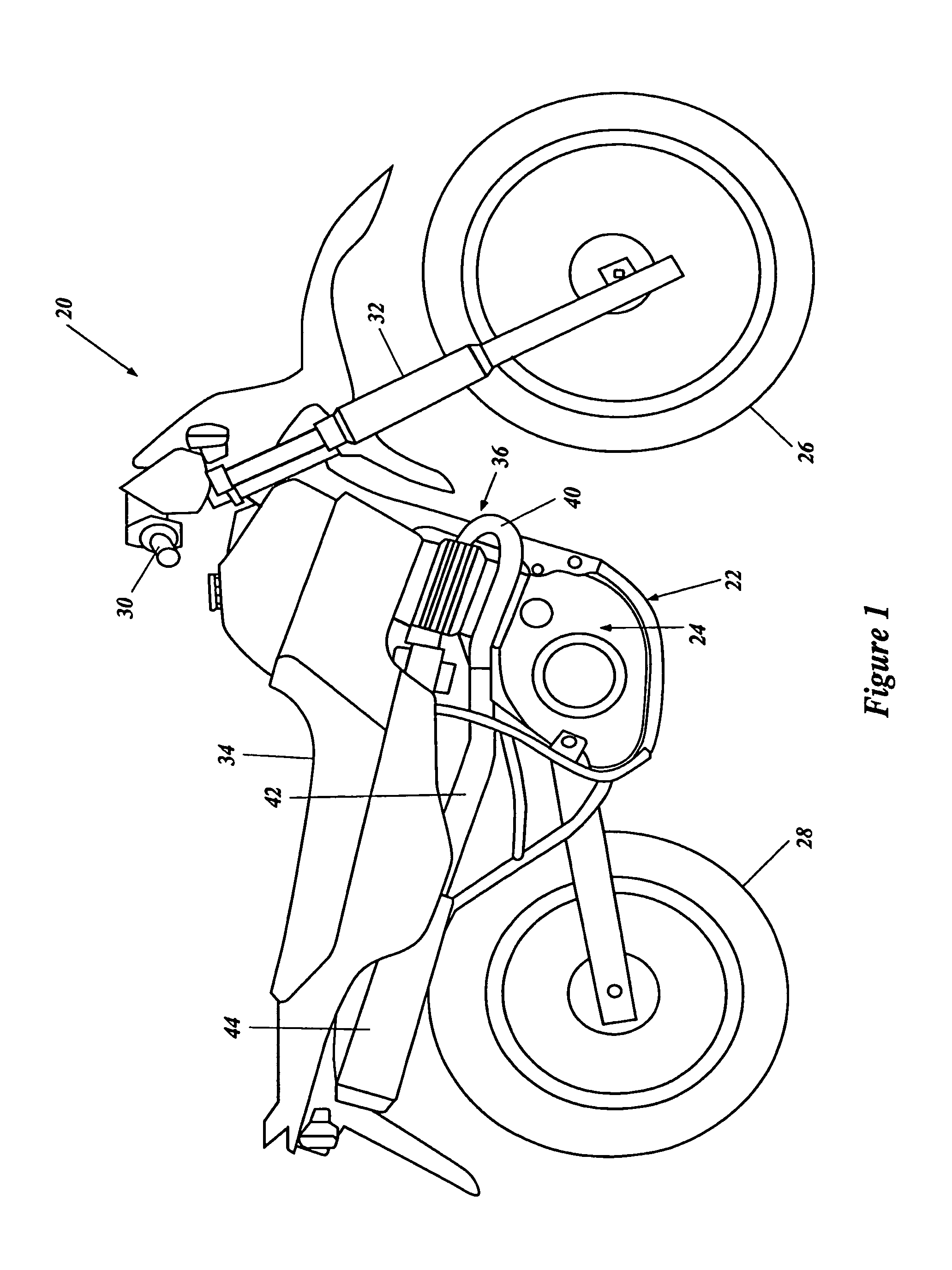

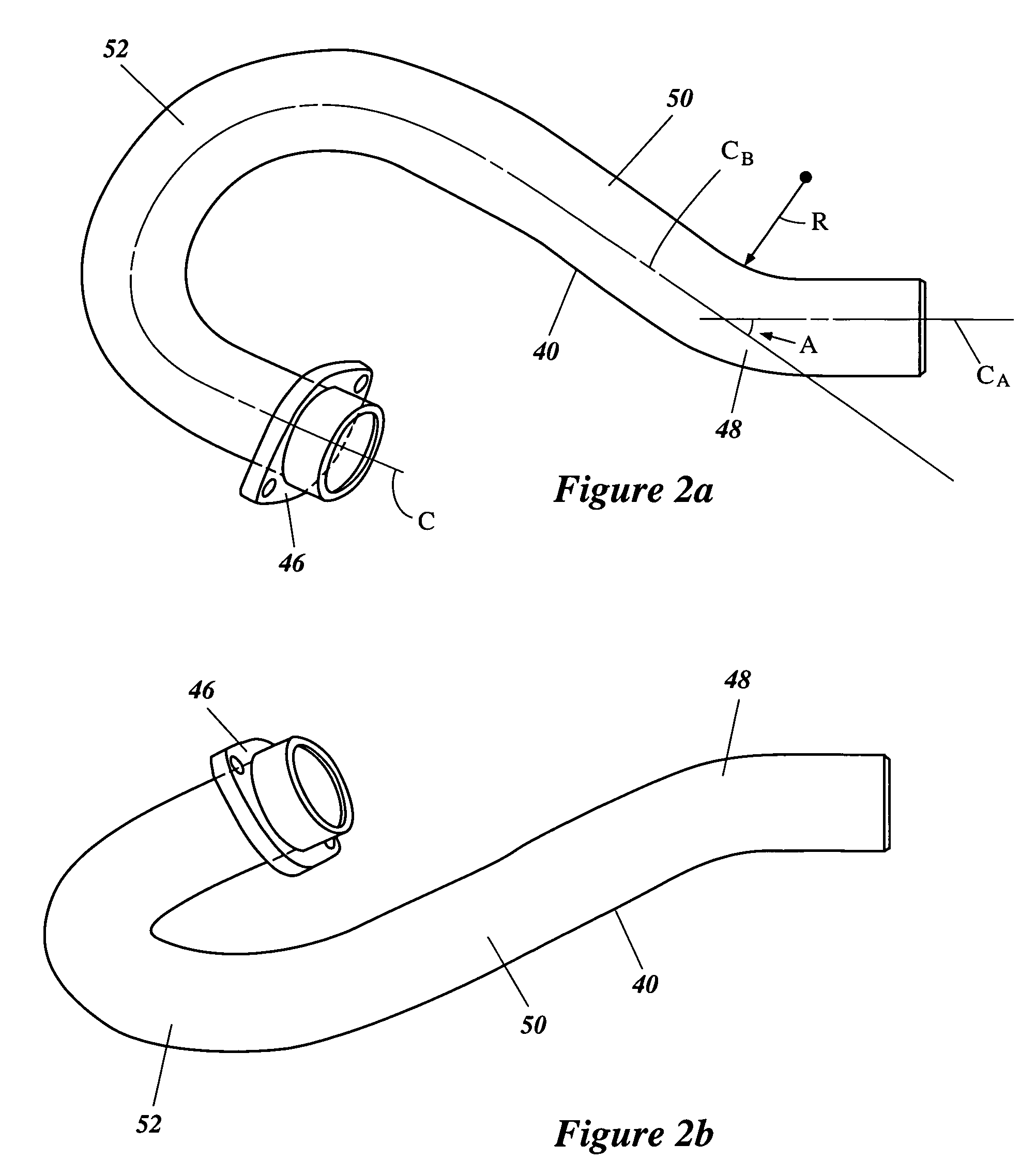

Pipe bending apparatus and method

A pipe bending apparatus for performing a pipe bending method, wherein the method includes filling a workpiece with a liquid, pressurizing the liquid to a target pressure level, and bending the workpiece to create a bent pipe. Preferably, the pressure level is inversely proportional to the radius of the bend in the pipe. Furthermore, preferably the pressure is directly proportional to the bending angle of the pipe. Preferably, the pressure is maintained substantially at the target pressure during the bending process. Optionally, the pressure level can be increased during the bending process.

Owner:YAMAHA MOTOR CO LTD

Connector connection terminals

InactiveUS20090170352A1Help positioningImprove assembly accuracyCoupling device detailsFixed connectionsEngineeringMechanical engineering

A connector connection terminal that is less likely to buckle and in which cutting task is facilitated is provided. The present invention provides a connector connection terminal in which substantial height dimension from a rotation recess to an end face at an end on a rear surface side is set larger than a substantial height dimension from the rotation recess to an end face at an end on the front surface side, and an upper surface from the rotation recess to the end face at the end on the rear surface side is a flat surface.

Owner:DAIICHI SEIKO CO LTD

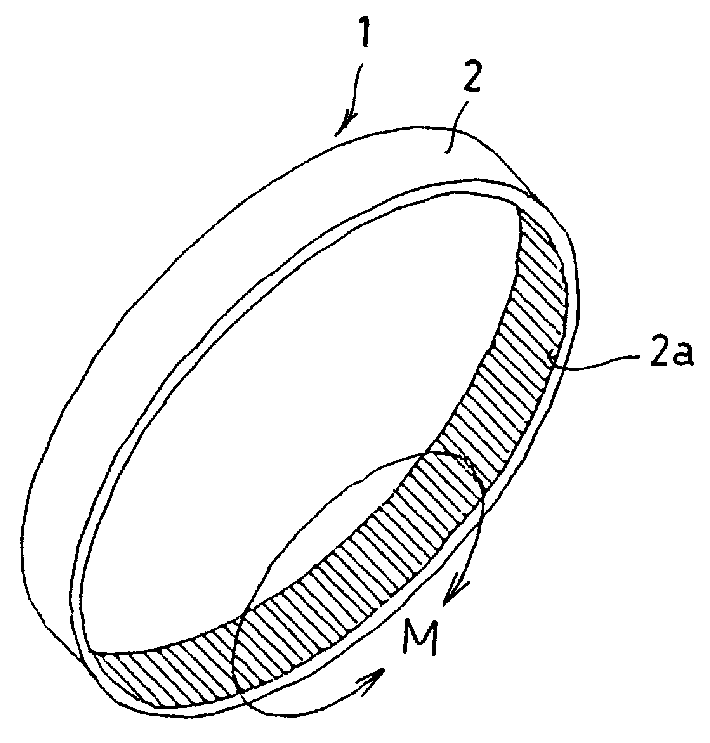

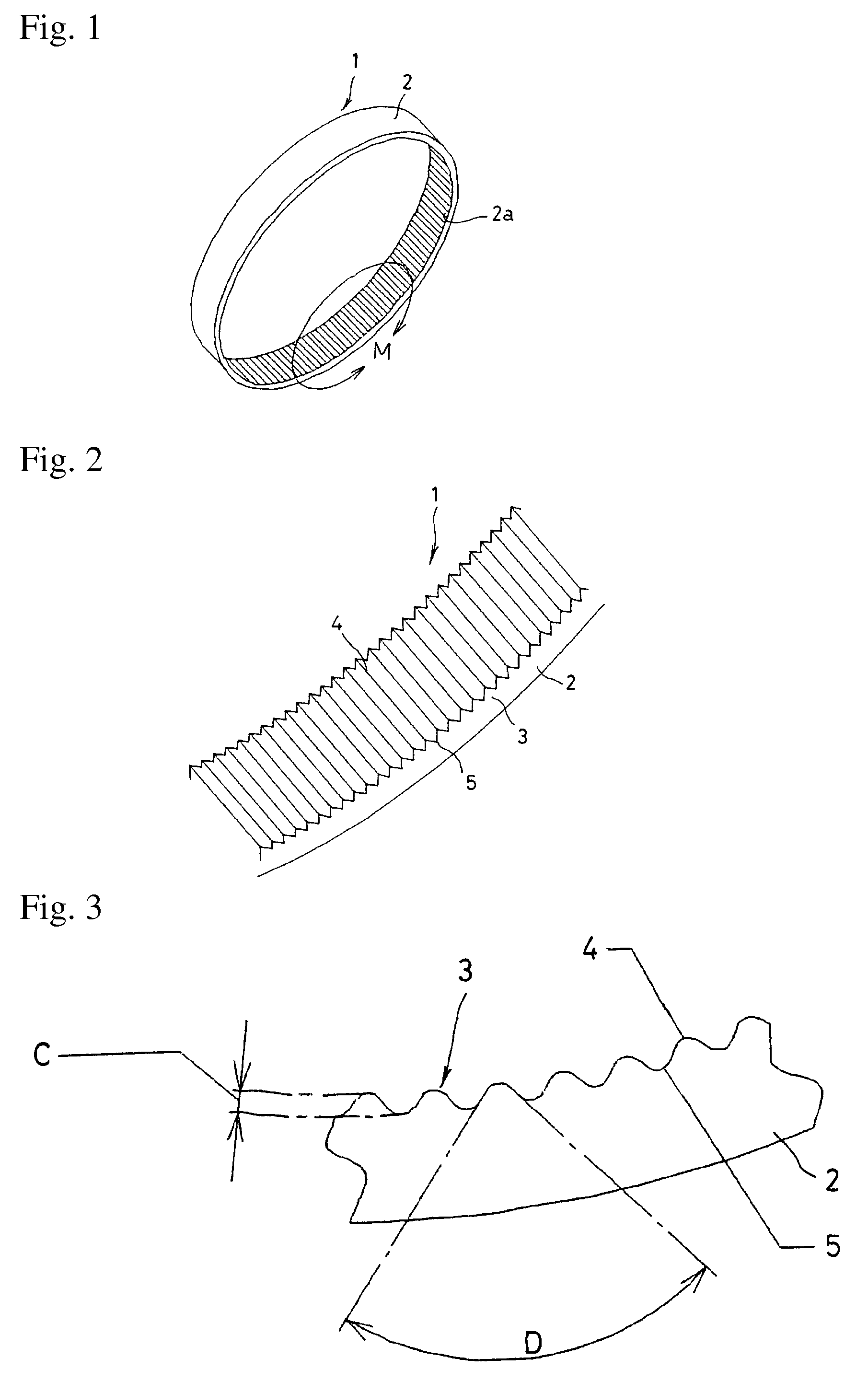

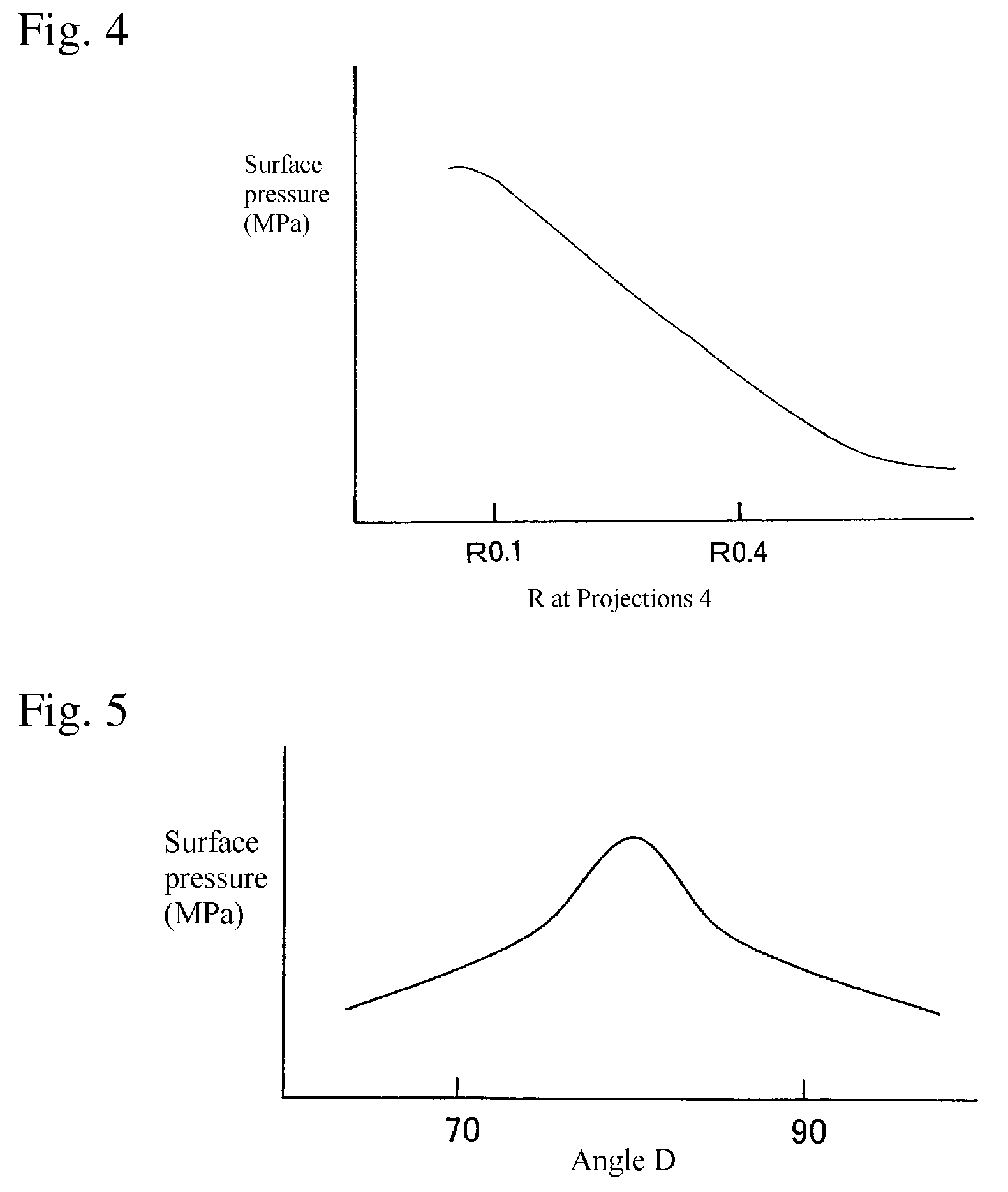

Endless boot fixing band and manufacturing method thereof

InactiveUS7657975B2Reduce tightening forceLittle strengthYielding couplingFlexible elementsStructural engineeringMechanical engineering

Owner:NHK SPRING CO LTD

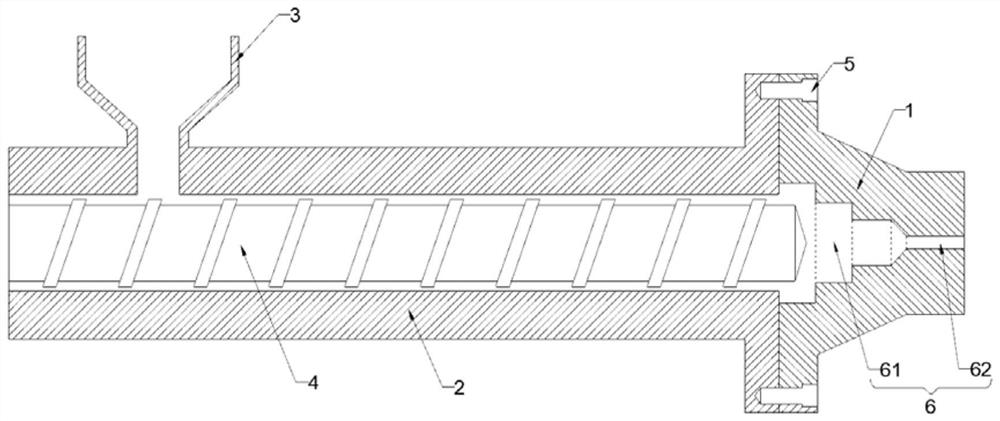

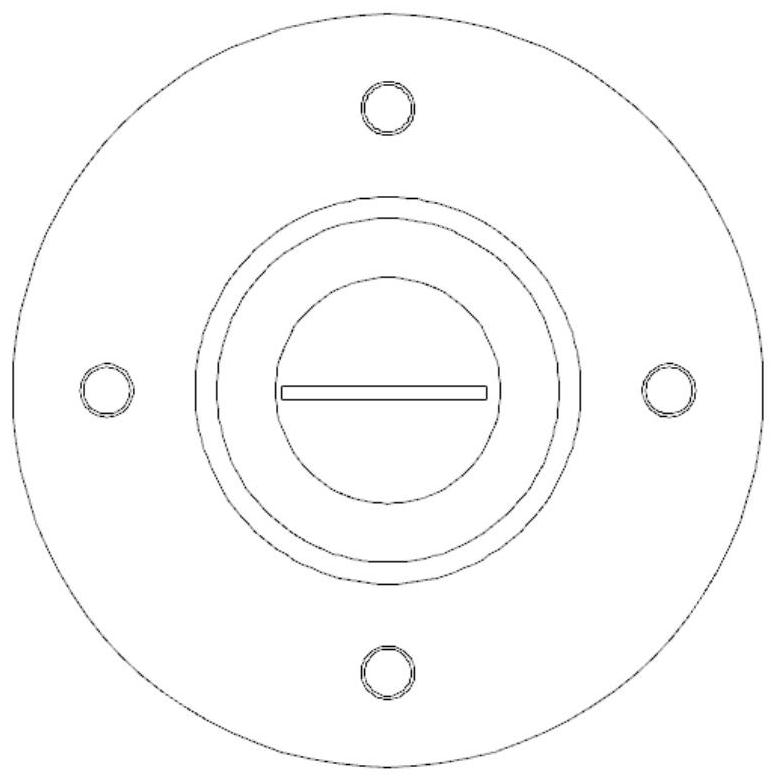

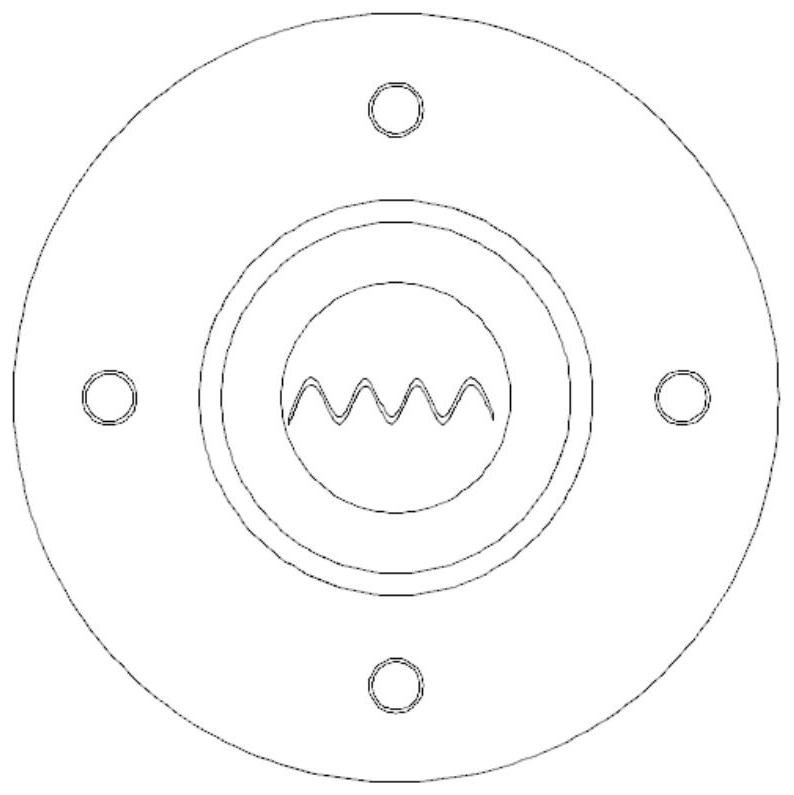

Extrusion head for pole piece forming, forming device comprising extrusion head and forming method and preparation method of extrusion head

PendingCN112072063AImprove thickness uniformityReduce powder shedding rateElectrode moldingButt jointEngineering

The invention provides an extrusion head for pole piece forming, a forming device comprising the extrusion head, a forming method of the extrusion head and a preparation method of the extrusion head.The extrusion head comprises an extrusion head shell, and a through extrusion channel is formed in the extrusion head shell in the extrusion direction; the extrusion channel is divided into a transition cavity and a forming cavity which are sequentially communicated in a butt joint mode in the extrusion direction, and the diameter of the annular face of the inner wall of the transition cavity is gradually reduced in the extrusion direction. And the mixed pole piece mixture is extruded into a pole piece with a certain thickness by adopting a screw rod, and the pole piece is dried, and then directly passes through a specific cutting die, so the manufacturing of different types of special pole pieces is finished. And compared with other pole piece preparation methods, the preparation efficiency is obviously improved.

Owner:EVE ENERGY CO LTD +1

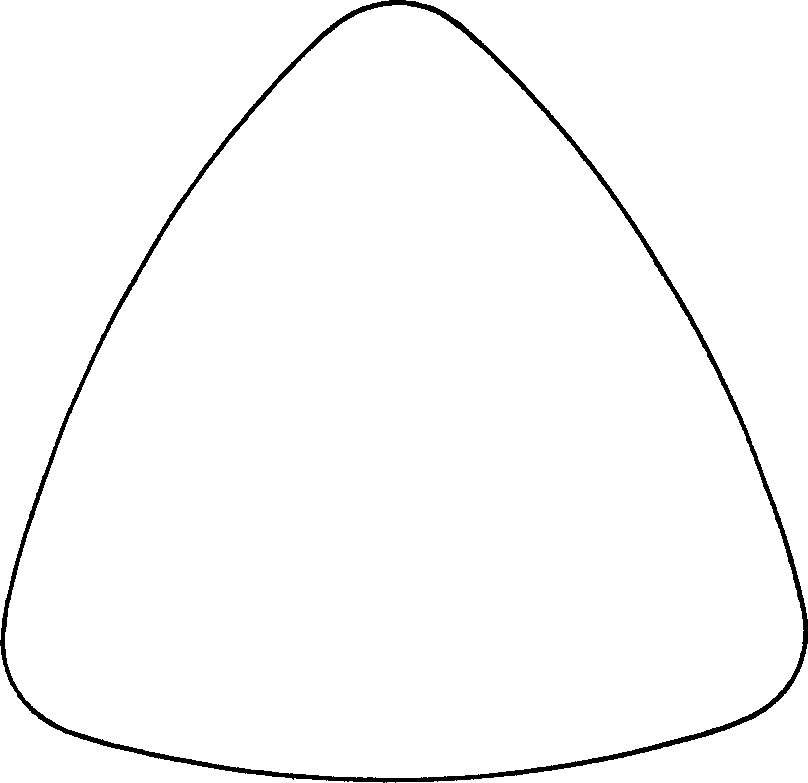

Poly (trimethylene terephthalate) modified cross-section yarn

InactiveCN1370246AUniform cross-sectional shapeUniform shapeFilament/thread formingThin material handlingYarnSpin welding

The present invention provides a special-shaped yarn excellent especially as clothing material, which is composed of more than 95 mole % of propylene glycol terephthalate repeating units and less than 5 mole % of other ester repeating units, and the intrinsic viscosity [η] is 0.7 ~ 1.3 (dl / g) polypropylene terephthalate, and has a three-lobed cross-section, the outer circumference of the three-lobed cross-section is composed of a convex curve, or a convex curve and a straight line to the outside of the cross-section Polytrimethylene terephthalate shaped yarn. In addition, according to the production method of the present invention, it is possible to suppress the adhesion of the polymer to the spinning orifice or the generation of dirt, and there are few burrs and broken yarns, and it is the first time that the above-mentioned special-shaped yarn can be stably produced industrially.

Owner:ASAHI KASEI KK

Poly (trimethylene terephthalate) modified cross-section yarn

InactiveCN1195910CUniform cross-sectional shapeUniform shapeFilament/thread formingThin material handlingYarnPolyethylene terephthalate

Owner:ASAHI KASEI KK

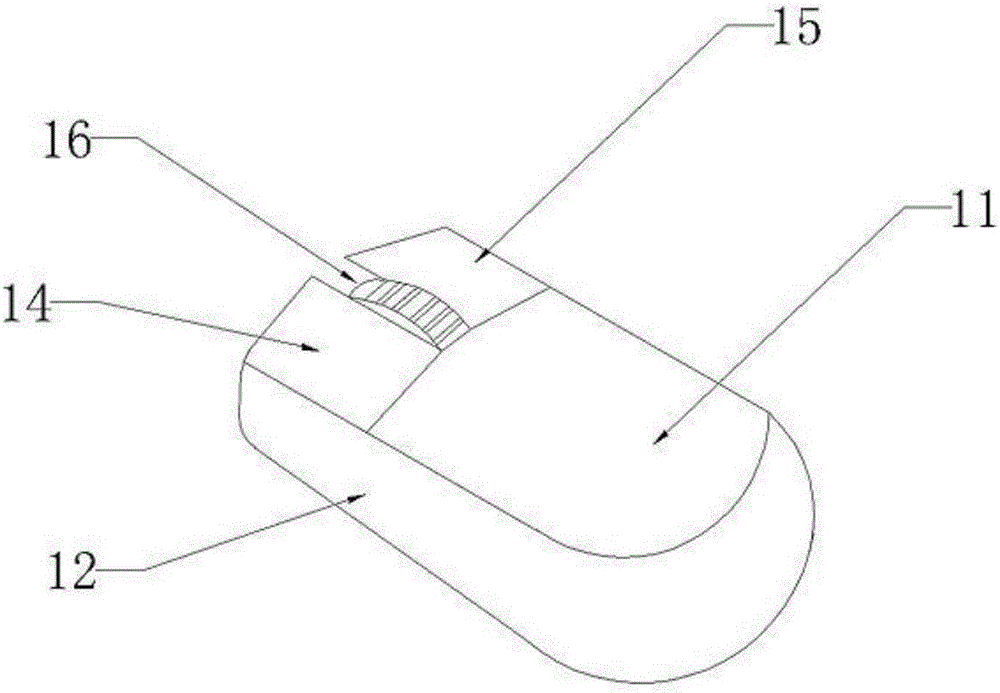

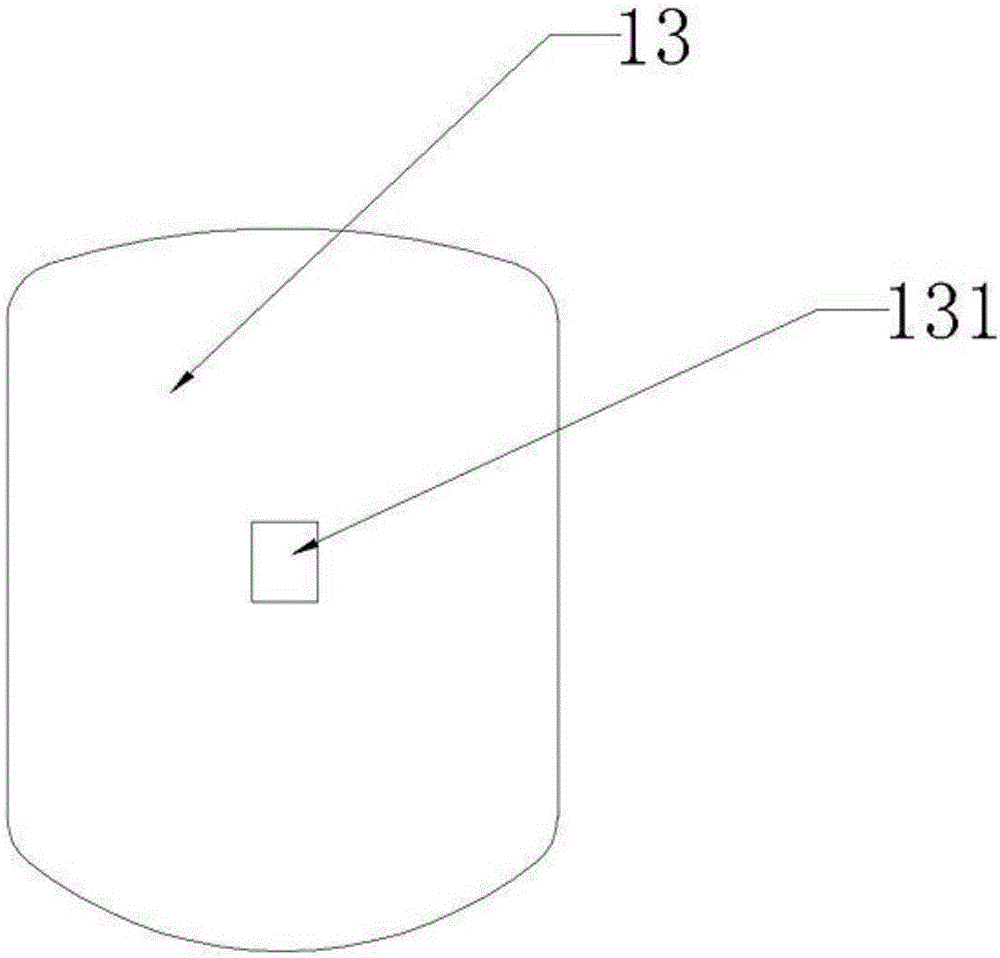

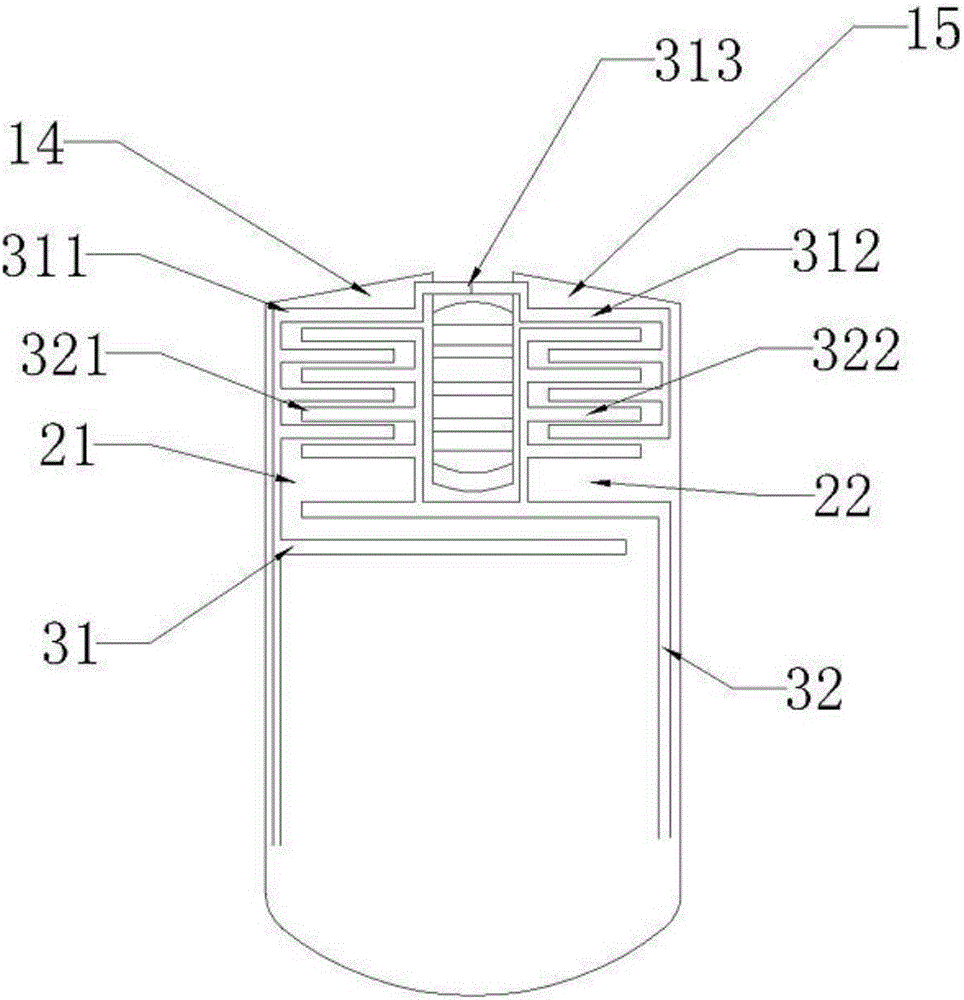

Self-charge mouse

ActiveCN106843542AImprove energy conversion efficiencyReduce usageBatteries circuit arrangementsElectric powerMechanical energyComputer module

The invention discloses a self-charge mouse which comprises a shell, an energy conversion module and an energy collection module. A left keyboard plate and a right keyboard plate are arranged on the shell, a roller is arranged between the left keyboard plate and the right keyboard plate, and mechanical energy can be converted into electric energy by the energy conversion module on the basis of piezoelectric effects and electromagnetic induction; the energy conversion module comprises a first energy conversion module, a second energy conversion module and a third energy conversion module; the twin-stage vibration of the left keyboard plate and the right keyboard plate can be converted into electric energy by the first energy conversion module on the basis of the piezoelectric effects; rolling of the roller can be converted into electric energy by the second energy conversion module on the basis of the piezoelectric effects; movement of the mouse can be converted into electric energy by the third energy conversion module on the basis of the electromagnetic induction; the energy collection module comprises a first energy collection module, a second energy collection module and a third energy collection module and is used for collecting the electric energy generated by the energy conversion module.

Owner:江苏如心智能科技有限公司

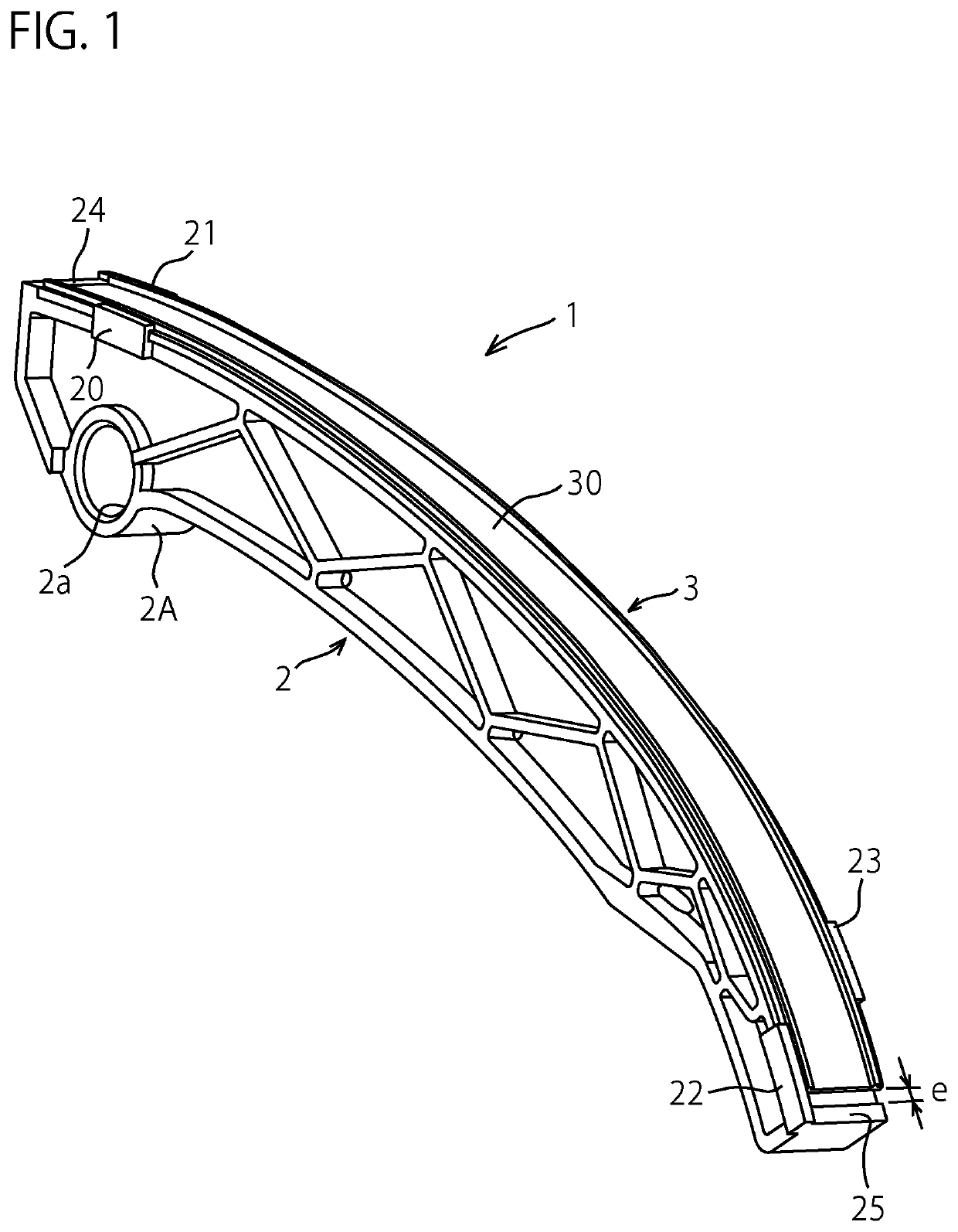

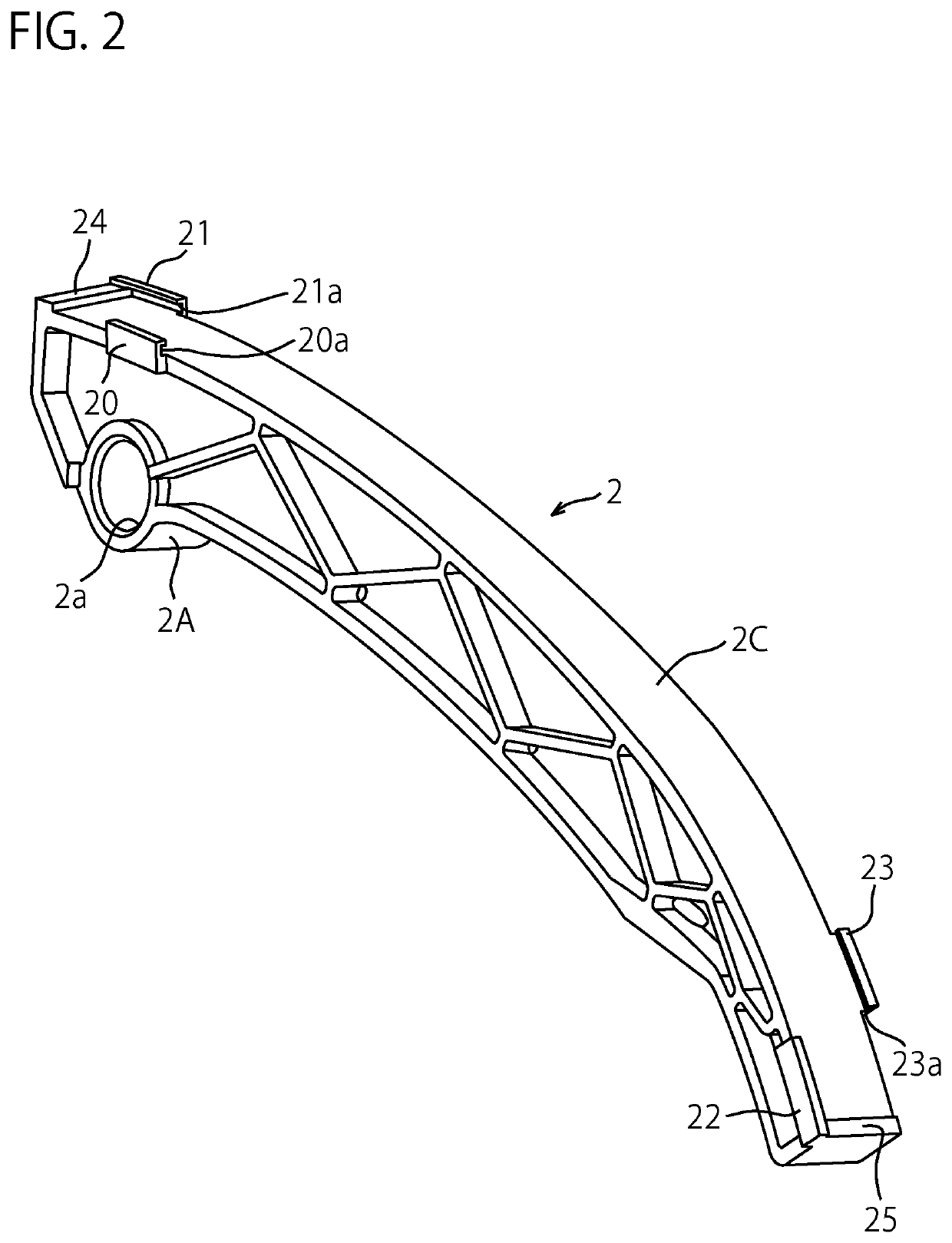

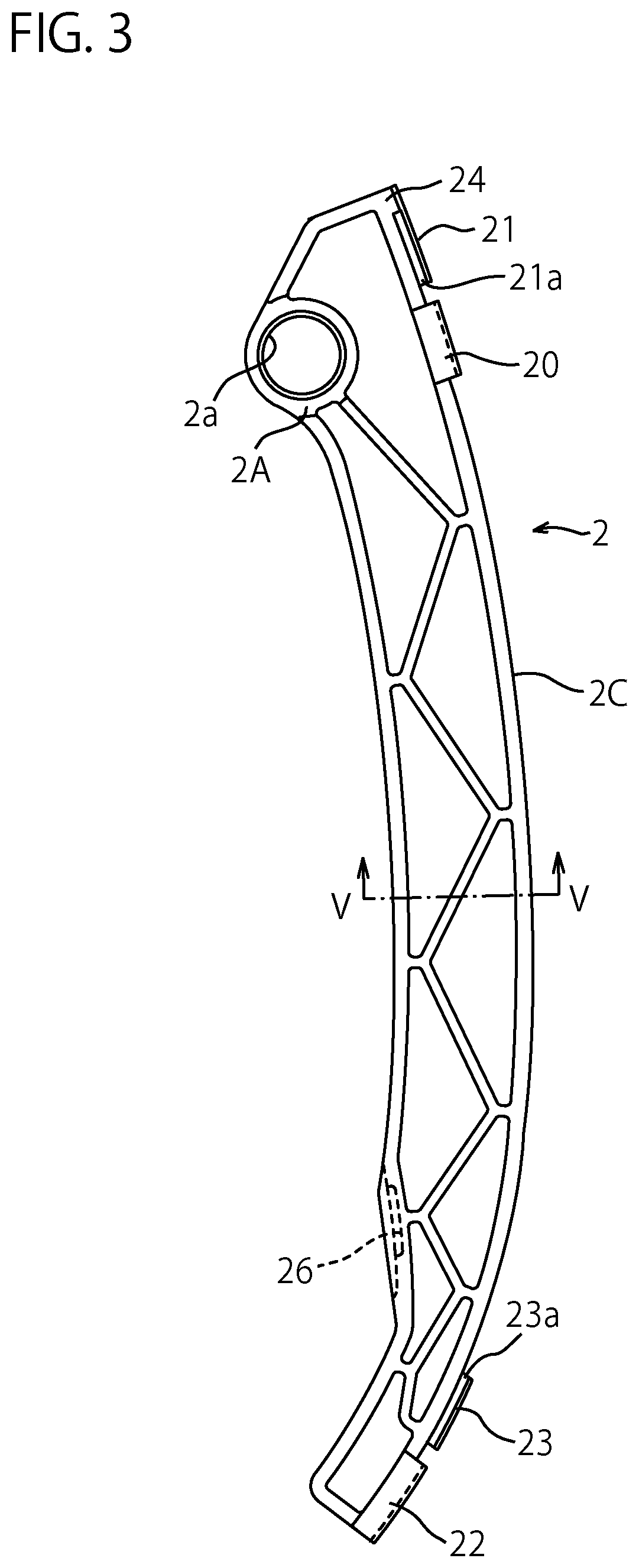

Shoe for chain guide and for chain tensioner arm, and chain guide and chain tensioner arm provided with said shoe

Owner:BORGWARNER INC

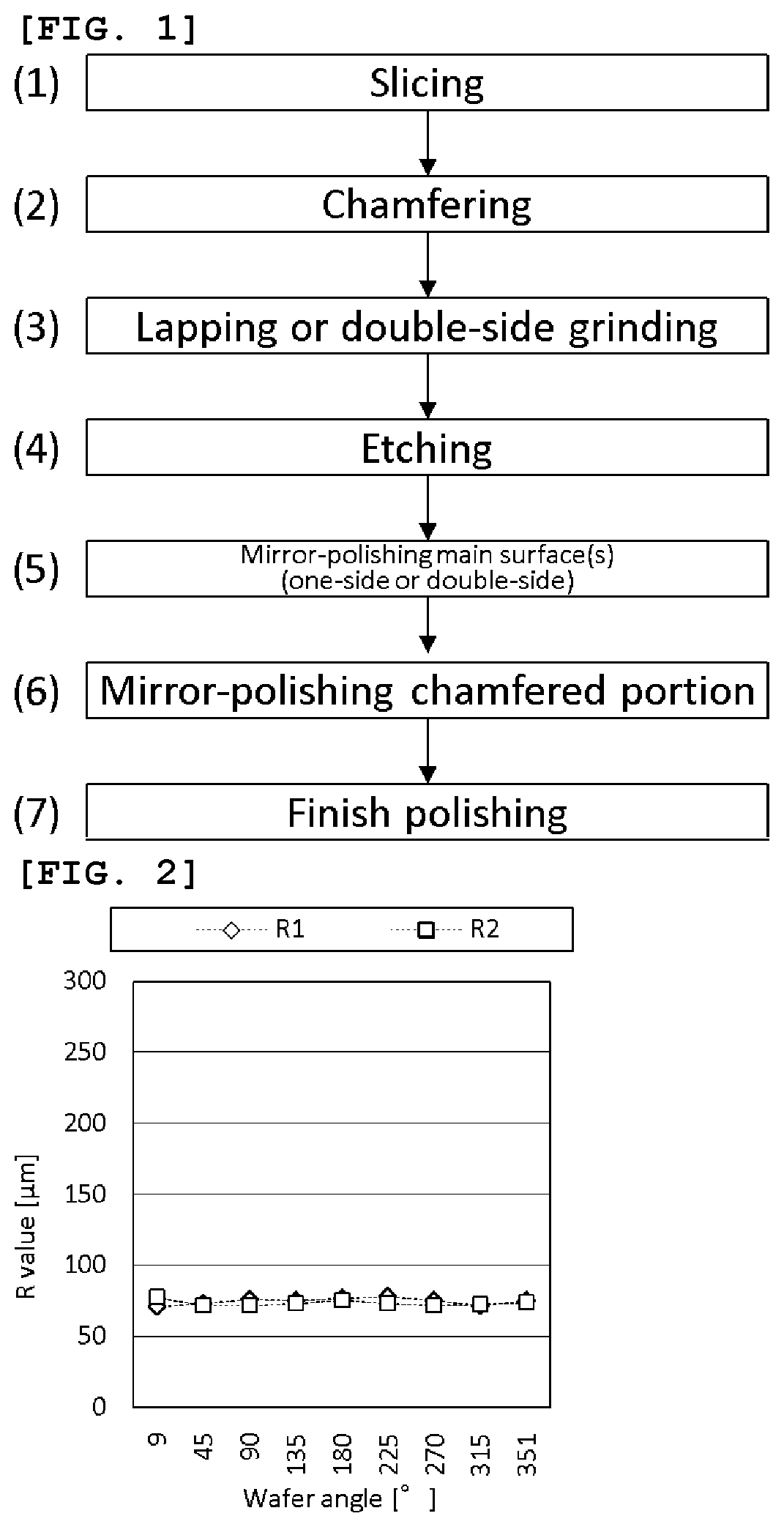

Method for manufacturing wafer

ActiveUS20200006047A1Uniform cross-sectional shapeEdge grinding machinesSemiconductor/solid-state device manufacturingWaferingMechanical engineering

A method for manufacturing a wafer product, including the steps of: chamfering a circumferential edge portion of a wafer; lapping or double-side grinding main surfaces thereof; etching; mirror-polishing the main surface; and mirror-polishing the chamfered portion. The chamfered portion has a cross-sectional shape including: a first inclined portion continuous from the first main surface; a first arc portion continuous from the first inclined portion and having a radius of curvature; a second inclined portion continuous from the second main surface; a second arc portion continuous from the second inclined portion and having a radius of curvature; and an end portion connecting the first arc portion to the second arc portion. This provides a method for manufacturing a wafer by which a variation in a chamfered cross-sectional shape in a circumferential direction caused by etching can be suppressed.

Owner:SHIN-ETSU HANDOTAI CO LTD

Capacitive sensor

ActiveCN101432627BHigh sensitivityAvoid defectsAcceleration measurementCapacitanceCapacitive sensing

Owner:PANASONIC CORP