Method for preparing plurality of layers of superfine silicon lines

An ultra-fine silicon and line technology, which is applied in semiconductor/solid-state device manufacturing, nanotechnology for information processing, semiconductor devices, etc., can solve the problems of complex process and long production cycle, and achieve a large process window and process cost. Small, uniform cross-sectional topography

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0063] A two-layer nanowire structure with a diameter of about 5 nm can be achieved according to the following steps:

[0064] 1) ALD on (100) bulk silicon substrate SiO 2 as a sacrificial layer;

[0065] 2) ALD Si 3 N 4 as a corrosion mask;

[0066] 3) ALD SiO 2 as a sacrificial layer;

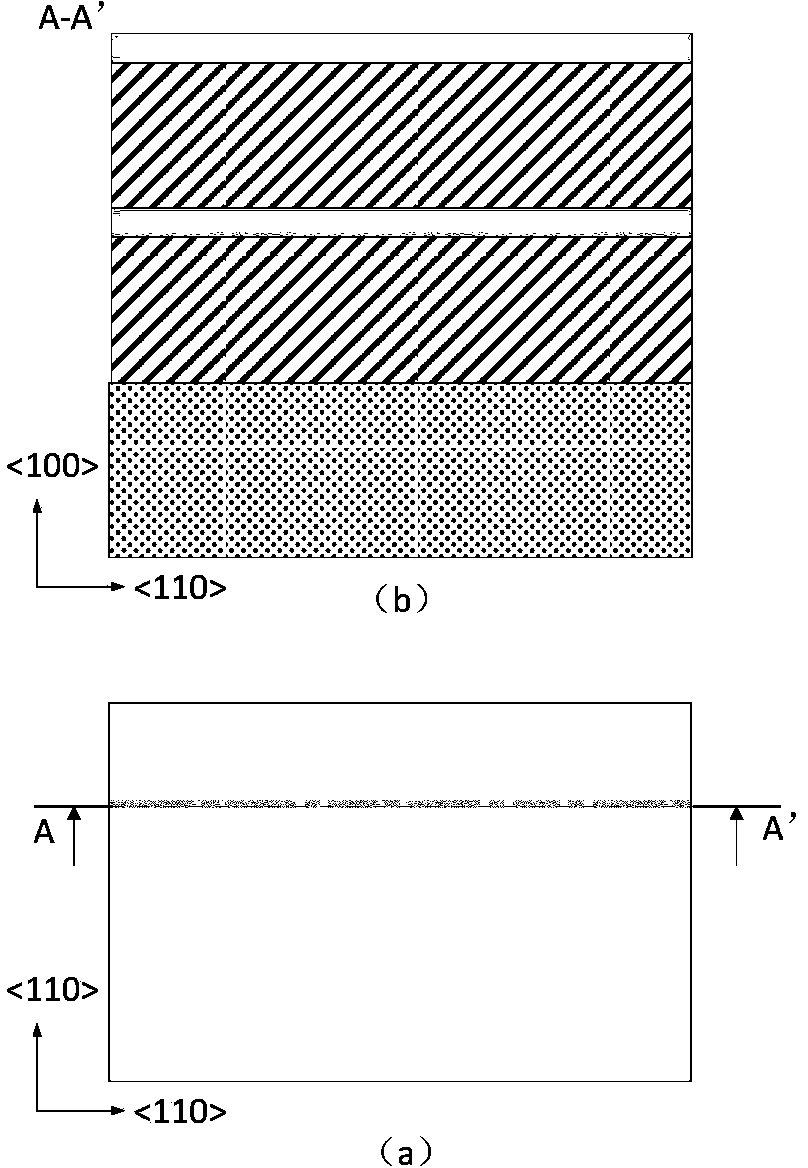

[0067] 4) ALD Si 3 N 4 As a corrosion mask, such as figure 1 shown;

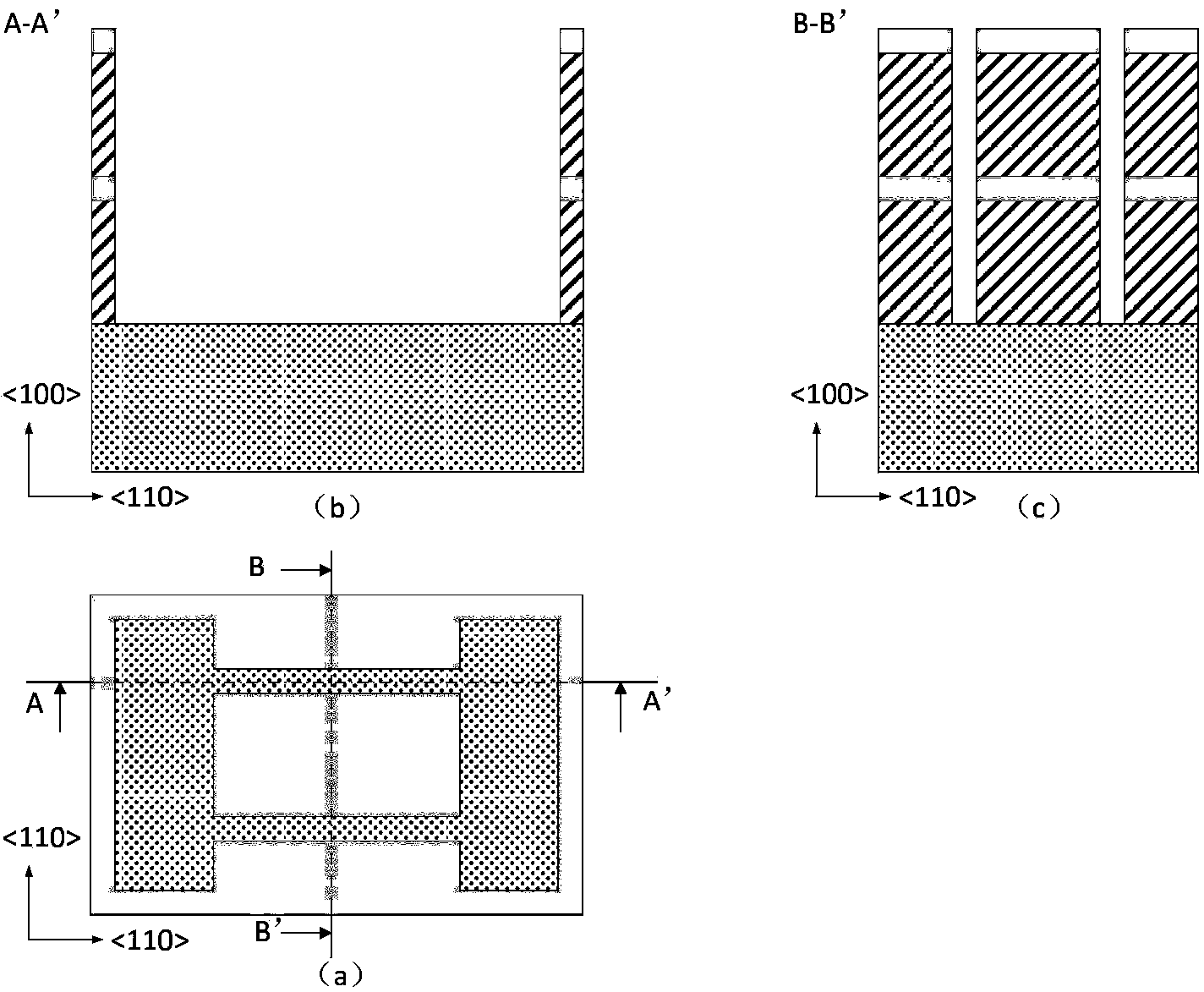

[0068] 5) Electron beam lithography defines the epitaxial windows of Fin and the source and drain regions, in which the width of the Fin structure is 20nm, the length is 300nm, and the length direction and the sidewall crystal direction are both along ;

[0069] 6) Anisotropically etching the stacked structure of the sacrificial layer-masking layer, transferring the pattern defined by photolithography to the stacked structure, exposing the silicon substrate;

[0070] 7) Remove photoresist, such as figure 2 shown;

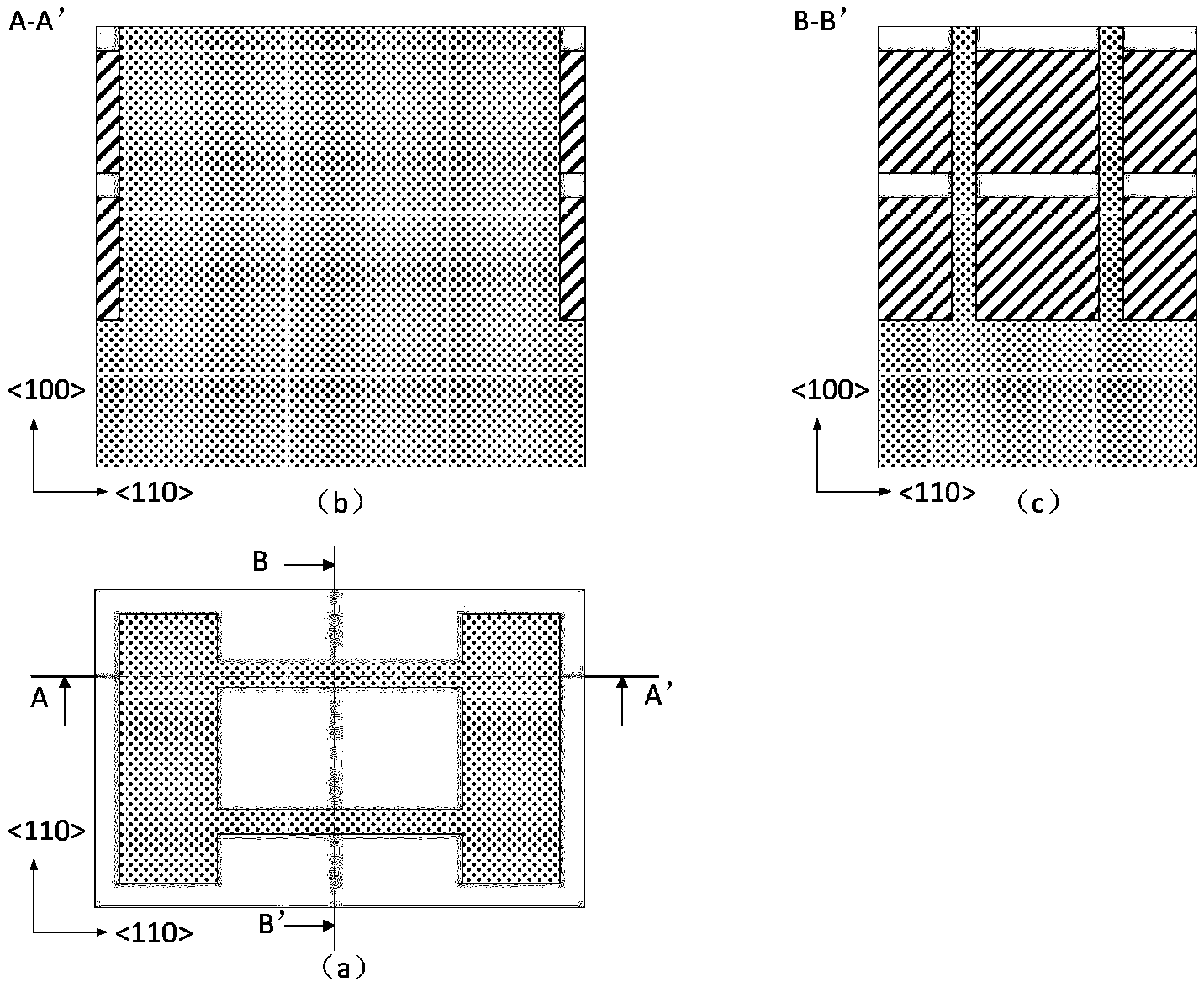

[0071] 8) Selective epitaxy silicon;

[0072] 9) Chemical mechanical polishing remove...

Embodiment 2

[0083] A three-layer nanowire structure with a diameter of about 10 nm was prepared.

[0084] With embodiment 1, difference is:

[0085] a) Select (110) SOI substrate;

[0086] b) Steps 1)-4), the sacrificial layer is made of ICPECVD Polycrystalline germanium, the mask layer is made of ICPECVD SiO 2 ;

[0087] c) After step 4), execute 4.1): ICPECVD Polycrystalline germanium as sacrificial layer; 4.2): ICPECVD deposition SiO 2 as a corrosion mask;

[0088] d) In step 5, 193nm immersion lithography is used to define the epitaxial windows of Fin and the source and drain regions, wherein the width of the Fin structure is 30 nanometers, the length is 300 nanometers, the length direction is along the crystal direction, and the sidewall is along the crystal orientation;

[0089] e) Step 8) Selective epitaxy silicon;

[0090] f) Step 10) using ICPECVD SiO 2 as the top masking layer;

[0091] g) Step 11) uses 193nm immersion lithography to define the etch window fo...

PUM

| Property | Measurement | Unit |

|---|---|---|

| diameter | aaaaa | aaaaa |

| length | aaaaa | aaaaa |

| diameter | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More