Transistor and formation method thereof

A transistor and semiconductor technology, applied in semiconductor devices, semiconductor/solid-state device manufacturing, electrical components, etc., can solve the problems of reduced transistor operating voltage, large transistor power consumption, unfavorable system integration, etc., to achieve stable threshold voltage, good quality, The effect of improving device performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

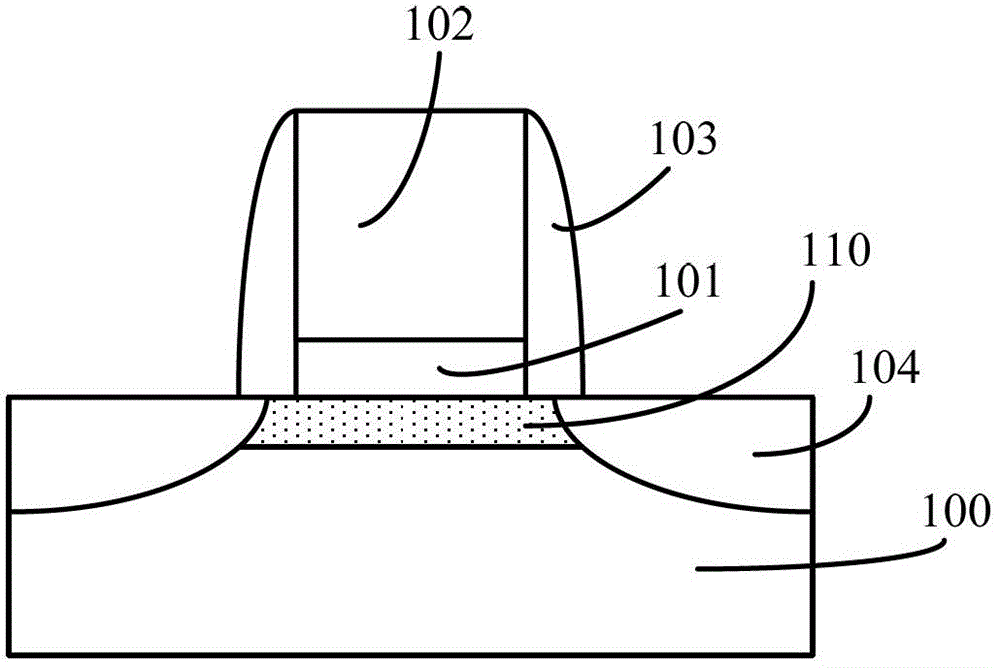

[0033] As mentioned in the background art, although the feature size of the transistor is continuously reduced, the operating voltage of the transistor cannot be reduced accordingly, resulting in excessive power consumption of the transistor.

[0034] The inventors of the present invention have found through research that, as the feature size of the transistor shrinks, the size of the channel region of the transistor also decreases accordingly, making the dopant ions in the channel region more sensitive to the influence of the threshold voltage. Specifically, the dopant ions in the channel region can produce random dopant disturbance (RDF, Random Dopant Fluctuations) effect, and the random dopant disturbance effect will produce a threshold voltage deviation σV T , and the threshold voltage deviation σV T The value of increases as the size of the channel region decreases. The threshold voltage deviation σV TThe turn-on voltage of different transistors will be different. In or...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More