Process deviation tolerating and reading interference eliminating reading amplifying circuit

A technology for read interference and process deviation, applied in the field of read amplifying circuits, can solve the problems of increasing the input offset of the read circuit, affecting the read reliability performance, and reducing the STT-MRAM read decision margin.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0058] The substantive features of the present invention are further described with reference to the accompanying drawings. Embodiments disclosed herein, specific structural and functional details thereof are for the purpose of describing specific embodiments only, therefore, the present invention may be embodied in many alternative forms and the present invention should not be construed as limited only to the embodiments described herein. Instead, this presents example embodiments to cover all changes, equivalents, and alternatives falling within the scope of the invention. Additionally, well-known elements, devices and subcircuits of the invention will not be described in detail or will be omitted so as not to obscure the relevant details of the embodiments of the invention.

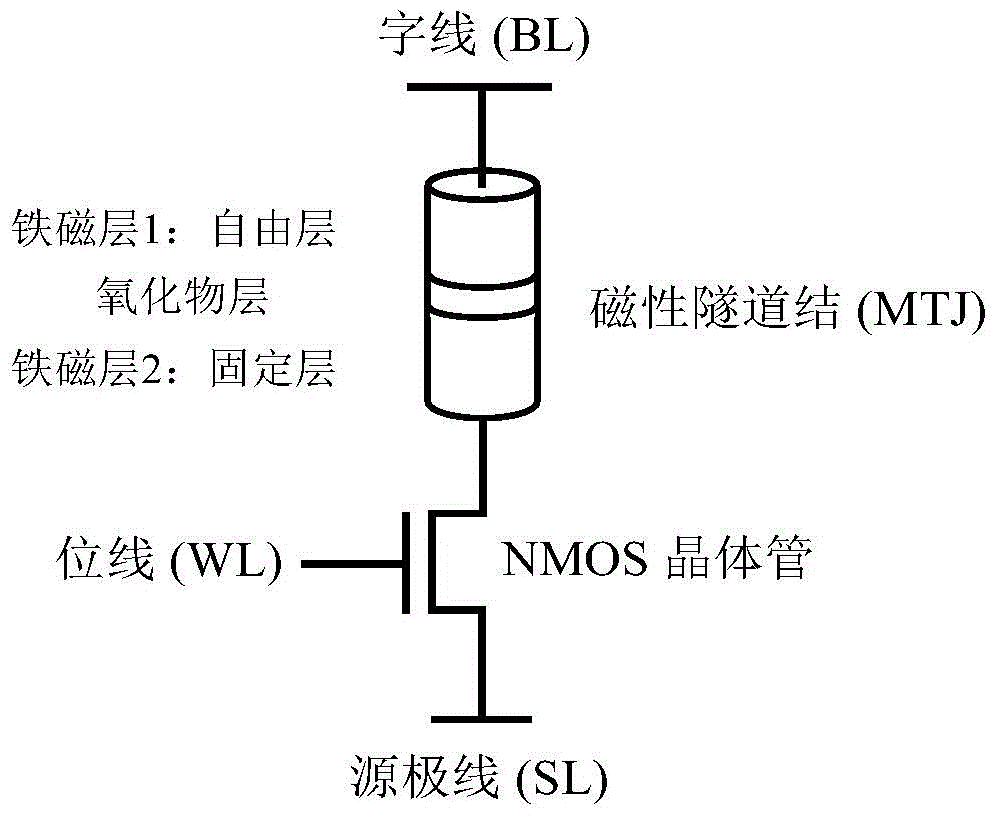

[0059] figure 1 It is a structural schematic diagram of an STT-MRAM memory cell using the reading circuit of the present invention.

[0060] The STT-MRAM memory cell consists of a magnetic tunnel jun...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More