Radio frequency transverse double-diffusion field effect transistor and manufacturing method thereof

A field-effect transistor and lateral double-diffusion technology, which is applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve problems that affect the robustness of device hot carrier injection capabilities and affect the service life of devices, and achieve Improved hot carrier injection capability and reduced output capacitance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0042] A method for manufacturing a radio-frequency lateral double-diffused field-effect transistor, comprising the following steps:

[0043] 1. grow lightly doped P-type epitaxial layer 102 on heavily doped P-type substrate 101, as figure 2 shown;

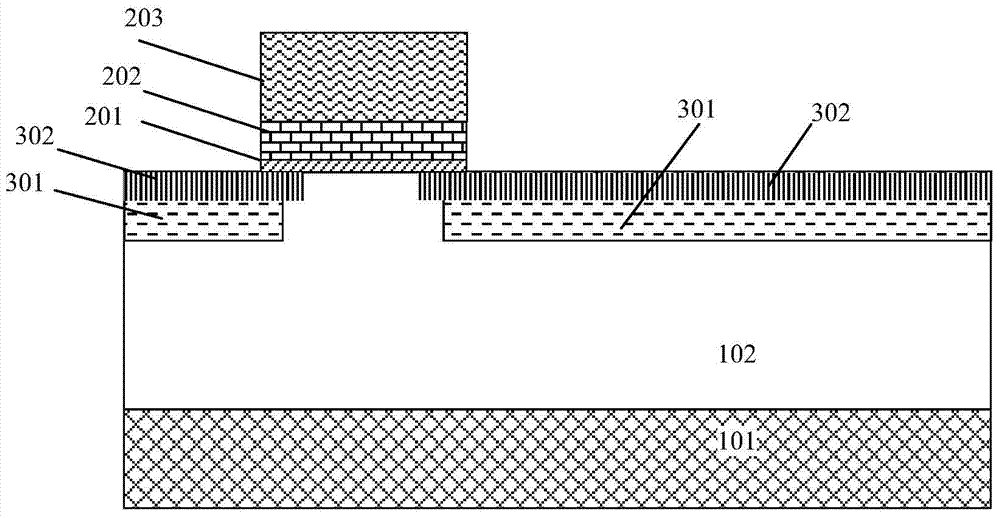

[0044] 2. An oxide layer 201 is thermally oxidized and grown on the P-type epitaxial layer 102, and then a layer of polysilicon 202 is deposited, and the polysilicon gate is photoetched in the middle;

[0045] 3. Keep the photoresist 203 above the polysilicon gate, and perform the first N-type ion implantation 301, the first N-type ion implantation is a self-aligned vertical implantation;

[0046] 4. Keep the photoresist 203 above the polysilicon gate, and perform the second N-type ion implantation 302. The second N-type ion implantation is a self-aligned oblique angle implantation, and the second N-type ion implantation depth is deeper than the first N-type ion implantation. Type ion implantation depth is shallow, such as im...

Embodiment 2

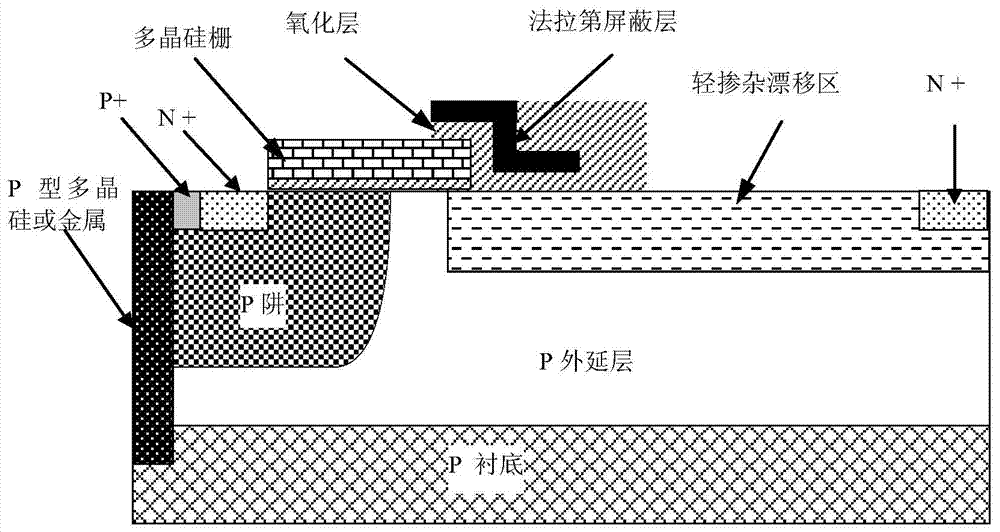

[0063] RF lateral double-diffused field-effect transistors, such as Figure 5 As shown, a P-type epitaxial layer 102 is grown on a P-type substrate 101, and a gate oxide 201 and a polysilicon gate 202 are sequentially formed above the middle of the P-type epitaxial layer 102;

[0064] Form a P well 501 in the P-type epitaxial layer at the lower left of the polysilicon gate 202, and form an N-type drift region in the P-type epitaxial layer at the lower right of the polysilicon gate 202;

[0065] The N-type drift region is divided into a low-depth region, a medium-depth region, and a high-depth region from left to right, the low-depth region is located below the right part of the polysilicon gate, and the high-depth region is a distance away from the right end of the polysilicon gate 202;

[0066] A Faraday shielding oxide layer and a Faraday shielding metal layer are formed on the right part of the polysilicon gate 202 and above the left part of the N-type drift region;

[006...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More