Low-power-consumption real-time noise-reduction and sharpening merged preprocessing algorithm for CMOS image sensor

An image sensor and low-power technology, applied in the field of low-power real-time noise reduction and sharpening preprocessing algorithm, can solve the problems of unfavorable saving of hardware resources, overall power consumption, and high algorithm complexity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

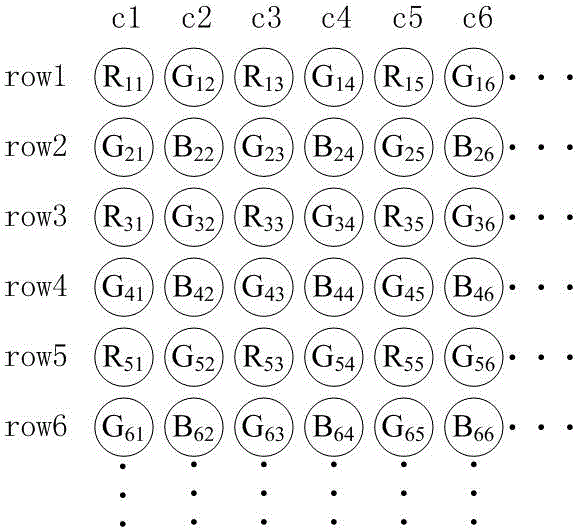

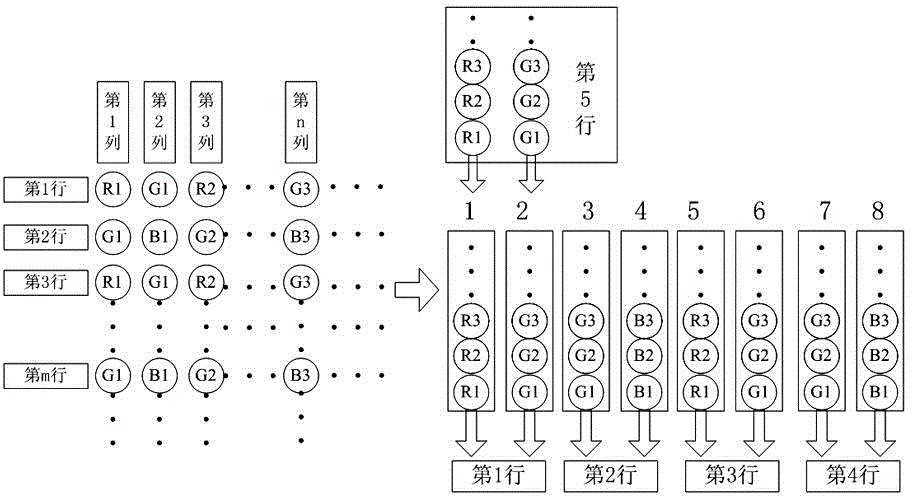

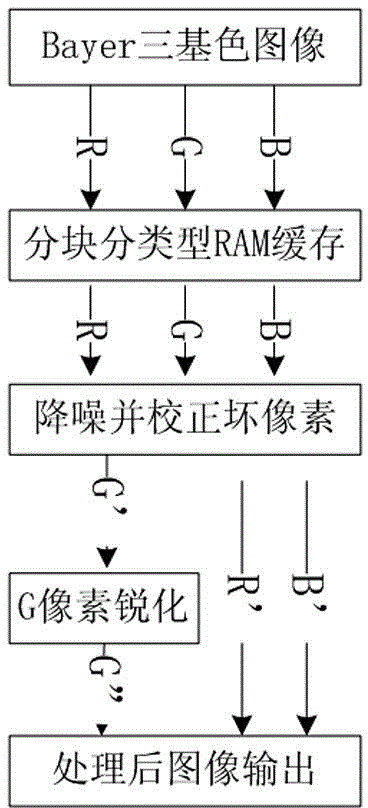

[0050] attached figure 1 is the Bayer model diagram of the color filter array CFA image, with figure 2 It is a schematic diagram of the process of loading Bayer data into half-depth memory. As can be seen from the figure, the low power consumption real-time noise reduction sharpening preprocessing algorithm combined with the CMOS image sensor of the present invention adopts the color filter array CFA to divide the input optical signal into the three primary colors of red, green and blue RGB, that is, RGB three kinds of pixels; The method of accessing data by block and type is used for data caching, the spatial adaptive noise reduction algorithm is used to reduce the noise of RGB pixels, and a new operator template is generated by combining the Laplacian operator and the smoothing operator G pixels for sharpening.

[0051] The method of accessing data by block and type on the chip is used for data caching, including storing and reading the RG or GB row data of Bayer data res...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More