A multi-port memory access controller for multi-processor and its control method

A multi-processor, multi-port technology, applied in electrical digital data processing, instruments, and various digital computer combinations, etc., can solve problems such as reducing the throughput rate of memory access data, achieve full utilization of real-time performance, improve throughput rate, memory The effect of full utilization of bandwidth

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

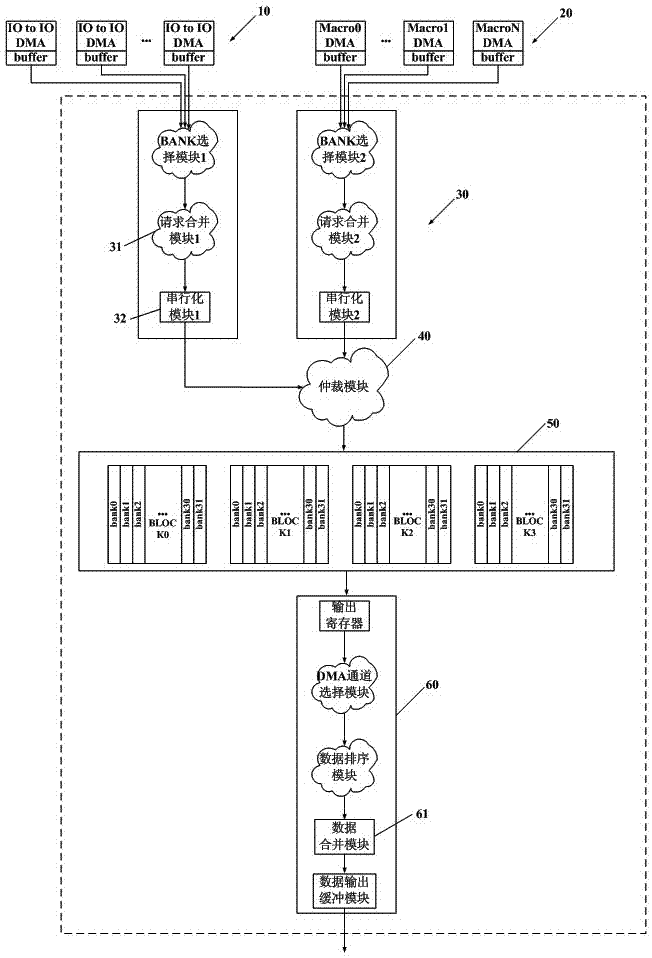

[0021] A multi-port memory access controller for multiprocessors, including an instruction channel 30, its input end is connected with the output end of the peripheral DMA channel 10 and the core DMA channel 20 of the multiprocessor respectively, and its output end is connected with the arbitration module 40 is connected to the input, the output of the arbitration module 40 is connected to the input of the memory array 50, the output of the memory array 50 is connected to the input of the data channel 60, and the output of the data channel 60 is respectively connected to the peripherals of the multiprocessor The input terminals of DMA channel 10 and kernel DMA channel 20 are connected, such as figure 1 shown. The instruction channel 30 is used to connect the multi-channel DMA request interface, and for each memory BANK serialized read and write requests, there is such a group of logic for each memory BANK; the arbitration logic module is used to determine the arbitration resul...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com