A kind of preparation method for the copper substrate of vertical structure led chip

An LED chip, vertical structure technology, applied in electrical components, circuits, semiconductor devices, etc., can solve the problems of high cost, complicated preliminary preparation, hindering the industrialization of vertical structure LED development, etc., to improve the yield and overcome a large number of copper adhesion. , the effect of low cost of preparation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

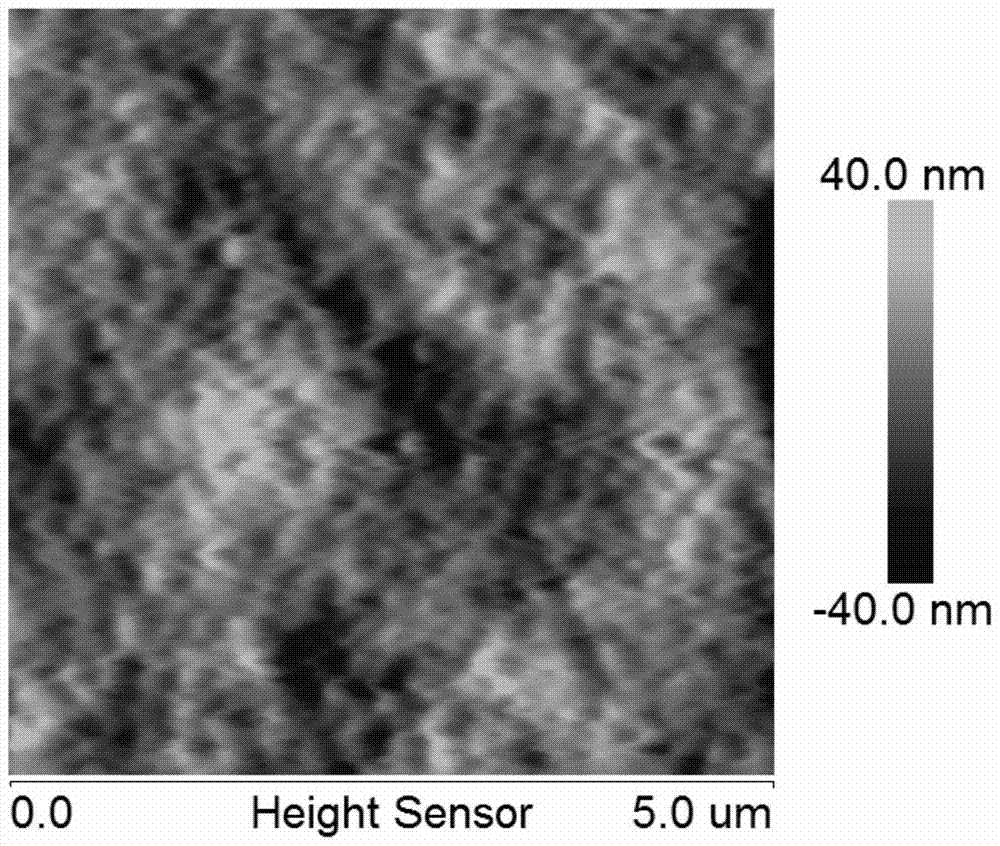

[0036] The method for preparing a copper substrate for a vertical LED chip of this embodiment includes the following steps:

[0037] The method for preparing a copper substrate for a vertical structure LED chip is characterized in that it comprises the following steps:

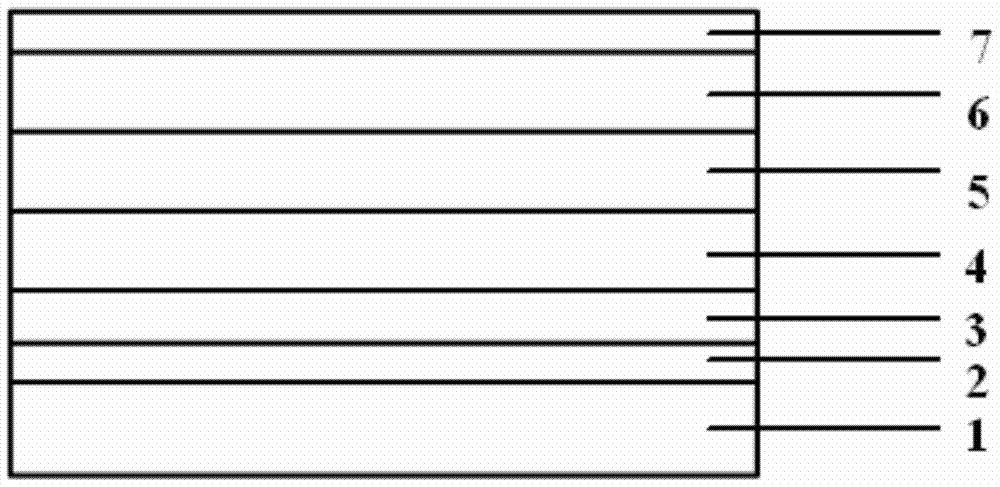

[0038] 1) A layer of P-type metal electrode layer is vapor-deposited on the surface of the GaN epitaxial wafer, the metal in the P-type metal electrode layer is Cr or Pt, and another layer is plated on the P-type metal electrode layer by photolithography or evaporation technology. Layer Au to obtain a first substrate; the thickness of the Cr or Pt is both 30-50 nm, and the thickness of the Au is 800-1000 nm.

[0039] 2) Clean the first substrate, and after the degreasing effect is achieved, use 10% H 2 SO 4 Carry out surface activation for 1 min; the specific cleaning process is 1.5, 1.5, and 1 min cleaning with acetone, ethanol, and deionized water, respectively.

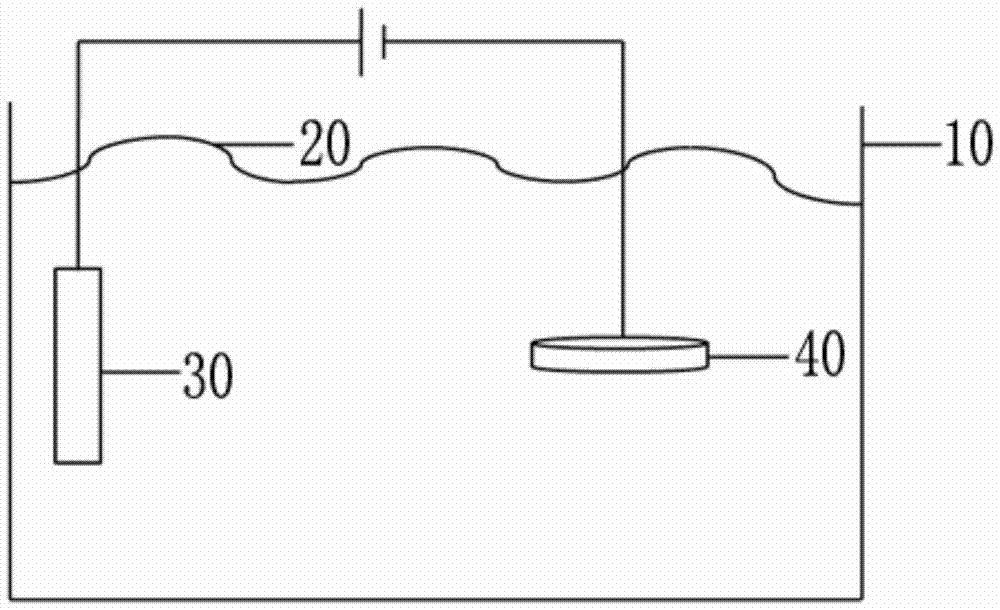

[0040] 3) Blackening the phosphorous copper anode co...

Embodiment 2

[0051] The method for preparing a copper substrate for a vertical LED chip according to this embodiment includes the following steps:

[0052] 1) A layer of P-type metal electrode layer is vapor-deposited on the surface of the GaN epitaxial wafer, and the metal in the P-type metal electrode layer is Cr or Pt, and another layer is plated on the P-type metal electrode layer by photolithography or vapor deposition technology. Layer Au to obtain a first substrate; the thickness of the Cr or Pt is 30 nm, and the thickness of the Au is 1000 nm.

[0053] 2) Clean the first substrate, and after the degreasing effect is achieved, use 10% H 2 SO 4 Perform surface activation for 1 min; the specific cleaning process is 1.5, 1.5, and 1 min with acetone, ethanol, and deionized water, respectively.

[0054] 3) Blackening the phosphorous copper anode containing 0.04wt% phosphorous for 3h and then cleaning; the cleaning solution used in the cleaning process is changed from the molar ratio of 1:5 (NH ...

Embodiment 3

[0062] The method for preparing a copper substrate for a vertical LED chip according to this embodiment includes the following steps:

[0063] 1) A layer of P-type metal electrode layer is vapor-deposited on the surface of the GaN epitaxial wafer, and the metal in the P-type metal electrode layer is Cr or Pt, and another layer is plated on the P-type metal electrode layer by photolithography or vapor deposition technology. Layer Au to obtain a first substrate; the thickness of the Cr or Pt is both 50 nm, and the thickness of the Au is 900 nm.

[0064] 2) Clean the first substrate, and after the degreasing effect is achieved, use 10% H 2 SO 4 Perform surface activation for 1 min; the specific cleaning process is 1.5, 1.5, and 1 min with acetone, ethanol, and deionized water, respectively.

[0065] 3) Blackening the phosphorous copper anode containing 0.065wt% phosphorous for 5h, and then cleaning; the cleaning solution used in the cleaning process is changed from the molar ratio of 1:...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More