Transistor forming method

A transistor and dry cleaning technology, which is applied in the direction of semiconductor devices, semiconductor/solid-state device manufacturing, electrical components, etc., can solve the problem of unclean removal of dummy gate 02, etc., and achieve the effect of improving etching effect, good effect, and avoiding pollution

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

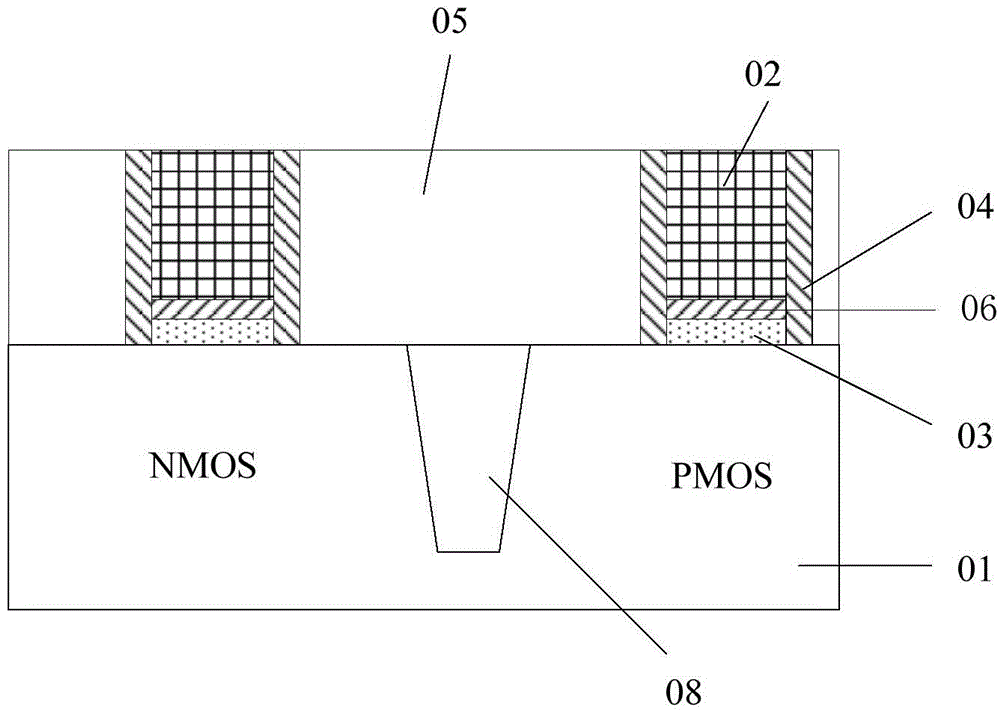

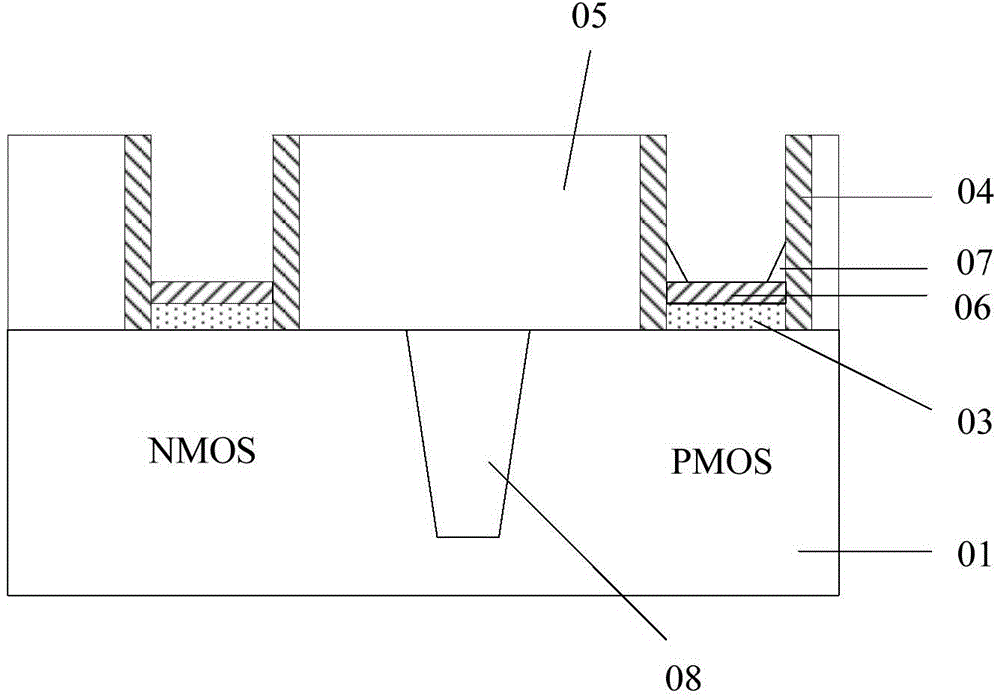

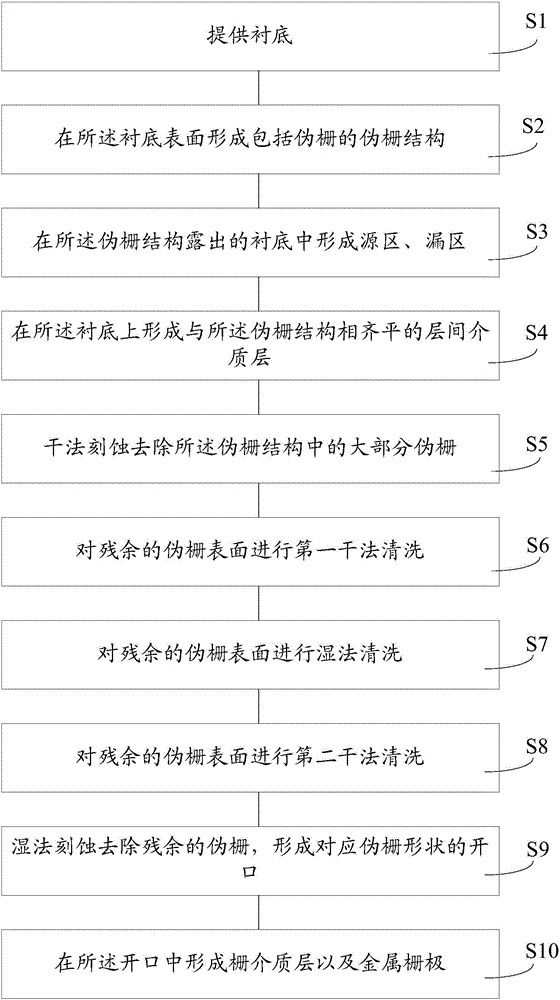

[0034] After dry etching removes most of the dummy gates in the dummy gate structure, pollutants such as particles and organic matter will be produced on the surface of the remaining dummy gates, and polymer particles and oxide layers, etc., will seriously affect the subsequent process. Particles and oxide layer adhere to the surface of the residual dummy gate. Due to the strong selectivity of the subsequent wet etching, the residual dummy gate blocked by polymer particles and oxide layer is difficult to be etched clean, and it is easy to make the final formed Transistors develop defects.

[0035] In order to wet-etch the pseudo-gate dielectric layer with pseudo-gate residues and other pollutants on the surface, the concentration of the etching solution used is high, and the high-concentration etching solution is easy to corrode the interlayer dielectric layer.

[0036] In order to solve the above technical problems, the present invention provides a method for forming a transi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More