Fin field effect transistor and method of forming the same

A fin-type field effect and transistor technology, which is applied in semiconductor devices, semiconductor/solid-state device manufacturing, electrical components, etc., to achieve the effects of avoiding deterioration of isolation effect, improving performance, and controlling etching rate

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

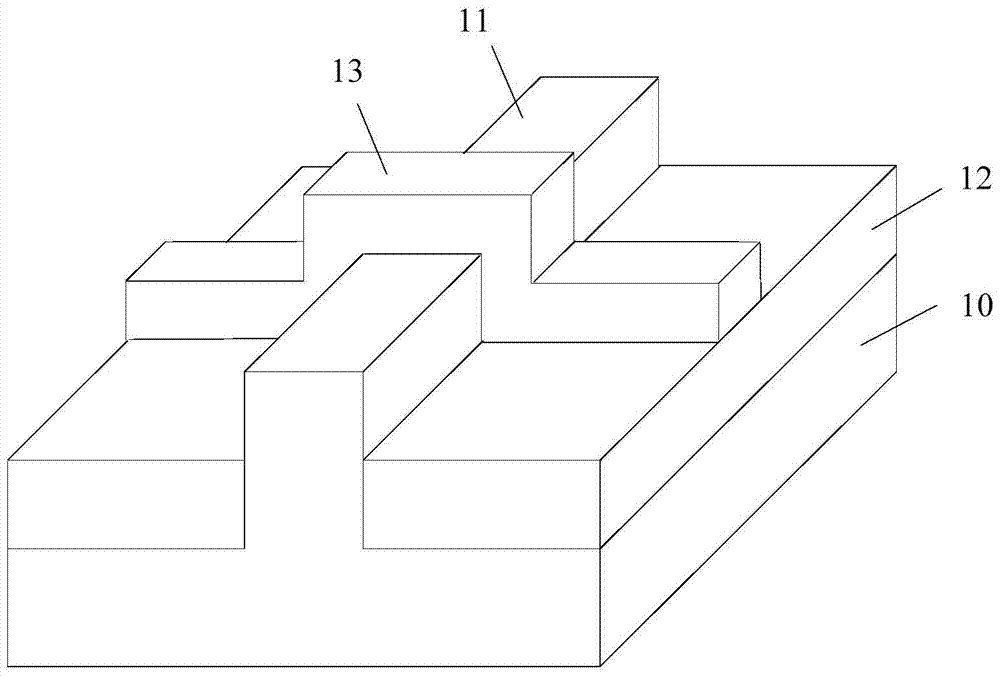

[0031] As mentioned in the background, the carrier mobility of the channel region of the prior art FinFET needs to be further improved, so as to improve the performance of the FinFET.

[0032] Improving the carrier mobility of the channel region of the transistor can be achieved by applying stress to the channel region, for example, applying tensile stress to the channel region of the NMOS transistor can increase the electron flow rate in the channel region of the NMOS transistor. mobility; applying compressive stress to the channel region of the PMOS transistor can increase the mobility of holes in the channel region of the PMOS transistor.

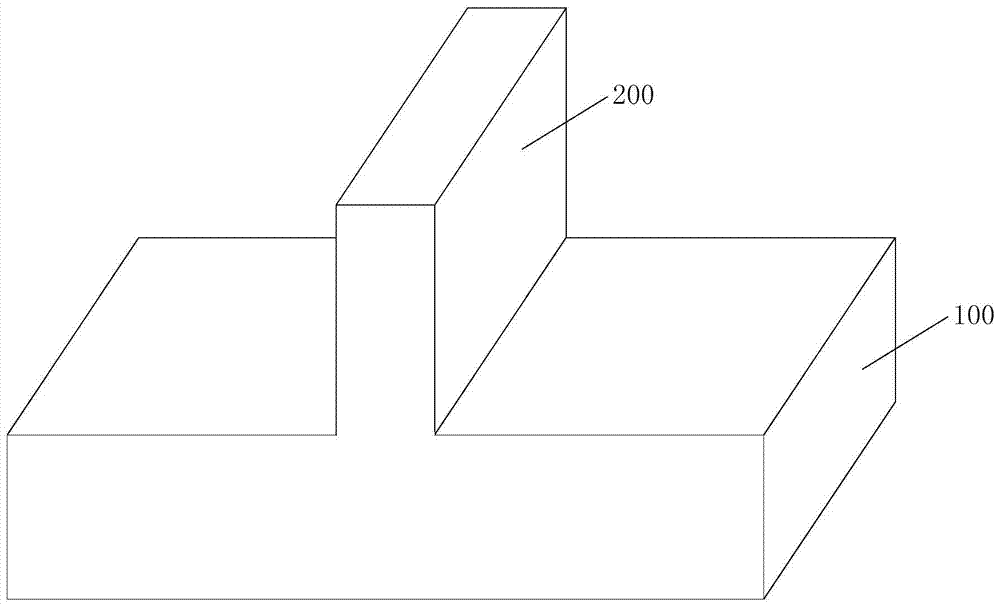

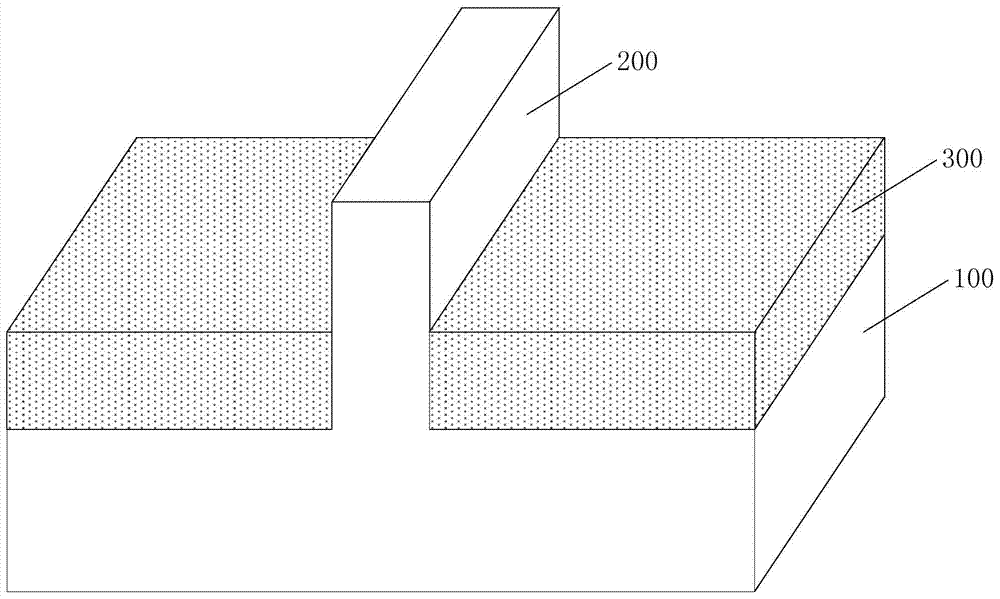

[0033] The channel region of the transistor can be stressed by forming a stressed source and drain. For fin field effect transistors, after removing the fins on both sides of the gate structure by etching, epitaxially form stress materials as source and drain, which requires more process time and cost; The stress layer is epitaxially fo...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More