Method for collaboratively and optimally designing high-speed IC-QFN (integrated circuit-quad flat no-lead) packages

A high-speed, packaged structure technology, applied in semiconductor/solid-state device components, semiconductor devices, electrical components, etc., can solve problems such as physical stress cannot be eliminated

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0021] The high-speed IC-QFN package of the present invention will be further described in detail below in conjunction with the accompanying drawings.

[0022] Firstly, the specific implementation manner of the QFN package described in the present invention is introduced. QFN has excellent high-frequency characteristics. If the price advantage of QFN can be maintained, the three-dimensional packaging of QFN will have a wider range of applications.

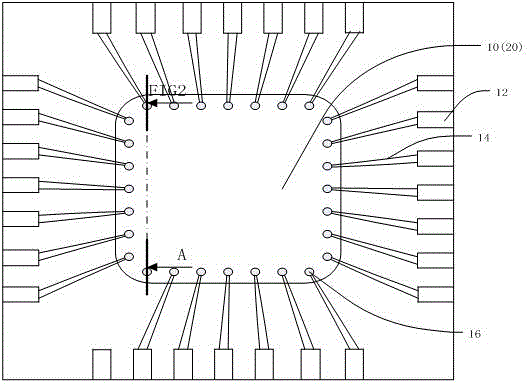

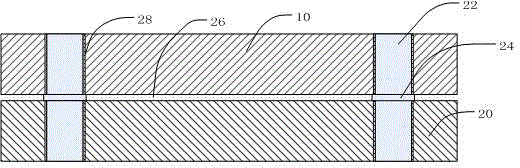

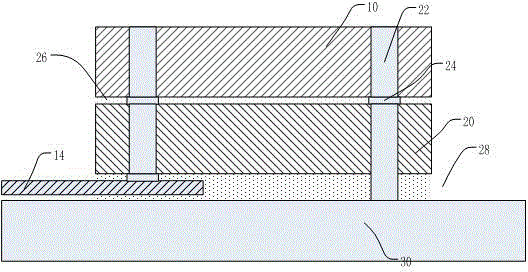

[0023] Such as figure 1 Shown is a schematic diagram of a top view of a QFN three-dimensional package, 10 and 20 are a high-speed IC chip and a control chip respectively, and the two are connected through TSV technology. The bumps of the three-dimensional package and the QFN pads are connected by QFN wiring. Compared with traditional bonding wire gold wires, less parasitics will be introduced and the cost will be reduced.

[0024] For high-speed ICs, any effort to reduce the path to ground will optimize high-frequency performance...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More