Organic light emitting display device and manufacturing method thereof

A light-emitting display and organic technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problem that the contact resistance cannot be effectively reduced, and achieve the effects of improving yield, reducing voltage drop, and large contact area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

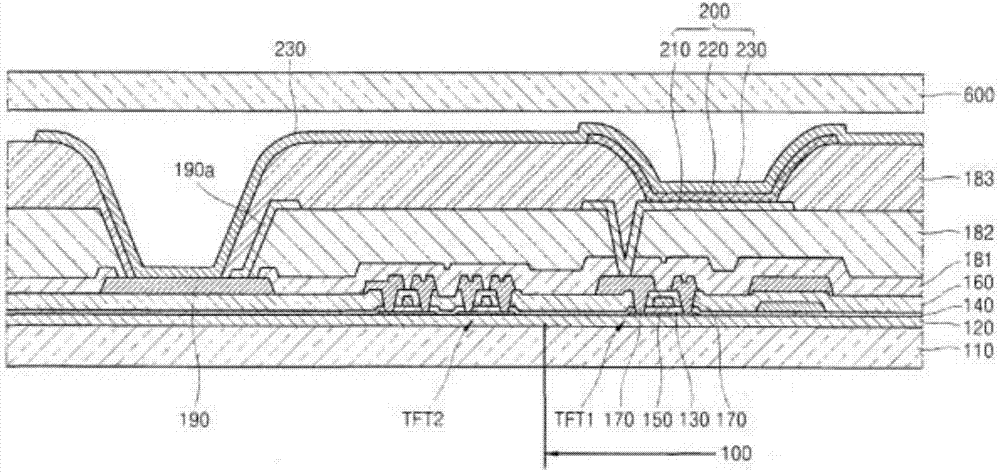

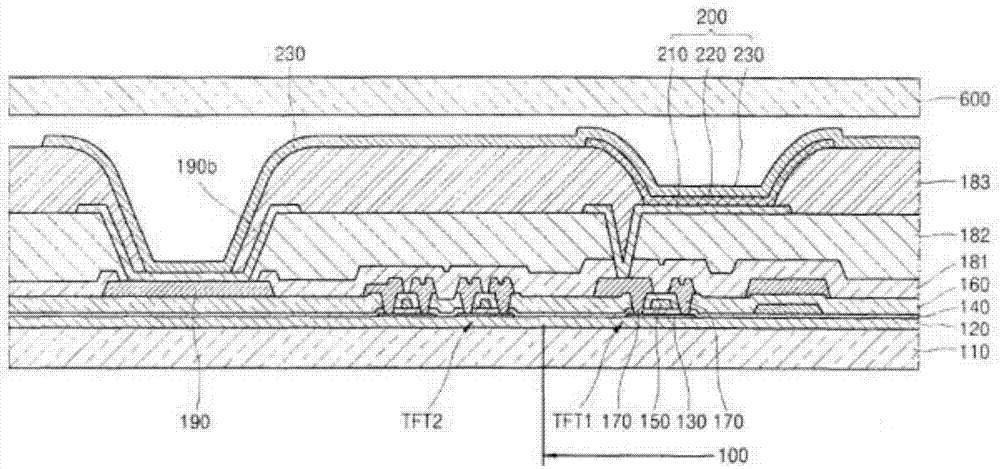

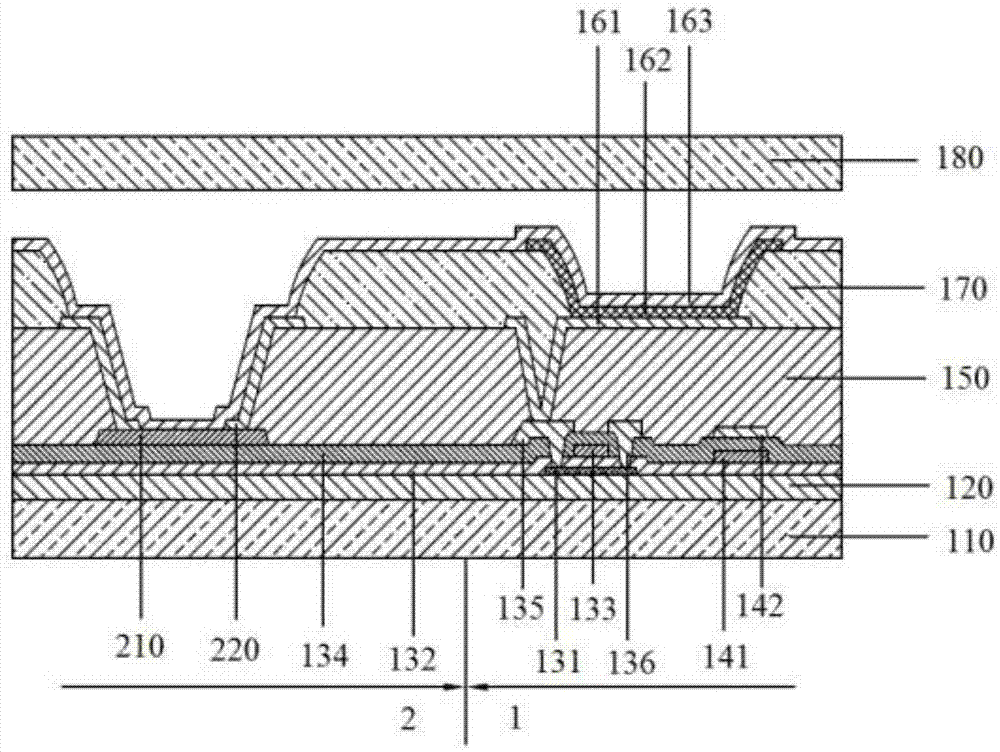

[0043] This embodiment provides an organic light emitting display device, such as image 3 As shown, it includes a substrate 110 , thin film transistors, capacitors and organic light emitting diodes arranged in the display area 1 of the substrate, and electrode power lines 210 arranged in the non-display area 2 of the substrate 110 .

[0044] The substrate 110 is selected from but not limited to a glass substrate or a polymer substrate, and a glass substrate is preferred in this embodiment.

[0045] A buffer layer 120 is directly formed on the substrate 110, and the buffer layer is a layer or multi-layer stacked structure selected from but not limited to silicon oxide and / or silicon nitride, with a thickness of 40-400 nm. A silicon oxide layer is preferred, with a thickness of 230 nm.

[0046] The organic light emitting diode comprises a first electrode 161, an organic light emitting layer 162 and a second electrode 163 stacked in sequence, the first electrode 161 is electric...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More